Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

А. Г. Милехин и А, И. Зверев (72) Авторы изобретения (7I) Заявитель (54) А НАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике.

Известен аналого-цифровой преобразователь, содержащий посждовательно сое I диненные усилители, выходы которых сое5

:бакены с.выходами компараторов Cll.

Недостатком устройства является ниэксе быстродействие.

Известен аналого-цифровой преобразо ватель, содержащий . последовательно сое

10 диненные усилите)ш, каждый из которых содержит два овэрационных уси)в)теля, выходы которых через диоды и резисторы соединены с входами, катоды и аноды дио.дов через резисторы соединены с шинамн источников питания С 21.

1S

Недостатком устройства является низ» кое быстродействие.

Цель изобретения - повышение быст родействия.

Указанная цель достигается тем, что аналого-цифровой преобразователь, содержащий блоки усижтежй по числу разряд» дов, вы))олпе))н ых Ha QB дифференциаль ных уси)ителях и двух резисторах аагруаки, выход каждого предыдущего блока уси усижтелей через резистор связи соединен с. входами каждого последующего, первый выход источника сигнала через резистор соединен с входной шиной первого блока усижтелвй, а второй выход - с общей un ной, в каждый блок усилителей введен ге нератор тока, первый выход котсрого.сое» . динен с входной шиной дажого блока уси)ителей и входами двух дифференциальных усилитетюй, а второй выход - с обшей imr ной, при этом вторые входы двух )ктффе» ренциальных уси)штелей соединены с ши нами источников опорного напряжения, прямой выход первого и инверсный выход второго дифференциальных усиа)теюй че рез первый резистор нагрузки сое)инеййс шиной источника питания, которая через второй резистор нагрузки. соединена с инверсным выходом первого и прямым выходом второго дифференциальных уси)щтеле№, а каждый дифференциальный усиж тель выполнен иа четърех транзисторах и с

92 10 двух дополнительных генераторах тока, причем база первого транзистора соединена с колжктором и базой второго транзистора, база третьего транзистора соединена с коллектором и базой четверто- го транзистора, эмиттеры первого и третьего, второго и четвертого транзисторов попарно обьединены и через соответствующие дополнительные генераторы тока соединены с шиной источника смеще- 10 нияе

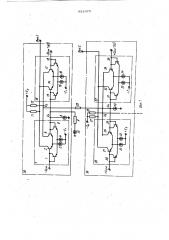

На фиг- 1 гриведена структурная электрическая схема устройства, на фиг, 2временные диаграммы.

Устройство содержит транзисторы l, 15

2, генераторы 3, 4 тока, транзисторы 5, 6, образующие мфференциальный усилитель 7, генератор 8 тока, резисторы 9, источник 10 сигнала, резисторы 11 и 12 нагрузки,:транзисторы 13 и 14, генера- щ торы 15 и 16 тока, транзисторы 17 и

18, образующие дифференциальный усилитель 19. Следующий усилитель состоит иэ транзисторов 20 и 21, генераторов

22 и 23 тока, транзисторов 24 и 25, 2$ образующих дифференциальный усилитель

26, резисторы 27 и 28 нагрузок, резистор 29 связи, генератор 30 тока, транзисторы 31, 32, генераторы 33, 34 тока, транзисторы 35, 36 образуют диф- 3О ференциальный усилитель 37, дифференциальные усилители 7, 19 и 26, 37 образуют блоки 38 усилителей . Дифференциальные усилители 7 и 19 выпоюяены на транзисторах с < -р-и ссттррууккттуурроойй, а

3S дифференциальные усилители 26 и 37на транзисторах р -n-р структуры. Поэтому полярность напряжений питания этих каскадов противоположная. Каждая последующая пара дифференциальных усигмтелей должна состоять иэ трвнзистоФ ров с проводимостью, противоположной по сравнению с транзисторами предыдущей пары. Это вызвано несоответствием уровней постоянных составляющих напряжений 1 на входе и выходе дифференциального усилителя. Для точной установки необходимых уровней постоянных напряжений на сигнальных входах дифференциальных усилителей включены генераторы 8, 30. Напряжение с вых. 1 поступает на компаратор для фзрмирования е -го разряда

АОП, а с вых. 2 — для формирования (+1)-го разряда.

При подаче на вход обычного дифференциального усилителя линейно-изменяющегося напряжения выходной ток, а следовательно и напряжение, не будет ли75 4 нейной функцией входного напряжения, так квк коллекторный ток является экспо ненциальной функцией напряжения на эмиттерном переходе транзистора (при малых значениях этого напряжения). Однако если входное напряжение изменяется не линейно, а по закону логарифма, то нелинейность проходной характеристики транзистора может быть скомпенси-рована, вследствие чего в схеме устройства применено диопное включение транзисторов 1, 6,. 13, 18, 20, 25, 31, 36 и т.д. Напряжение на диоде описывается логарифмической функцией проходящего через него. тока. Поэтому между входными и выходными токами существует линейная зависимость. Источником сигнала в данном устройстве должен быть источник тока. При использовании в качестве источника сигнала источника ЭДС необходимы дополнительные резисторы, служащие эквивалнтом внутреннего сопротивления источника тока. Эту функцию выполняют резисторы 9, 29 и т.д.

Внутреннее сопротивление источника сигнала .и входное сопротивление дифференцивльных усилителей образуют делительь напряжения, в результате чего амплитуда напряжения сигпала на входе дифференциального усилителя меньше напряжения источника входного сигнала. Кроме того, эа счет базовых токов транзисторов 5, 6, 13 и 14 протекающих через резистор 9; напряжение сигнала на базах этих транзисторов имеет постоянное смещение уровня относительно нвпряжения источника сигнала. Линейно изменяющийся ток источника сигнала, проходящий через транзисторы 1, 6, 13 и 18, создает логарифмически-изменяющееся напряжение, которое является управляющим напряжением для транзисторов 2,5,14,17.

Предположим, что в начальный момент времени (фиг. 2б) напряжение на базах транзисторов 5, 6, 13, 14 равно нулю.

Если при этом напряжение на базах транзисторов 1„2 по модулю больше нуля, то в исходном состоянии транзисторы 1, 2, 17 и 18 закрыты, а транзисторы 5, 6, l3 и 14 открыты и их ток коллектора определяется величиной тока генераторов

3,4, 15 и 16. По мере увеличения отрицательного напряжения на входе устройсгва (фиг. 2б) токи генераторов тока начинают перераспределяться так, что токи через транзисторы 5, 6 уменьшаютс я, а через транзисторы 1, 2 увеличиваются. В момент времени tg, когда нвпржкение, токи между транзисторами 2 и

A2107""» разрядов, выполненных на двух дпфферен» циальных усилителях и двух резисторах на гузки, выход каждого предыдущего блока уси ытелей через резистор связи соединен с входами каждого посждуюшего, первый выход источника сигнала че» рез резистор соединен с входной шиной первого блока усилитежй, а второй вход5, 1 и 6 распределяются поровну. При дальне йшем увеличении отрицательного напряжения Vg. перераспределения токов продолжаются до тех пор, пска напряже ние Vg не превысит по абсолютной se- s личине напряжения Ч . Это соответству ет моменту времени +g. Весь ток генераторов 3 и. 4 проходит при этом только через транзисторы . н 2. Распредежние с обшей шиной, о т л и ч а ю ш и и с я токов в дифференциальном усклителе 19 10 тем, что, с целью повышения быстродейдо момента 4 = tg остается неизменным, ствия, экономичности и надежности, в каждый блок усижтелей введен генератор если к этому времени напряжение Yg лители соединены друг с другом своими ходом второго дифференциальных усилиразиополярными выходами (прямой выход одного - с инверсным выходом другого и наоборот), изменение токов обоих 2. Преобразователь по п. 1, о т л икаскадов в обшей нагрузке (резисторы ЗО ч а ю ш и и с я тем, что каждый диффе11 и 12) имеют взаимно противополо i ренциальный усилитель выполнен на четыжный характер, а выходное напряжение рех транзисторах и двух дополнительных с учетом разделения работы дифферент «генераторах тока, причем база первого альных усилитежй по времени имеет транзистора соединена с коллектором и вид, приведенный на фиг. 2в. З базой второго транзистора, база третье

Работа дифференциальных каскадов 26 го транзистора соединена с колжктором и 37 аналогична . Работе дифференциальных и базой ченюртого транзистора, эмитте каскадов 7 и 19. ры первого и третьего, второго и чет»

Коэффициент усиления па напряжению,вертого транзисторов попарно обьедипены каждого дифференциального Усилителя ра- 4tr и через соотвеФстцуюшие дополнительныа вен 2, вследствие чего крутизна линей о- генераторы тока соединены с шиной исизменяюшегося напряжения на выходе ка- тощцкка смещения. ждой последующей пары каскадов вдвое больше, чем на выходе предыдущей Hctочники информации, (фиг. 2д). Это приво ат к тому, что 4$ принятые во внимание при экспертизе сворачивание" напряжения во времени на выходах дифференциальных каскадов 1. Смолов В, Б. и др. Микроэжкт происходит вдвое быстрее, чем на их . роиные цифро-аналоговые и аналого-цифвходах. ровые преобразователи информации

Ф ор мула и зобре тени я . «Энергия 1976, с. 32 324.

l. Аналого-цифровой преобразователь, 2. Ощтсание прибора DL 305 фирмы содержащий блоки усилитежй по числу hrctrtSt&rtt 99urd 1977 f ïðoòoòttïI. меньше напряжения смешения (Y +Я. тока, первый выход которого соединен с

Поэтому изменение выходного напряжения входной шиной данного блока усилитежй дифференциальных усилитежй 7 и 19 до is H выходами двух дифференциальных ycHmrвремени t. = t определяется перераспре- тежй, а второй выход- с обшей шиной, дежнием тока генератора 3 между трэн- rtpH oM sTopbte входы двух t!H peH» зисторами 2 и 5. В свою очередь,изме- циальных усилителей соединены с шинами йение выходного напряжения за время источников опорного напряжения, прямой -,, определяется только перераспре» 20 выход первого и инверсный выход второделением тока юнератора 16 между тран- го дифференциальных усилитежй через зисторами 14 и 17, характер измене первый Резистор нагрузки соединены с ния которого аналогичен перераспредеж- диной источника питания, которая через нию тока в дифференциальном усилителе ° втоРой Резистор, нагрузки соещщена с щ1

-4

7. Ввиду того, что дифференциальные уси-23 версным выходом первого и йрямым выА21 075

-Ьм л

Составитель А. Титов

Редактор С. Запесочный Техред М.Гергель Корректор В. Бутяга

Заказ 2380/74 Тираж 954 Подписное

BHHHIIH Государственного комитага СССР по делам изобретений и открытий

113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул Проектная, 4