Стробируемый делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

АНИЕ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву.— (22) Заявлено 02.07.80 (21) 2949369/18-2 1 (51) М. Ка. с присоединением заявки №вЂ”

Н 03 К 23/00

Гасударственный комитет (23) Приоритет—

Опубликовано 15.04.82. Бюллетень №14 ло делан изобретений и открмтий (53) УДК 621.374.4(088.8)

Дата опубликования описания 25.04.82

Ър""

А. M. Гамбург, Е. К. Иосипов, М. A. Солоха и Л. Pl. Фельдман,.„. : *:! (72) Авторы изобретения (7l) Заявитель

«4«««". ь«, ю„, ««=„, (54) СТРОБИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике.

Известен делитель частоты с привязкой сигналов к задающей частоте, содержащий последовательно соединенные триггеры со счетным входом, логический элемент И вЂ” НЕ, элемент ИЛИ вЂ” НЕ, дополнительный триггер и дополнительный элемент И вЂ” НЕ, выход которого соединен с одним входом элемента ИЛИ вЂ” НЕ, второй вход которого подключен к выходу основного элемента И вЂ” НЕ (1) .

Данный делитель не обеспечивает достаточной точности деления.

Наиболее близким по технической сущности к изобретению является делитель час- тоты, содержащий последовательно включенные каскады деления, логические цепи, причем на входы каскадов. деления поданы стробирующие сигналы (2), Данный делитель не обеспечивает достаточной точности временных привязок за счет нестабильности задержки выходных импульсов по отношению к стробирующему.

Целью изобретения является уменьшение нестабильности задержки выходных импульсов по отношению к стробирующему .

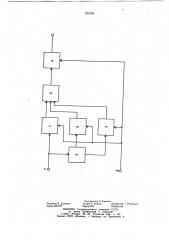

Поставленная цель достигается тем, что в стробируемый делитель частоты, содержащий m каскадов деления частоты, вход первого из которых соединен с входной шиной, а входы управления всех каскадов деления частоты соединены с шиной стробирующего сигнала, введены блок задержки и элемент ИЛИ, входы которого соединены с выходами всех каскадов деления частоты кроме последнего, а выход подключен к входу последнего каскада деления частоты, 1О входы всех каскадов деления частоты, кроме первого и последнего, соединены с выходами блока задержки, вход которой соединен с входной шиной.

На чертеже приведена структурная элек15 трическая схема предлагаемого делителя частоты.

Делитель частоты содержит каскады

1 — 4 деления частоты, блок задержки 5, элемент 6 ИЛИ. На входную шину 7 подается входной сигнал, а на шину 8 — стробирующий сигнал.

Принцип работы делителя заключается в следующем.

В исходном состоянии, в момент времени t о работа делителя запрещена низким

921096

4 ления строба относительно входных сигналов через время равное — — Тщ, переключаL з ется один из каскадов деления частоты 1 — 3.

Нестабильность задержки относительно строба сигнала на выходе стробируемого делителя частоты тоже равна — - " —, так как каскад 4 деления переключается сигналом с выхода элемента 6.

При поступлении последующих входййх импульсов работа делителя повторяется аналогично предыдущему.

По окончанию строба по шине 8 в момент времени t 0 стробируемый делитель частоты устанавливается в исходное состояние.

При поступлении очередного строба в момент времени 1н стробируемый делитель частоты функционирует аналогичным образом.

Таким образом, на выходе делителя час-. тоты выходные (поделенные) импульсы выдаются с нестабильностью задержки выходного импульса относительно строба на - -.

При увеличении количества дополнительных каскадов деления до и и соответствующем формировании в блоке задержки входных импульсов, задержанных относительно

25 друг друга на — „- —, величина нестабиль т ности задержки выходного импульса относительно строба равна — — "- —. т

n+!

Формула изобретения

3 (нулевым) потенциалом, поступающим по шине 8 (строб отсутствует). Импульсы на выходе делителя отсутствуют, так как все каскады деления установлены низким потенциалом в нулевое исходное состояние и работа их по делению импульсов запрещена на время отсутствия строба. На шине 7 присутствуют входные импульсы, которые поступают на первый каскад деления 1, не изменяя его состояния, и на блок задержки, который формирует на своих выходах импульсы, задержанные относительно входных импульсов соответственно на 1/3 Твх . и

2/3 Твх, где Твх — период следования входных импульсов. Импульсы с выходов блока задержки соответственно поступают на входы каскадов 2 и 3 деления частоты, не изменяя их состояние.

При поступлении в момент времени по шине 8 строба потенциалом высокого уровня разрешается работа по делению ймпульсов каскадам деления частоты.

Каскады деления частоты срабатывают по переднему фронту положительных импульсов.

Таким образом, в момент времени по импульсу, поступившему по шине 7 в момент времени t<, первый каскад деления не переключается, так как момент времени

t< опережает момент времени tz.

Первым переключается. каскад 2 деления, на вход которого в момент времени

t> поступает с выхода блока задержки импульс, задержанный относительно строба.

Положительный перепад напряжения с выхода каскада 2 деления через элемент 6 поступает на вход второго каскада деления и переключает его. На выходе делителя появляется потенциал высокого уровня. Далее в моменты времени t4 u t z соответственно происходит включение каскада 3 деления и каскада 1 деления, а в моменты времени t6, 17, te соответственно выключе.ние каскадов 1 — 3 деления. На входах элемента 6 и, следовательно, на его выходе в момент времени t устанавливается потенциал низкого уровня.

При поступлении очередного импульса в момент времени t на вход каскада 2 деления вновь на его выходе установится потенциал высокого уровня; который через элемент 6 поступает на каскад 4 деления и переключает его в нулевое состояние.

Таким образом, на выходе элемента 6 формируются положительные импульсы с периодом следования 2 Твх и с нестабильностью задержки относительно строба - -, так как при произвольном моменте поступСтробируемый делитель частоты, содержащий m каскадов деления частоты, вход первого из которых соединен с входной шиной, а входы управления всех каскадов деления частоты соединены с шиной стробирующего сигнала, отличающийся тем, что, с целью уменьшения нестабильности задержки выходных импульсов по отношению к стробирующему, в него введены блок задержки и элемент ИЛИ, входы которого

40 соединены с выходами всех каскадов деления частоты, кроме . последнего, а выход подключен к входу последнего каскада деления частоты, входы всех каскадов деления частоты, кроме первого и последнего, соединены с выходами блока задержки, вход которого соединен с входной шиной.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 445988, кл. Н 03 К 23/02, 05.10.72.

50 2. Проектирование микроэлектронных цифровых устройств. Под ред. Майорова С. А., 1977, с. 146.

921096

Составитель Г. Королев

Корректор Г. Решетник

Тираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4