Устройство для детектирования многочастотных сигналов с двукратной относительной фазовой манипуляцией

Иллюстрации

Показать всеРеферат

<и 921115

Союз Советскии

Социалистических республик

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{61) Дополнительное к авт. сеид-ву < 758558 (22) Заявлено 21. 05. 80 (2! ) 2927539/18-09 (5! )М. Кл.

Н 04 L 27/22 с присоединением заявки М

1ееудлротеенный комитет

СССР пе делан изобретений и открытий (23) Приоритет (53) УД1(621. 39". .62(088.8) Опубликовано 15.04.82. Бюллетень 1те 14

Дата опубликования описания 17.04.82

° °

А. A. Гришуков, В. M. Сильянов и Л. М.1 Рахович (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ МНОГО4АСТОТНЫХ

СИГНАЛОВ С ДВУКРАТНОЙ ОТНОСИТЕЛЬНОЙ

ФАЗОВОЙ МАНИПУЛЯЦИЕЙ

Поставленная цель достигается тем, что в устройство введены инвертор, коммутатор, генератор смещенных частот, формирователь управляющих импульсов, анализаторы зоны расстройки и последовательно соединенные многоканальный компаратор, блок переключения частоты и сумматор, вто15 рой вход и выход которого соединены соответственно с выходом накопителя и управляющим входом перестраиваемого генератора, при этом выход входного преобразователя частоты подключен к

20 входу инвертора, выход которого соединен с первым входом коммутатора, . и к второму входу коммутатора, третий вход и выход которого соединены соИзобретение относится к связи, может использоваться в системах передачи и приема многочастотных сигналов с двукратной относительной фазовой манипуляцией.

По основному авт.св. 11 758558 известно устройство для детектирования многочастотных сигналов с двукратной относительной фазовой манипуляцией, содержащее перестраиваемый генератор, выход которого подключен к опорному входу входного преобразователя частоты, выход которого через последовательно соединенные блок корреляторов, запоминающий блок, сканирующий блок и .блок вычисления разностей фаз подключен к входам блока вы", деления большего и меньшего сигналов, последовательно соединенные блок формирования сигналов расстройки, блок оценки сигналов расстройки и нако" питель (lj .

Однако известное устройство обладает сравнительно невысокой помехоустойчивостью при увеличении частотной расстройки принимаемых сигналов.

Целью изобретения является повышение помехоустойчивости при увеличении частотной расстройки принимаемых . сигналов., 1115 ф

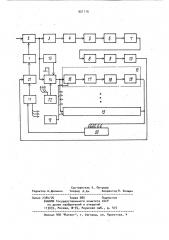

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для детектирования многочастотных сигналов с двукратной относительной.фазовой манипуляцией содержит перестраиваемый генератор 1, вхсдной преобразователь 2 частоты, блок 3 корреляторов, запоминающий блок 4, сканирующий блок 5 блок 6 вычисления разностей фаэ, блок 7 выделения большего и меньшего сигналов, блок .8 формирования сигналов расстройки, блок 9 оценки сигналов расстройки, накопитель 10, блок

l1 переключения частоты; генератор 12 смещенных частот, инвергор 13, коммутатор 14, анализаторы 15 зон расстройки, включающие в себя перемножитель 16, интегратор 17, выпрямитель

18 и накопитель 19, многоканальный компаратор 20, сумматор 21 и формирователь 22 управляющих импульсов.

Устройство работает следующим образом.

Групповой многочастотный сигнал, представляющий собой сумму отрезков гармонических колебаний, модулированных по фазе, поступает через входной преобразователь 2 на блок 3. Вычисленные в блоке 3 проекции сигнала через запоминающий блок 4 и сканирующий блок 5 поступают в блок 6, в котором формируются сигналы, пропорциональные синусам и косинусам разностей фаз соседних посылок. Блок 7 определяет больший и меньший сигналы в каждом из каналов, по которым в

3 92 ответственно с первым выходом формирователя управляющих импульсов. и первыми входами анализаторов эонй расстройки, вторые, третьи и четвертые входы которых соединены соответственно с выходом генератора смещенных частот, вторым выходом формирователя управляющих импульсов и вторым выходом блока переключения час" тоты, а выходы анализаторов зоны расстройки подключены к входам многоканального компаратара, причем анализатор зоны расстройки содержит последовательно соединенные пе" ремножитель, интегратор, выпрямитель и накопитель, выход которого является выходом анализатора зоны расстройки, входами которого являются входы перемножителя и вторые входы интегратора и накопителя. блоке 8 формируются сигналы расстройки частоты. Полученные сигналы анализируютая в блоке 9,и, если они искажены помехой не более некоторого допустимого уровня,-поступают в накопитель lO, в котором формируется единый сигнал"рассогласования, поступающий через сумматор 21 на перестраиваемый генератор 1.

10 Сигнал рассогласования, воздействующий на перестраиваемый генератор

l, является периодическим с периодом равным четверти частоты, манипуляции.

Он равен нулю не только -в отсутствии

1а смещения частоты сигнала в канале связи, но и при смещениях частоты, кратных четверти частоты манипуляций. Для устранения неоднозначности

1 информационный сигнал с,входного щ преобразователя 2 поступает непосредственно и через инвертор !3 на коммутатор 14, с выхода которого он поступает на перемножители 16 анализаторов 15, На вторые входы перемножителей 16 поступают с генератора

12 сигналы с частотами(а ср х ч . Частота Мср является средней частотой группового сигнала и поступает на первый анализатор 15. Величина A < представляет собой частотный разнос между двумя соседними точками,в которых сигнал рассогласования, полученный в накопителе 10, равен нулю, t.e. Ьм равно четверти частоты манипуляции. Число К=0,1... Его максимальное значение зависит от необходимого диапазона компенсируемого смещения частоты и определяет число.. анализаторов зоны расстройки. Коммутатор 14, начиная с момента t=0, до момента,t=ht пропускает сигнал на анализаторы 15. С момента tight до момента й=Т (где Т - длительность.интервала интегрирования сигнала в блоке 3) сигнал от анализаторов 15 отключается. С момента t=T. до момента t--T+dt на анализаторы 15 ин- формационный сигнал поступает через инвертор 13. Коммутатор 14 управляет50 ся от формирователя управляющих импульсов 22.

Интеграторы 17 интегрируют результат перемножения входного сигнала анализаторов 15 и сигналов соответст-. вующих смещенных частот. К концу посылки результаты интегрирования представляют собой разность отсчетов информационного сигнала, сдвинутых на

5 921 время. й=Т. После прохождения через выпрямитель 18 эти разности поступают в накопитель 19. Результаты накопления в анализаторах 15 сравниваются в многоканальном компараторе 20, пос- 5 ле чего по наименьшему иэ них принимается решение о сдвиге частоты, кратном четверти частоты манипуляции. Ре зультат сравнения поступает в блок

11, выходное напряжение которого че- 10 рез сумматор 21 воздействует на перестраиваемый генератор 1. .Сброс интеграторов 17 производится rio командам с формирователя 22, а сброс накопителей 19 - по командам с блока 11.

Предложенное устройство обеспечивает высокую помехоустойчивость при расстройках сигнала, сравнивае-. мых с частотным разносом между ка- zp налами.

Формула изобретения

1. Устройство для детектирования многочастотных сигналов с двукратной относительной фазовой манипуляцией по авт.св. Г" 758558, о т л и ч аю щ е е с я тем, что, с целью ловы-:зо шения помехоустойчивости при увеличении частотной расстройки принимаемых сигналов,.введены инвертор, коммутатор, генератор смещенных частот, формирователь управляющих импульсов, анализаторы зоны расстройки и,последовательно соединенные многоканальный компаратор, блок переключения а

«5 б час тоты, и сумматор, второй вход и выход которого соединены соответственно с выходом накопителя и управляющим входом перестраиваемого генератора, при этом выход входного преобразователя частоты подключен к .входу инвертора, выход которого соединен с первым входом коммутатора, и к второму входу коммутатора, третий вход и выход которого соединены соответственно с первым выходом формирователя управляющих импульсов и первыми входами анализаторов зоны расстройки, вторые„ третьи и четвертые входы которых соединены соответственно с выходом генератора смещенных частот, вторым выходом формирователя управляющих импульсов и вторым выходом блока переключения частоты, а выходы анализаторов зоны расстройки подключены к входам многоканального компаратора.

2. Устройство по.п.1, о т л ич а ю щ е е с я тем, что анализатор зоны расстройки содержит последовательно соединенные перемножитель, интегратор, выпрямитель.и накопитель, выход которого является выходом анализатора зоны расстройки, входами которого являются входы перемножителя и вторые входы интегратора и накопителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 758558, кл. H 04 L 27/22, 1977 (прототип).

Составитель Е. Петрова

Редактор А.Долинич Техред A.Ä÷ КорректорЛ. 6окшан.

Заказ 2384/76 Тираж 685 Подписное

ВНИИПИ Государственнного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППЯ "Патент", г. Ужгород, ул. Проектная, 4