Устройство для умножения электрических сигналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и922784

ИЗОБРЕТЕН ИЯ

CoIo3 Советскнк

Соцкалисткческик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.08.80 (2) ) 2867294/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 23.04.82. Бюллетень Ме 15

Дата опубликования описания 23.04.82 (5I }М. Кл.

9 069 7/164

1Ьвударстоквный комитет

CC CP аа делам изобретений и откоытнй (53} УДК 681.

;335(088. 8) (72) Авторы изобретения

А. Ф. Гришков, А. Н. Гуляев, И. Г. Дорух и А. (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

ЭЛЕКТРИЧЕС К ИХ С И ГНА ЛОВ

Изобретение относится к аналоговой вычислительной технике, Извес тны ус гройства, предназначенные" для умножения электрических сигналов, содержащие усилительные элементы и квадраторы (11 .

Недостатком этих устройств является то, что они обладают ограниченными функциональными возможностями.

Наиболее близким к предлагаемому по технической сущности является устройство для умножения, содержащее согласующие усилители, входы которых являются соотве. гствующими входами устройства, а выходы подключены ко входам . суммирующего квадра тора, к входу каждого из согласующих усилителей подключен вход соответствующего квадра тора, первые:из разноименных выходов квадратора соединены, второй выход одного из квайэаторов подключен к одному выходу устройства, а второй выход другого квадpampa соединен с одноименным выходом суммирующего квадратора, второй вьмод которого подключен ко второму выходу устройства, источник регулирующего напряжения, выход которого.подключен ко входу суммирующего квадратора. Это устройство позволяет производить как

oBepaIMH уМножения, так и операции нахождения корней приведенного квадратного уравнения p2) .

Однако операция нахождения корней

1о приведенного квадратного уравнения выполняется вручную — сигнал на вьмоде источника регулируемого напряжения изменяют до тех пор, пока на выходе устройства установится нуль. Эти действия

15 затрудняют процесс вычислений и увеличивают время решения задачи.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, .

20 что в известное устройство для умножения сигналов, содержащее два согласующих усилителя, входы которьм соответственно являются первым и вторым входами устройства, первый сумматор, первый и вто3 9227 рой входы которого соответственно подключены к выходам первого и второго согласующих усилителей, три квадратора, вход первого квадратора подключен к выходу первого сумматора, введены второй сумматор, интегратор и переключатель, входы второго.и третьего квадраторов соответственно подключены к выходам первого и второго согласующих усилителей, а выходы первого, второго и третье- 10

I o квадраторов соответственно подключены к первому, второму и третьему входам второго сумматора, прямой выход которого является первым выходом устройства, инверсный выход сумматора 15 подключен к первому входу переключателя, первый выход которого подключен к входу интегратора, выход интегратора является вторым выходом устройства и подключен ко второму входу переключа-. 20 теля, второй выход которого подключен к третьему входу первого. сумматора.

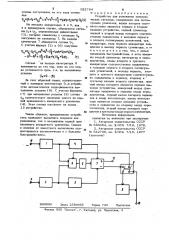

На чертеже приведена функциональная схема устройства для умножения электрических сигналов. 25

Устройство для умножения электри- ческих сигналов содержит два согласую-. щих усилителя 1 и 2, три квадратора

3, 4 и 5, два сумматора 6 и 7, переключатель 8 и интегратор 9, первый 50 вход 10 устройства, второй вход 11 устройства„первый выход 12 устройства, и, второй выход 1З устройства. Входы согласующих усилителей 1 и 2 соответственно являются входами 10 и 11 устройства, а выходы подключенных ко входам квадраторов 4 и 5 и первым и вторым сумматора 6. Выход сумматора 6 подключен ко входу квадратора 3, а инвертирующие выходы квадраторов 4 и 5 соединены со входами сумматора 7. Неинвертирующий выход. сумматора 7 является первым выходом 12 устройства, а инвертирующий выход сумматора 7 подключен к первому входу переключателя

8. Первый выход переключателя 8 соединен со вход м интегратора 9, Выход интегратора 9 является .выходом 13 устройства и подключен ко второму входу переключателя,8. Второй BblxoA IIe50 реключателя 8 соединен с третьим входом первого сумматора 6.

Устройство работает следующим обраэоь

Ы положении переключателя 8, изоб« раженном на чертеже, интегратор 9 отключен от инвертирующего выхода сумматора 7 и or третьего входа сумматоре 6.

На входы 1Î и 11 устройства подаются

84 4 сигналы с и Ъ соответственно подлежащие перемножению,,которые через согласующие усилители 1 и 2 поступают на входы квацраторов 3, 4, 5. На .выходах квадраторов 4 и 5 образуются сигналы (3

U =g<

v -ь%

На выходе квадратора 3 образуется сигнал U,, равный квадрату суммы сигналов а и Ь, поступивших на его вход

"3=(4 И ..(%)

Сигналы с выхода квадратора 3 и с инвертирующих выходов квацоатооов 4 и

5 поступают на входы сумматора 7. На выходе сумматора 7 образуется сигнал

Ц, равный сумме сигналов, поступающих на его вкоцы, который подается на выход 1 2 устройства. С учетом того, что используются инвертирующие выходы квацраторов 4 и 5 сигнал U опрецеляется () =g g =g р)

4 3

С учетом уравнений (1) и (2) получаем „р в в„ ф

Таким образом, на выходе 12 устройства образуется сигнал, пропорциональный произведению входных сигналов, т.е. устройство выполняет операцию перемножения

В.положении переключателя 8, противоположном изображенному на чертеже, интегратор 9 подключается своим входом к инвертирующему выходу сумматора 7, а выходом - к третьему входу сумматора

6. На входы 10 и 11 устройства поступают сигналы а и Q, пропорциональные коэффициентам р и q приведенного квацратного уравнения вида х .>px+,=0. (4)

Величины g u Q удовлетворяют условиям

Иа b)=P

ЪМ=% .

Я)

Как и в предыдущем случае, поданные на вход устройства сигналы через согласующие усилители 1 и 2 поступают на входы квадраторов 3, 4 и 5. Кроме ro го, на выход сумматора 5 поступает изменяющийся сигнал U C выкоца интегратора .9. Таким образом, на выхоце сумматора 6 действует сумма сигналов cD входов устройства и с выхода интеграто. ра 9. Поэтому на выходе квацратора 3 образуется сигнал Ug равный квадрату оцписное ираж

Филиал ЛПП "Патент", г. Ужгород, ул. Проектная, 4

5 9227 суммы .поступивших на его вход сигналов

Ч =(4 Ь )5) = 6 ФЬ 05 ЫЬ ЦФ 9 5(6)

На выходах квацраторов 4 и 5, как и в предыдущем случае, образуются сигна-. лы U< и О, определяемые райенствами (1), которые совместно с сигналом U поступают на сумматор 7. На выходе сумматора 7 образуется сигнал U>.

С учетом формул (1) и (6) получаем

0 ОЬ-01-0 =а Фь ФЧЪ|ФЫЬФМ6ФЪ)95- .

- a -6= Р+щ+ъ) и +ьь. hi

5 Ю

Сигнал на выходе .интегратора 9 изменяется до тех пор, пока на его входе установится нуль, т.е. до выполнения словия у

U>--O Л

За счет обратной связи, осуц ествляемой с помощью интегратора 9,.в устройстве автоматически поддерживается выполнение условия (8). С учетоМ формулы (7) при выполнении условия (8) сигнал 2s

0 соответствует значению одного из кор5 ней приведенного квадратного уравнения (4). Этот сигнал поступает на выход .

1 3 устройства.

Таким образом, предлагаемое устройство позволяет выполнять операции как умножения, так и нахождения корней приведенного квадратного уравнения. Однако в отличие от известного вычисления осуществляются автоматически и с большим быстродействием.

84 6

<Рормула изобретения

Устройство для умножения алектрических сигналов, содержашее цва согласующих усилителя, входы которых соответст. енно являются первым и вторым входами устройства, первый сумматор, первый и второй входы которого соответ ственно подключены к выходам первого и второго согласующих усилителей, три, квадратора, вхоц первого квадратора под-. ключен к выходу первого сумматора, о тл и ч а ю ш е е с я тем, что, с целью повышения быстродействия, в него введены второй сумматор, интегратор и переключатель, входы второго и третьего квацраторов соответственно подключены к выходам первого и второго .согласуюших усилителей, а выхоцы первого, второго и третьего квацраторов соответствен.l но подключены к первому, второму и третьему входам второго сумматора, прямой выход которого является первым выходом устройства, инверсный выход сумматора подключен к первому входу переключателя, первый выход которого подклю. чен к входу интегратора, выхоц интегратора является вторым выходом устрой-. ства и подключен ко второму входу переключателя, второй выход которого подключен к третьему вхоцу первого сумматора.

Источники информации, принятые во внимание при акспертизе1

1. Авторское -свидетельство СССР

М 586464, кл. Я 06 7/16, 1976.

2. Авторсков свидетельство СССР

М 642730, кл. Q 06G 7/16, 1977 (прототип) .