Преобразователь декартовых координат

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалнстнческнк

Республик ()922789 (61) Дополнительное к авт. свнд-ву (22) Заявлено 25.08.80 (21) 2976489/18-24 (51)М. Кл. с присоединением заявки М—

G 06@ 7/22

1Ъоудорстоаииый комитет

СССР ао лелем имбретеиий и открытий (23) Приоритет

Опубликовано 23.04.82. Бюллетень № 15 (53) УДК681. .3 (088.8) Дата опубликования описания 25.04.82 (72) Авторы изобретения

А, Б. Артамонов, А. Н. Жариков и А.„N. Смирнов

j

Ленинградский ордена Ленина электротехнический институт им, В. И. Ульянова (Денина).;. .„:„...:-.-.-, . (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДЕКАРТОВЫХ КООРДИНАТ

Изобретение относится к аналоговой вйчислительной технике.

Известен преобразователь декартовых координат, в котором по заданным прямоугольным координатам формируется суммарное гармоническое колебание, из которого затем в определенные моменты времени, определяемые заданным углом поворота координат, выделяются мгновенные значения, соответствующие повернутой системе координат (I J .

Недостаток этого преобразователя заключается в малом быстродействии, поскольку для выделения преобразованных. координат требуется время, болыйее, чем период одного колебания.

Известен также преобразователь координат, в котором преобразование осуществляется дискретными поворотами до обнуления одной из двух составляющих. В нем для убыстрения процесса преобразования предварительно определяется номер октанта, которому принадлежит аргумент (2) .

Наиболее близким к предлагаемому по технической сущности является прес4, разователь декартовых координат, в котором значения прямоугольных координат задают амплитуду и фазу колебания консервативного звена, образованного двумя интеграторами и инвертором, аргумент приводится к первому квадранту, в момент времени, соответствующий приведенному аргументу, консервативное звено размыкается, и значения координат, накопленные интеграторами, записываются в аналоговый запоминающий блок (3) .

Недостаток известного устройства заключается в том, что его быстродействие ограничено временем развертки, соответствующим четверти периода колебания.

Цель достигается тем, что преобразователь декартовых координат, содержащий первый интегратор, выход которого через первый ключ связан с входом втоюого интегратора, инвертор, вход которого

3 9227 связан с входами первого и второго ин,теграторов соответственно через второй и третий ключи, а выход инвертора через четвертый япоч связан с входом первого интегратора, двухканальный аналоговый запоминающий блок, первый вход которого через пятый ключ соединен с входом инвертора, а второй вход через шестой ключ - с выходом инвертора, причем выходы аналогового запоминаю- 10 щего блока являются выходами преобразователя, входы начальной установки первого и второго интеграторов через .седьмой и восьмой ключи соединены с соответствукяяими шинами задания декартовых координат, шина задания угла поворота через масштабирующий резистор, а шина опорного напряжения через дискретный делитель напряжения соединены с первым входом компаратора, шина опорного напряжения через девятый ключ соединена с входом третьего интегратора, вход начальной установки кьторого через десятый ключ связан с шиной нулевого потенциала, выход компаратора соединен с входом блока управления, соответствующие выходы которого соединены с управляющими входами ключей, двухканального аналогового запоминающего блока и дискретного делителя нащ)яженияэ дополни 3

30 тельно содержит сумматор, блок вычитания и четыре ключа, управляющие входы которых связаны с соответствующими выходами блока управления, при этом обе шины задания декартовых координат соединены с соответствующими входами

3З сумматора и блока вычитания, выход сумматора через первый дополнительный ключ соединен с входом начальной установки первого интегратора, выход блока вычитания через второй дополнительный

40 ключ соединен с входом начальной установки второго интегратора, выход третьего интегратора через третий дополнительный ключ соединен. с вторым входом компаратора, который через четвертый дополнительный ключ соединен с шиной нулевого потенциала.

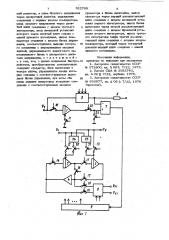

На фиг. 1 изображена схема преобразователя декартовых координат; на фиг. 2вариант выполнения блока управления, входящего в состав преобразователя.

Иреобразователь содержит интеграторы 1-3, инвертор 4, дискретный делитель напряжения (ДДН) 5, масштабирующий резистор б,компаратор 7, двухканаль- 33 ный аналоговый запоминающий .блок 8, блок 9 управления, ключи 10-23, сумматор 24, блок 25 вычитания. Блок 9

4 управления содержит генератор 26 импульсов, триггеры 27 и 28, одновибраторы 29-31, элемент И 32, реверсивный счетчик 33, дешифраторы 34 и 35, инверторы 36 и 37.

Сущность предложения заключается в использовании неявной симметрии тригонометрических функций, которая при неизменном диапазоне изменения моделируемой входной величины, представляющей собой угол поворота системы координат, позволяет уменьшить диапазон изменения моделирующего аргумента.

Преобразователь работает следующим

; образом.

Цикл работы состоит из 5 тактов.

Первый такт (.) предназначен для выяснения,. к какому из 8 октантов принадлежит входной аргумент, моделирующий угол поворота декартовой системы координат; во втором такте (L q ) устанавливаются начальные условия интеграторов 1-3; в третьем такте (Т ) устройством вырабатываются выходные ве личины Оу < и Uy в четвертом (Г 4 ) и пятом (5 ) тактах выходные величины Ug и U> „последовательно записываются в блок 8.

Второй, четвертый и пятый такты имеют фиксированные длительности, величины которых задаются одновибраторами 29-31. Длительности первого такта зависят от величины входного аргумента, моделирующего угол поворота, и третьего — от времени непосредственно преобрасзования; началом каждого из них является конец предыдущего такта, а. окончани» ем - сигнал с компаратора 7.

В первом такте замыкается ипоч 23, а реверсивный счетчик 33. вырабатывает равномерно убывающий двоичный код, поступающий на трехразрядный дискретный делитель 5 напряжения. Если выходное сопротивление ДДН 5 постоянно (наприi мер, используется делитель на основе сегки % -2R) и равно величине резистора

6, то на основе компаратора 7 образуется схема сравнения токов. В момент,. когда выходной сигнал компаратора станет равным нулю, триггер 27 переходит в нулевое. состояние, а на реверсивном счетчике 33 сохраняется номер октанта, которому принадлежит аргумент, моделируемый отношением напряжений U< и Ug .

Во втором такте замыкается ключ 11, а также два из ключей 12, 13, 20 и 21, соответствующие установленному номеру октанта. Задний фронт 7 устанавливает в единичное состояние триггер 28.

5 9227

В третьем такте работы - такте вы работки устройством величин ОХ1и Оу1 эаьжнуты ключи 10, 14, 15, 17 и 22.

Выходное напряжение интегратора 1 линейно возрастает. 5

И1

t т„

89 6 записывается через ключи 17 и 18, а в шестую ячейку — через ключи 16 и 19.

4) Для четвертого октанта (3)

= — — (X4J)Sian, +, Ч-Х)

Гъ

З =- — У4Ч)оа i X) Scend<

% %

1 1 tL где Т - постоянная времени интеграто-.

1 ра 1.

Напряжение с выхода интегратора 1 сравнивается на компараторе 7 с напряжением - (U — — Uy ), где и — номер

1 и

8 октанта, в котором находится входной аргумент. В момент равенства входных 15 сигналов компаратора„отмечаемого единичным сигнапом на его вЪ ходе, ь =

Т V1 5 (— — — ). Единичный сигнал ком-, Uc. в паратора сбрасывает в ноль триггер 28, размыкая ключи 10, 14, 15 и 22, при этом интеграторы 2 и 3 превращаются в кратковременные аналоговые запоминающие устройства, хранящие вепичины напряжений, соответствующих значениям кобрдинат в повернутой на угол А системе.

Соотношение постоянных времени интеграторов 1, 2 и 3 должно быть равно

4л. т

В зависимости от того, какому октанту принадлежит аргумент d на интеграторах 2 и 3, устанавливаются различные начальные условия 0 и 0 > а напрян н жения ИХ., и U> снимаются с различных

1 точек:

1) В первом октанте (и = О) уст- з5 ройство работает так же, как известное устройство: в интегратор 2 записывается

Ок, в интегратор 3 - Uy, в первую ячейку блока 8 сигнал подается через ключи 16 и 18, а во вторую - через кличи 17 и 18.

2) Оля второго октанта (и = 1).

Преобразователь декартовых координат, содержащий первый интегратор, вы40 ход которого через первый ключ связан с входом второго интегратора, инвертор, вход которого.связан с входами первого и второго интеграторов соответственно через второй и третий ключи, а исход

45 инвертора через четвертый ключ связан с входом первого интегратора, двухканальный аналоговый запоминающий блок, первый вход которого через пятый ключ соединен с входом инвертора, а второй вход через шестой ключ — с выходом инвертора, причем. выходы аналогового запоминающего блока являются выходами преобразователя, входы начальной установки первого и второго интеграторов через седьмой и восьмой ключи сое динены с соответствующими шинами задания декартовых координат, шина задания угла поворота через масштабирутоХ = ((у)СоЬд.,+ (J 3)510*

У =--(gay)9(ed — (3-х)СОМА

Я Ж (В первую ячейку блока 8 сигнал ОХ1 записывается через ключи 16 и. 18, а во вторую — через ключи,-17 и 18.

3) Дпя третьего октанта (= 2) 3 "--Х 3 М14J COSd.1

У =-(XQOSd, 3Sied1).

Здесь в интеграторы 2 и 3 заносятся соответственно напряжения UX и Оц, в одиннадцатую ячейку блока 8 напряжение

На интеграторы 2 и 3 подаются соответственно напряжения КV +Q ) и -И0 - V )

iх м ч, В бпок 8 сигнал Ох1 заносится через и 17 и 18, а 0М„- через и 16 и 19.

Работы преобразователя в последующих октантах отличается только изменением знака напряжений Цх1 и V>„. Так,в пятом октанте сигналы поступают в блок 8 с выхода инвертора 4 через ключ

19, а процесс вычисления соответствует случаю первого октанта.

Аналогично шестой октант соответствует второму, седьмой — третьему, а восьмой - четвертому.

Таким образом, введение сумматора

24 и блока 25 вычитания с соответствующей коммутацией элементов позволило примерно вдвое сократить время вычисления, что и определяет технико-зкономический эффект от использования изобрете ния.

Формула изобретения

922789 щий резистор, а шина дпорного напряжения через дискретный делитель напряжения соединены с первым входом компаратора, шина опорного напряжения через девятый ключ. соединена с входом третьего интегратора, вход начальной установки которого через десятый ключ связан с шиной нулевого потенциала, выход компаратора соединен с входом блока управления, соответствующие выходы которо- 10

ro соединены с управлякпцими входами ключей, двухканального аналогового за» поминающего блока и дискретного делителя напряжения, о т л и ч а ю щ и йс я тем, что, с целью повышения быстро-15 . действия, преобразователь дополнительно содержит сумматор, блок вычитания и четыре ключа, управляющие входы которых связаны с соответствующими выходами блока управления, при этом обе щ шины задания декартовых координат соединены с соответствующими входами сумматора и блока вычитайия, выход сумматора через первый дополнительный ключ соединен с входом начальной установки первого интегратора, наход блока вычитания через второй дополнительный ключ соединен с входом начальной установки второго интегратора, поход третьего интегратора чейз третий дополнительный ключ соединен с вторым входом компаратора, который через четвертый дополнительный ключ соединен с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетепьство СССР

% 572800, кл. G 06Gj 7/22, 1975.

2. Патент США % 3932740, кл. G 06 Q 7/22, опублик. 1976.

3. Авторское свидетельство СССР

% 638977, кп. 5 06 Q 77//2222, 1976 (прототип) .

Составитель Г, Осипов

Редактор Л. Гратилло Те)сред Ж.Кастелезич Корректор C. Шекмар

Заказ 2584/66 Тираж 732 Подписное

ВНИИПИ Государственно о комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4