Логарифмический преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗО6РЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()922791

Союз Советски к

Социалистическик

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 26.09.80 (21) 2985711/18-24 (5l)IN. Кл. с присоединением заявки М

Gj 06Q, 7/24

3Ъеудэратееный квинтет

СССР аю делэм изобретений и юткрытнй (23) Приоритет

Опубликовано 23.04. 82. еноллетень,% 15

Дата опубликования описания 25.04.82 (53) УДК 681. .335 (088. 8) (72) Авторы изобретения

К). В. Хохлов, В. Д. Биделко, С. ф. Уйййнне, К). Г. Туманов, Н. Н. Барышевский и В. А. Тесленко

7 ,1 .. е, f

Киевский ордена Ленина политехнический институт нм. 50 летия Великой Октябрьско социалистической революции

) и (7l ) Заявитель (54) ЛОГАРИФМИЧЕСКИЙ ПРЕОБРА ЗОВАТЕЛЬ

Изобретение относится к устройствам преобразования электрических сигналов по логарифмическому закону и может быть использовано в вычислительных машинах, 5

Известен логарифмический преобразователь, содержащий источник опорного напряжения, интегратор, функциональный частотный преобразователь, схему срав.нения, триггер (1 . !

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предложенному является логарифмический преобразова1$ тель, содержащий переипочатель, преоб. разователь кода в напряжение, два аналоговых запоминающих устройства, схему сравнения, регистр, генератор импульсов, распределитель импульсов, блок управления и источник опорного напряжения (21 .

Однако известный логарифмический преобразователь имеет сложную функцио, нальную схему и невысокую точность, работы.

Бель изобретения — повышение точности работы и упрощение.

Поставленная цель достигается тем,, что в логарифмический преобразователь, содержащий соединенные последовательно первый ключ, аналоговое запоминающее устройство, схему сравнения и регистр, выходы которого являются выходами логарифмического преобразователя, входом которого является вход первого ключа, второй ключ, выход которого подключен к выходу первого ключа, генератор mvrпульсов, инвертор, источник опорного напряжения и распределитель импульсов, выходы которого соединены со входами регистра, первый выход распределителя импульсов подключен к управляющему входу первого ключа и входу инвертора, выход которого соединен с управляющим входом второго ключа, выход генератора импульсов подключен к управляющему входу аналогового запоминающего устрой91 4 ное по первому тактовому импульсу.

Причем t =1, йРй 01100 (Ц, )1=0 0>< 01<0О, (Ъ) где Оо- опорное напряжение.

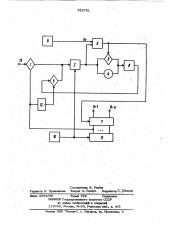

Разряды регистра 7, в которые записывается информация, выбираются после.довательно, начиная со старшего, с помощью распределителя 11 импульсов. (. поступлением второго тактового импульса на вход распределителя .11 импульcos первый ключ 1 размыкается, второй ключ 9 замыкается, и в аналоговом запоминающем устройстве 2 запоминается напряжение с выхода квадратора 8, которое подается на схему 5 сравнения.

Еспи зто запомненное напряжение больше опорного, то в следующий разряд регистра 7 записывается 1 ", и дополнительный ключ 3 размыкается, если же запомненное напряжение меньше опорного, то в регистре 7 записывается "О», и дополнитепьный ключ 3 замыкается.

В результате к,,концу второго такта на выходе квадратора 8 установится напряжение

11ричем

i<ð1, пои U тоо

i<-0, net U<< g g)

Далее работа происходит аналогично до тех пор, пока информация не будет записана в последний разряд регистра 7.

В итоге, к концу последнего такта на выходе квадратора 8 установится напряже ние

" " U> " (В) 3 92 27 ства и ко входу распредепителя импульсов, ко второму входу схемы сравнения подключен выход источника опорного напряжения, введены дополнительный ключ и соединенные последоватепьно 5 масштабирующий блок и квадратор, выход квадратора подключен ко входу второго ключа, вход дополнительного ключа соединен со входом масштабирующего блока и с выходом аналогового запоминающего устройства, выход схемы сравнения подключен к управляющему входу дополнительного ключа, выход которого соединен с выходом масштабирующего блока. 15

На чертеже изображена функциональI ная схема предложейного логарифмического преобразователя.

Схема содержит первый ключ 1, ана- логовое запоминающее устройство 2, дополнительный ключ 3, масштабируюший блок 4, схема 5 сравнения, источник 6 опорного напряжения, регистр 7, квадратор 8, второй ключ 9, генератор 10 импульсов, распределитель 11 импульсов, инвертор 12, вход 13 и выходы 14-1, 14- f1 логарифмического анапого-цифровопб преобразователя.

Логарифмический преобразователь работает следующим обрааом.

ЗО

С поступлением первого тактового импульса от генератора 10 имйульсов на вход распредепителя 1 1 импульсов замыкается первый ключ 1, размыкается вто рой ключ 9 и на аналоговое запоминаю35 щее устройство 2 подается преобразуемое напряжение со входа 13. По тактовому импульсу происходит также запись в аналоговое запоминающее устройство 2, с выхода которого запомненное напряже40 ние поступает на схему 5 сравнения. Если запомненное напряжение больше опорного напряжения, то в старший разряд регистра 7 записывается «1", и дополнительный ключ 3 размыкается. Если за45 помненное напряжение. меньше опорного, то в старший разряд регистра 7 записывается "О, и дополнительный ключ 3 замыкается. В результате, в конце первого такта на выходе квадратора 8 устанавпивается напряжение

611" 1 ) „ф . и 1 1()

bnb "....Ь а Ь где Ug — напряжение на входе 13, ТаК как показатели степени в выражении (6) соответствуют разрядам регистра 7, причем

1 =0„ flPM 0„(0 (-ц) где ф1—

b основание логарифма; коэффициент передачи масштабирующего блока 4; напряжение аналогового запоминающего устройства 2, запомненто, логарифмнруя обе части выражения (5); получим, что результирующий код в регистре 7 равен логарифму от входного напряжения йо выбранному основанию

1+ —,„Ь вЂ” 1 Ф...+ — 1 =90/1Ð - Я)

° °

4 ° 4 1 ° Х

14 В 3"

5 9227

По сравнению с известным устройством в предложенном логарифмнческом преобразователе. повышена точность работы, определяемая точностью только квадратора при более прост .й функциональной 5 схеме.

Формула изобретения

Логарифмический преобразователь, содержащий соединенные последовательно первый ключ, аналоговое запоминающее устройство, схему сравнения и регистр, выходы которого являются выходами логарифмического преобразователя, входом которого является вход первого ключа,,второй ключ, выход которого подклЮчен к выходу первого ключа, генератор.им пульсов, инвертор, источник опорного 20 напряжения и распределитель импульсов, выходы которого соединены с входами регистра, первый выход распределителя импульсов подключен к управляющему входу первого ключа и входу инвертора, 25 выход которого соединен с управляющим входом второго ключа, выход генератора импульсов подключен к управляющему входу аналогового.запоминающего устройства и к входу распределителя импульсов, к второму входу схемы сравнения подключен еьц од истОчника опор» ного напряжения, о т л и ч а ю щ и йсятем, что,,с целью повьпаения точност работы и упрощения, в него введе= ны . дополнительный ключ и соединенные последовательно масштабируккций блок и квадратор, выход квадратора. подключен к входу второго ключа, вход дополнительного ключа соединен с входом масштабируюшего блока и с выходом аналогового запоминампего устройства, mrs схемы сравнения поципочен к управляющему входу дополнительного ключа, выход которого соединен с выходом масштабируюшего блока.

Источники информапии, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 424171, кл. Я 06Gj 7/24, 1974.

2. Авторское свидетельство СССР . № 540266, кл. Gi 064 7/24, 1976 (прототип) .

Составитель В. Рыбин

Редактор H. Пушненкова Техред Л,э Пекарь. Корректор, С Шекмар .Заказ 2584/66 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений н открытий

113035, Москва, Ж-35, Раушскан наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4