Цифровая динамическая следящая система

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

Союз Советских

Соцнаяиктичесиих

Республик (и 9

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву 33 244464 (22) Заявлено 08.07.80 (21) 2954554/38»24

Ю. с присоединением заявки М ". (Sl }M. Кл. (3)5. В 11/52

С 05 В 33/14

9нудлрстваиивй комитет

СССР ию дилан иэебретеинй н еткрытий (23)Приоритет " (5З}УДК 62-50 (088. 8) Опубликовано 30.04.82 ° Бюллетень № 16

Дата опубликования описания 30 .04.82 (72) Авторы изобретения

А. Д. Подлиннов и B. В. Шкирятов

j 1 .. (73) Заявитель (54) ЦИФРОВАЯ ДИНАМИ4ЕСКАЯ СЛЕДЯЩАЯ

СИСТЕМА

Изобретение относится к автоматике, а именно к следящим системам управления и фильтрации, в частности к-следящим фильтрам для выделения сигналов на фоне помех.

По основному авт. св. и 244464 известна следящая система, содержащая смеситель, цифровой дискриминатор и преобразователь код - частота, причем параллельно с выходом цифрового дискриминатора дополнительно включено m последовательно соединенных между собой реверсивных счетчиков, выход которых подключен ко входу преобразователя код - частота t31.

Основным недостатком известной си-! стемы является невысокая точность вследствие дрейфа фазы выходного сигнала, обусловленный тем, что цифровЬй дискриминатор работает,по откло" нению приращения Фазы входного сигна" ла промежуточной частоты относительно эталонного значения этой частоты и является нечувствительным к началь" ной фазе входного сигнала.

Цель изобретения - повышение точ" ности системы.

Указанная цель достигается тем, что в систему введен блок эталонной частоты, .выход которого подключен к второму входу цифрового дискриминатора, второй выход которого соеди" нен с вторым входом преобразователя код - .частота.

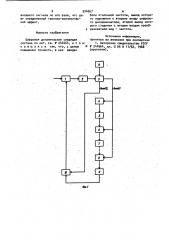

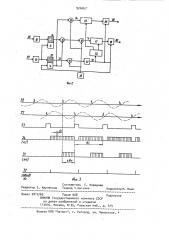

На фиг. 1 приведена блок-схема предлагаемой системы; на фиг. 2пример реализации цифрового дискриминатора; на Фиг. 3 - временные ди. аграммы работы цифрового дискриминатора.

Цифровая динамическая следящая система содержит смеситель 1, усилитель 2 промежуточной частоты, цифровой дискриминатор 3, блоки коэффициентов передачи и реверсивные счетчики 4-9, преобразователь 1О код - час" ,тота, блак 11 эталонной частоты, фор3 924667 4 мирователь 1? опорного сигнала, форми" состоящий в общем случае иэ и-разрядрователь 13 измеряемого сигнала, flap» ного счетчика-делителя. Импульсы с вый триггер 14, первый и второй вен- выхода делителя 22 частоты поступают тили l5 и 16> первый счетчик 17, пер- на опрос регистров 18 и 26, считывая вый регистр 18, генератор 19 этапон- g цифровые значения частотного рассогных импульсов, второй триггер 20, ласования ьИу и фазового рассогласотретий вентиль 21, делитель 22 часто- вания dNq на выход дискриминатора ть!„ регистр 23 опорных чисел, четвер- и одновременно записывая в счетчики тый вентиль 24 второй счетчик 25, 17 и 25 через регистр 23 опорных чивторой регистр 26, первый 27 и вто-,10 ел числа i4; Nq, и устанавливается рой 28 входы цифрового дискриминато- триггер 20 в нулевое состояние для ра, первый 29 и второй 30 выходы циф- очередного измерения >7 и Nqt. рового дискриминатора,. выход 31 вен- П „ „ -. „ 2к, тиля 16, выход 22 частоты делителя 32, с выход 33 триггера 20, выход 34 венти" 15 ля 24, тогда окончательно имеем Юг 4г

fear 0g Ь} q

С b

Система работает следующим абрамкам.

Напряжение промежуточной частоты с выхода усилителя 2 поступает на вход цифрового дискриминатора 3, где на первом выходе выделяется величина рассогласования бар в цифровой форме.

Все время обработки величины рассог" ласования Ч занимает в системе астатизмом и-го порядка m временных циклов, Во время первого цикла величина М записывается с соответстующими коэффициентами передачи в реверсив30 ные счетчики, которые используются в качестве интеграторов, Во время второго цикла число из реверсивного счетчика 5 со своим знаком записывается в реверсивный счетчик 7, где суммируется с имеющимся там числом.

Таким образом, после окончания m-го цикла в реверсивном счетчике 9 образуется результирующее число, пропорциональное сумме одинарного, двойного, тро" íîãî и т.д. вплоть до m-го

40 интеграла от величины рассогласова" ния. Пропорционально этому рассогласованию на выходе преобразователя 10 код - частота образуется частота, которая поступает на смеситель l

Дискриминатор 3 работает следу" ющим образом.

Сигнал с выхода усилителя 2 промежуточной частоты поступает через первый вход 27 на формирователь 13 для формирования импульсов в момент перехода синусоидального сигнала через нулевой уровень. При поступлении очередного импульса с выхода формирователя 13 триггер 20 устанавливает- 5 ся в единицу и открывает вентиль 21, в результате чего счетные импульсы проходят на делитель 22 частоты, где Т и Т - периоды измеряемого и опорного сигналов соответственно.

При поступлении на единичный вход триггера 20 очередного импульса f цикл работы повторяется.

Согласно временной диаграмме (фиг. 3) на выходе триггера 20, вентилей 15 и 16 формируется мерный интервал, пропорциональный фазовому сдвигу между опорным импульсным сигналом 28 и измеряемым 27. В счетчике 17 с учетом предварительно записанного числа Nq пропорционального половине периода опорного сигнала Г, образуется величина a Nq = Ng - Ne которая через регистр 18 считывается на второй выход 30 дискриминатора.

Преимущество предлагаемой динамической следящей системы состоит в том, что за любой интервал времени ее работы расхождение текущей фазы фходного сигнала код " частота относительно фазы входного сигнала не превышает половины периода частоты входного сигнала, поскольку предлагаемая следящая система, обладая всеми достоинствами частотной автоподстройки частоты в части вхождения в синхронизм, практически при любом частотном рассогласовании обеспечивает отслеживание входного сигнала с точностью до его фазы.

Таким образом, предлагаемая цифровая динамическая следящая система, обеспечивая высокие качества системы частотной автоподстройки, обладает и высокой точностью отслеживания

5 924667 6 входного сигнала по его фазе, что да- блок эталонной частоты, выход которо" ет определенный технико-экономичес- . ro подключен к второму входу цифровокий эффект. го дискриминатора; второй выход кото-. рого соединен с вторым входом преобразователя:;код - частота. формула изобретения

Цифровая динамическая следящая система по авт. св. У 244464, о т л ич а ю щ а я с я тем, что, с целью повышения точности, в нее введен

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

И 244464. кл. G 05 В f 1/52, 1968 (прототий).

924667

/, (Мод)

Составитель Г. НеФедова

Редактор С. Крупенина Техред Т Наточка

Корректор И. Пожо

Заказ 2817/65 Тираж 908

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

133035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4