Запоминающее устройство на ферритовых сердечниках

Иллюстрации

Показать всеРеферат

А. А. Крупский, С. П. Кунерман и N. И. Чельднев (72) Авторы изобретения (7l ) Заявитель (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО НА ФЕРРИТОВЫХ

СЕРДЕЧНИКАХ

Изобретение относится к цифровыь1 электронным вычислительным машинам (ЭВМ). и может быть использовано при построении вапоминаюижх устройств . (ЗУ) на ферритовых сердечниках с пря моугольной петлей гистерезиса.

Известны ЗУ на ферритовых сердвчни«ах, выполненные по системе 2,5Д и работающие, в основном, в режиме обращения по большим группам последовательных ад-. ресов (1).

Недостатком известных 3 У является" большая вежчина помехи.

Наиболее близким к предлагаемому яв.ляется ЗУ на ферритовых сердечниках, со15 держащее накопитель, выполненный по системе 2,5Д -к адресно-разрядным (X) a адресным (У) обмоткам которого подклю чены выходы адресно-разрядных и адрес, ных блоков дешифраторов и формирователи импульсов така, входы которых соединены с вводами адресно-разрядного и адресного регистров, ко входам которых поаключены шины приема адреса. При. этом. wzoAH fn разрядов адресно-разрядного и л разрядов адресного регистра совшинены с одноименными входами адресно разрядного и адресного блоков пешнфрат оров и фор мирователей имбо льсов тока, 2нт выходов адресно-разряцного и 2" выходов адресно го блоков цешифраторов и формирователей импульсов тока соединены с одноименными адресно-разрядными и адресными обмотками накопителя 21.

Недостатком известного ЗУ является большая величина помехи от полувыбранных сердечников, подвергающихся воздействию импульсов адресно-разрядного или адресного токов, что снижает нацвжность ЗУ, затрудняет увеличение его быстродействия, Бель изобретения - повышение надежности ЗУ эа счет уменьшения помех от полувыбранных, сердечников.

Поставленная цель достигается тем, что в ЗУ, содержащем накопитель, выполненный по системе 2,5Д, входы которого подключены к выходам адресного и адресно-разрядного дешифраторов второй ступе3 4 эом: выход 11» первого (младшего) разряда адресного регистра 8 соединены со входом 12„последнего (старшего) . разряда адресного блока 6 дешифраторов первой ступени, выходы со второго по

-й адресного регистра 8 подключены ко входам с первого по (n-1)-й адрес ного блока дешифратора первой ступени 6.

За счет такого выполнения связей.адресного регистра с адресным блоком дешифраторов первой ступени при подаче последовательных адресов на регистр адреса адресные обмотки выбираются поочередно слева и справа от перекрытия выходной обмотки.

Устройство работает следующим образом.

Допустим, что выбираемый массив имеет адреса с 18 -1+, а для õðàнения рассматриваемого разряда массива

t используются сердечники, находящиеся на пересечении обмотки 17 и обмоток 18„ по 18 ° . При обращении к этому массиhy последовательно выбираются адресные обмотки 18 -18(z. ai)) . 18, 18 р" >2) п

18у, 18 +>> ..., 18а

18 при этом с каждой адресной обмот кой выбираются адресно-разрядная обмотка 17„. Такая последовательнссть выборки адресных обмоток повторяется при любой выбранной адресно-разрядной обмотке.

Сменим значение той составляющей помехи or полувыбранных сердечников, которая связана с неидентичностью состояний компенсирующих друг друга пар полувыбранных сердечников, расположенных с разных сторон от перекрестия.

Помеха or полувыбранных сердечни-. ков возникает при воздействии на них импульса тока считывания только по одной из координат., причем большую помеху дают сердечники, находящиеся в состояниях единицы и разрушенного нуля.

Компенсация этих помех обеспечивается прошивкой выходной обмотки с перекрещИванием прямого и обратного проводов, причем наилучшая компенсация (суммарная помеха, близкая к нулю) обеспечивается, если на взаимно компенсирующих отрезках выходной обмотки имеется одинаковое количество сердечников, дающих большую помеху, и одинаковое — дающих малую помеху.

После подачи тока считывания, например, в обмотку 17< все сердечники этой обмотки находятся в состояниях разрушенной единицы, либо в ссстоянии нуля, т.е. при следующем считывании все

3 02475 ни, входы которых подКлючены к выходам адресных и адресно-разрядных формироватежй, входы которых подключены к выходам адресного и адресно-разрядно о дешифраторов первой ступени, входы которых подключены к выходам адресного и адресно-разрядного регистров соответственно, входы которых подключены к адресным шинам, первый выход адресного регистра подключен к и -му входу адресного дешифратора первой ступени, а выход адресного регистра с второго по /о -ый . подключены к входам адресного дешиф ратор6 первой ступени с первого по (n -1) -й соответственно.

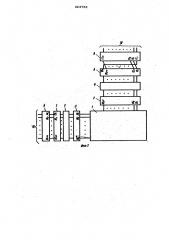

На фиг. 1 изображена схема предлагаемого устройства, на фиг. 2 - схема про шинки одного разряда накопителя.

Устройство содержит накопитель 1,адресный блок 2 дешифраторов второй ступени,адресно-разрядный блок 3 дешифраторов второйступени, адресный блок 4 формирователей импульсов тока, адресно-разрядный блок 5 формирователей импульсов, тока, адресный блок 6 дешифраторов первой ступени, адресно разрядный блок 7 дешифраторов первой ступени, адресный регистр 8 на 6 разрядов, адресно-разрядный регистр 9 на гп разрядов, шины поиема адреса 10, выходы адресного

36 регистра 11 11г,, входы адресного блока дешифраторов первой ступени 12„

12д выходы адресного блока дещифраторов второй ступени 13„-13 „выходы ад ресно-разрядного регистра 14 -14п1, входы адресно-разрядного блока дешифра» з торов 15„-15„,первой ступени, выходы адресно -разрядного блока дешифраторов второй ступени 16 -16 „ адресно-разрядные обмотки накопителя 17 -17, адресные обмотки накопителя 18„-18 .", 40 ферритовые сердечники 19, выходную обмотку 20, перекрестия проводов выходной обмотки 2 1.

Накопитель 1 содержит координаты обмотки: адресно-разрядные 17> - 17, к которым подключены одноименные выхо . яы 16 -18р адреснсь-разрядного блока дешифраторов второй ступени 3, и адресные

18 -18 п к которым подключены одноименные выходы 13 -1S„n адресного бж го

1 ка дешифраторов второй ступени 2.

Выходы 14„-14„„ адресно-разрядного регистра 9 соединены с одноименными входами 15 -15,„адреснс разрядного блока 7 дешифраторов первой ступени.

Выходы 11„11„адресного регистра 8 ооединены со входами блока 6 дешифра- торов первой ступени следуюшкм обра1. Запоминающее устройство современНых ЭЦВМ, Сб. статей под ред. <рупсКо го А. А. М., Мир, 1968; с. 56.

5 9247 они дают малую помеху, и обеспечивается наилучшая компенсация. Если после этого начинается обращение к некоторому массиву и многократно выбирается обмотка 17к, . то на сердечники обмотки 17r 5 ,воздействуют импульсы тока в обмотках.

18)þ 18g(qi ); " 18, 18р и/ +g) и т.д., после которых соответствующие сер» дечники остаются в состояниях единицы, либо разрушенного нуля, т.е. при следу 10 ющем обращении они дают большую помеху. Поскольку подача тока в обмотки

18 в предлагаемом устройстве произв ° дится поочередно - сперва в одну обмотку сжва от перекрестия проводов выход» t5 ной обмотки, затем в одну обмотку справа от перекрестия проводов выходной об мотки и т.д., то наибольшая суммарная помеха при первом обращении к обмотке

17, отличается or случая наилучшей го . Компенсации только нв величину разности между большой и малой помехами с одной пары сердечников. Аналогичный эффект достигается также во всех других случаях например, если перед обращени- г5 ем к данному массиву по рассматриваемой обмотке 17 подается имцульс тока записи.

Таким образом, в предлагаемом устройстве рассматриваемая составляющая помехи от полувыбранных сердечников по адресно-разрядным обмоткам умень- . шается в 2" /2 раз, в по адресным обмоткам в 2 /2 ðàý. Для современных массовых ЗУ системы 2,5Д значения 2 и 2 составляют соответственно 25655

512 и 32-64, поэтому в предлагаемом устройстве суммарная помеха уменьшв ется в несколько раз, Это позволяет су щественно повысить надежность (веро- .1ц ятность бессбойной работы )устройства, 53 6 либо увеличить быстродействие устройст вв в 1 2-2 раза за счет уме ьшения временй затухания помехи.

Ф о р м у л а. и з о б р е т е н и я

Запоминающее устройство на ферритовых сердечникал, содержащее накопитель, выполненный но системе 2,5Д, входы ко-. торого подключены к выходам адресного и адресно-разрядного дешифраторов второй ступени, входы которых подключены к выходам адресных и адресно-разрядных формирователей, входы которых подключены к выходам адресного и адресно-разрядного дешифрвторов первой ступени, вхо ды которых подключены к выходам Brtpec» ного и адресно-разрядного регистров со- . ответственно, входы которых подключены,R адресным шинам, î т л и ч в ю щ е е с я тем, что, с цежю повышения надежности устройства, в нем первый выход адресного регистра подключен к д - му входу адресного дешифратора первой сту пени, где rt -число разрядов адресного регистра, а выходы адресного ре 5 с тра с второго по и -й подключены к входам адресного дешифрвтора первой ступени с перво о по (,n-Õ)-й соответственно.

Источники информации, принятые во внимание при экспертизе

2. Шинн А. Г. и Дерюгин А. А. Циф ровые вычислительные машины, N., Энергия", 1975, с. 161 (прототип).

924753

МФ ° ° 1фр fP g б ф) К

Составитеи А. Дерюгин

Редактор Ю. Середа Тещред: М.Гергель Корректор H. Швыдкая

Заказ 2826/69 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауаскаа иаб., д 4/5

Фи жал ППП Патент, г. жгород, ул. Проектная, 4

1 (!У р

1У М

3 Ю! 1У!1