Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А H N E (ii)924755

ИЗОВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Соцнапнстннескнз

Респубяни (Bl ) Дополнительное к авт. свид-ву(22) Заявлено 27. 06. 79 (21) 2786717/18-24 (sl)M. Кл. с присоединением заявки.1те

6 11 С 27/00

9твуаеретееивыН квинтет

СССР ао делен изееретееив

II етерыткя (23) ПриоритетОпубликовано )g,p4 82 Бюллетень М l6

Дата опубликования описания 30 .04 .82 (53) УДК 681. З27..66(088.8) (72) Автор, изобретения

6. В. Тимофее в (7l) Заявитель (54 ) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при создании спе- i циализированных аналоговых и. комбинированных вычислительных устройств.

Аналоговое запоминающее устройство (АЗУ ) предназначено для запоми. нания и хранения определенное время мгновенных значенйй входного запоминаемого напряжения. Запоминаемое напряжение подают через ключ к нако36

° пительному конденсатору, который заряжается до мгновенного значения это.го напряжения. При размыкании ключа накопительный конденсатор запомина1$ ет,значение напряжения, которое было на нем в момент размыкания ключа.

Известно АЗУ, обеспечивающее запоминание и хранение мгновенных значений напряжения )1) .

Недостатком этих устройств является невысокая точность запоминания при коммутации импульсными сигналами малой длительности с большой скважностью, обусловленная следующими причинами.

Для получения высокой точности запоминания необходимо выбирать большую постоянную времени разряда Tpa>b. накопительного элемента. Для этого приходится выбирать кроме определенной величины сопротивления разряда и большое значение емкости накопительного конденсатора . Это приводит к увеличению постоянной времени заряда емкости Т -„ при замкну3Р том ключе, которая примерно равна

Т --= В„;С,и к тому, что за время открытого состояния ключа, определяемого временем действия коммутационного импульса, емкость не успевает зарядиться до амплитудного значения входного сигнала. Это вызыва- ет ошибку в запоминании. Уменьшение запоминающей емкости <для возможности заряда до амплитудного значения ) приводит к уменьшению Трвьр.

92475 и увеличению ошибки. за счет разряда емкости при разомкнутом ключе..Поэтому обеспечить высокую точность при небольших длительностях импульса коммутационного сигнала и при его большой скважности, не удается.

Наиболее близкой к предлагаемой является схема выборки-хранения сигналов, Устройство содержит накопительный конденсатор; одна обклад- lo ка которого соединена с общей шиной, а другая - с неинвертирующим входом операционйого усилителя (ОУ),вы ход которого соединен с инвертирующим входом ОУ и выходом устройства» и. че- 15 рез ключ, управляемый сигналом выборки, со входом устройства l2);

Недостатком устройства является невысокая точность запоминания при коммутации импульсными сигналами ма-, 20 лой длительности и большой скважнос" ти накопительного конденсатора (при размыкании ключа) либо ошибкой за счет того, что конденсатор за время действия коммутирующего импульса при замкнутом ключе не успевает зарядиться до амплитудного значения входного сигнала.

Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем, что в аналоговой запоминающем устройстве, содержащем ячейки памяти, каждая из которых выполнена на накопительном элементе, нап35 ример на конденсаторе, одна из обкладок которого соединена с шиной нулевого потенциала, ключе, выход которо" го соединен с обкладкой конденсатора и неинвертирующим входом операционного усилителя, охваченного по инвертирующему входу обратной связью, и шину управления, подключенную к одному из входов ключа, в каждую ячейку памяти, кроме первой, введены расширитель длительности сигнала управления и переключатель,первый вход каждого из которых, кроме первого, соединен с выходом переключателя предыдущей ячейки памяти, 50 .а вход первого переключателя соединен с выходом первого операционного усиЛителя, второй вход переключателя каждой ячейки памяти подключен к выходу операционного усилителя данной ячейки памяти, вход расширителя длительности сигнала управленив каждой ячейки памяти подключен каине управления и первому входу кло.

5 4 ча первой ячейки памяти, а выходы соединены соответственно с третьим входом переключателя и соответствующим входом ключа данной ячейки памяти, выход операционного усилителя которой соединен с входом ключа последующей ячейки памяти.

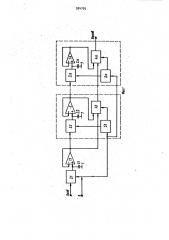

На фиг. 1 представлена функциональная схема устройства; на фиг. 2эпюры сигналов, поясняющие принцип работы предлагаемого устройства.

Устройство (фиг. 1 ) содержит операционные усилители 1.1-1,п, накопительные элементы, например конденсаторы 2.1-2.п, ключи 3.1-3.п, переключатели 4.1-4.п, расширители длительности сигнала управления 5.15.п, шина 6 управления, шина 7 нулевого потенциала и ячейки 8.1;8.п памяти.

Устройство работает следующим образом.

При наличии сигнала управления срабатывает ключ 3. 1, расширители длительности сигнала управления 5.15 il одновременно с поступлением сигнала управления выдают напряжение, открывающее ключи 3.2-3.п и переключатели 4.1-4.п переходят в положение, при котором напряжение с выхода усилителя 1.1 проходит через переключатели 4.1-4.п на выход устройства, а сигналы с усилителей

1.2-1.п на выход не проходят,,т.е. на выход проходит только сигнал, соответствующий сигналу на конденсаторе 2. 1. Накопительные конденсаторы

2.2-2.п начинают также заряжаться напряжением с выходов усилителей

1.2-1 и. Постоянная времени заряда и разряда (за счет увеличения номинального значения емкости ) каждой последующей ячейки памяти увеличивается в соответствии с увеличением длительности коммутационного сигнала на выходе соответствующего расширителя.

После окончания командного импульса сигнал с выхода усилителя 1 выдается на выход устройства, и одновременно в течение времени Т,,q-<. напряжение на конденсаторе 2.2 следит за напряжением на выходе усилителя 1.1 практически без ошибки,т.е.

U = 0<<, так как Tp+p ., T>„p После окончания действия си -нала с выхода расширителя 5.! ключ 3.2 раз5 92475 мыкается, переключатель 4.1 переключается в положение, при котором разрывается цепь прохождения сигНала с выхода усилителя 1. 1 и выдается сигнал с выхода усилителя 1.2.

При этом разряд конденсатора 2.2 происходит с постоянной времени

Т .р 2Т .<, т.е. запоминание происходит с большой точностью. На фиг.2 это соответствует времени.T eм,ь.) до Тр во. Работа. последующих ячеек памяти происходит аналогично. Из фиг. 2 видно, что точность запоминания предлагаемого устройства значительно выше, чем у известного. 35

Предлагаемое устройство выгодно отличается от известного тем, что повышается точность запоминания при большой скважности коммутационного сигнала. 20

Формула изобретения

О

Аналоговое запоминающее устрЪйство, содержащее ячейки памяти, каждая р из которых выполнена на накопительном элементе, например на конденсаторе, одна из обкладок которого сое" динена с шиной нулевого потенциала., ключе; выход которого соединен с дру- зв гой обкладкой конденсатора и неин-. ."вевтирующим входом операционного усилителя, охваченного по инвертирую. щему входу обратндй связью, и шину управления, подключенную к одному из входов ключа, о т л и ч а ющ е е с я тем, что с целью повышения точности устройства, в него в каждую ячейку памяти, кроме первой, введены расширитель длительности сигнала управления и переключатель, первый вход каждого из которых, кроме первого соединен с выходом переключателя предыдущей ячеики памяти, а вход первого переключателя соединен с выходом первого операционного усилителя, второй вход переключате" ля каждой ячейки памяти подключен к выходу операционного усилителя дам" ной ячейки памяти, вход расширителя длительности сигнала управления каждой ячейки памяти подключен к шине управления и первому входу ключа первой ячейки памяти, а выходы соединены соответственно с третьим входом переключателя и соответствующим входом ключа данной ячей-. ки памяти, выход операционного усилителя которой соединен с входом ключа последующей ячейки памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 452859, кл. G 11 С 27/ОО, .1974.

1. 333 схемы на операционных усилителях, компараторах и повторителях. Под ред. Шило В. Л., 1976, с. 73, рис. 155 (прототип ).