Устройство для контроля блоков оперативной памяти

Иллюстрации

Показать всеРеферат

(.» . аь, ..

Б. Н. Анисимов, А. К. Криворотов, О, В..» Летнев и Ю. С. IJàêàðüÿíö (72) Авторы изобретения, (7!) Заявитель г (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ОПЕРАТИВНОЙ ПАМЯТИ

Изобретение относится к запомиНаю щим устройствам.

Известно устройство, содержащее схему пуска-останова, счетчика адреса, имитаторы ввода начального адреса, количества адресов и кода числа, .схему формирования кода, адреса, схему сравнения адреса, контрольный . регистр числа, схему формирования кода числа, схему сравнения чисел, счетчик циклонов, схему сравнения циклов и схему управления кодом чисел l.t j .

Недостатками этого устройства являются сложность и невысокая достоверность контроля.

Наиболее близким к предлагаемому является устройство для контро" ля блоков оперативной памяти, содержащее первый .счетчик, регистр числа и блок управления, подключенные к выходным шинам устройства, счетный триггер, формирователь, элемент И. основные коммутаторы, полусумматор, дополнительные коммутаторы, второй и третий счетчи" ки (21 .

Недостатком этого устройства яв"

3 ляется низкая достоверность контроля, так как применяемые в нем тесты типа "Дождь" и "Адресный код" не обеспечивают полной проверки бло ка оперативной памяти, в частности динамических качеств усилителей считывания.

Цель изобретения. - повышение дос" товерности контроля.

Поставленная цель достигается тем, что в устройство для контроля оперативной памяти, содержащее блок управления, регистр числа 1 элемент

И, первый счетный триггер, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики, причем выходы первого счетчика и регистра числа, выход элемента И и первый выход блока управления являются выходами

92475 устройства, второй выход блока управления соединен с первым входом элемента И, первыми входами первого счетного триггера и формирователя им. ульсов и входами второго и третьего счетчиков, выход элемента И подключен к входу первого счетчика, один из выходов которого соединен с вторым и третьим входами первого счетного триггера, выход которого подключен к первому входу полусумматора и второму входу формирователя импульсов, выход которого соединен с вторым входом элемента

И, второй вход полусумматора подключен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов, выходы которых соединены соответственно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока управления,чет.вертый выход ко5

20 торого соединен с первыми управляющими входами основных коммутаторов, 25 вторые информационные входы которых подключены соответственно к выходам дополнительных коммутаторов, управляющие и информационные входы корого подключены к первому входу элемента И, прямой и инвереный выходы второго счетного триггера соединены соответственно с информационными входами основных коммутаторов, вторые управляющие входы которых

" подключены к другому выходу первого счетчика, третий вход формирователя импульсов соединен с одним из выходов блока управления.

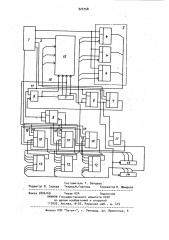

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит блок 1 управления с первым выходом 2, регистр 3 числа, выполненный на триггерах 4, первый счетчик 5, имеющий разрядность n . log Л, где А - количест2. во адресов, и предназначенный для формирования кода адреса, счетный триггер 6, формирователь 7 импульсов, второй счетный триггер 8, элемент И 9, основные коммутаторы

55

10, полусумматор 11, дополнительные коммутаторы 12, второй 13 и третий

14 счетчики. На чертеже показан торых соединены соответственно с вы- 30 ходами второго и третьего счетчиков, содержит второй счетный триггер, первый, второй и третий входы кото8 4 контролируемый блок 15 оперативной памяти. На чертеже обозначен (- -+1)и» ный выход 16 первого счетчика,соединенный со вторыми управляющими входами основных коммутаторов. .На чертеже обозначены также первый вход

17,элемента И, первые 18 и вторые

19 управляющие входы основных коммутаторов. Третий счетчик 14 имеет разрядность (и +1 ).

Устройство работает следующим образом.

Импульсы на управляющих входах 18 и 19 основных коммутаторов 1О обуславливает выбор одного из трех применяемых в устройстве контрольных тестов : "Дождь". "Адресный код" или

"IJàõìàTHûé код".Рассмотрим работу устройства в режиме формирования теста "Шахматный код". После запуска устройства блок 1 управления выдает управляющие импульсы, под воздействием которых коммутаторы 1О подключают выходы счетного триггера 8 ко входам регистра 3. Блок 1 вырабатывает тактовую последовательность импульсов, причем управляющий сигнал на третьем входе формирователя 7 обеспечивает прохождение этой последовательности импульсов через элемент

И 9 на вход счетчика 5. Во время первого такта обращения первого подцикла происходит запись кода "0" в первый адрес блока 15. Затем на выходе счетного триггера 8 появляется код "1", который записывается во второй адрес блока 15. Далее в третий адрес блока 15 записывается код "0".

Так продолжается до 2 1 адреса. Таким образом, первая строка первого канала блока 15 заполнена перемежающимися единицами и нулями. После заполнения 2 адресов на выходе 16 счетчика 5 устанавливается уровень логической "1", разрешая тем самым прохождение в следующие 2 тактов обращения импульса с инвеосного. выхода счетного триггера 8 на входы регистра 3. - Итак в течение первого подцикла каждый канал блока 15 заполнен "Шахматным кодом". Во время второго подцикла в блок 15 записыва-. ется инверсный "Шахматный код". Применение этого .кода обеспечивает. более полную проверку динамических качеств усилителей считывания блока 15 оперативной памяти.

924758

Технико-экономическое преимущество предлагаемого устройства заключается в более высокой, по сравнению с известным, достоверности контроля блоков оперативной памяти за счет. применения теста "Шахматный код" наряду с тестами "Дождь" и "Адресный код".

Формула, изобретения

Устройство для контроля блоков оперативной памяти, содержащее блок управления, регистр числа, элемент

И, первый счетный триггер, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики, причем выходы первого счетчика и регистра числа, выход элемента И и первый выход блока управления являются выходами уст-. ройства, второй выход блока управления соединен с первым входом элемента И, первыми входами первого счетного триггера и формирователя им« ,пульсов, и входами второго и треть.его счетчиков, выход элемента И подключен к входу первого счетчика, один из выходов которого соединен с вторым и третьим входами первого счетного триггера, выход которого подключен к первому входу полусумматора и второму входу формирователя импульсов, выход которого соединен с вторым входом элемента И, вто- зз рой вход полусумматора подключен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов,выходы которых соединены соответст венно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока уп- равления, четвертый выход которого соединен с первыми управляющими вхо" дами основных коммутаторов, вторые информационные входы которых подключены соответственно к выходам дополнительных коммутаторов, управляю" щие и информационные входы которых соединены соответственно с выходами . второго и третьего счетчиков о т

1 л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит второй счетный триггер, первый, второй и третий входы которого подключены к первому входу элемента И, прямой и инверсный выходы второго счетного триггера соединены соответственно с информационными входами основных коммутаторов, вторые управляющие входы которых подключены к другому выходу первого счетчика, третий вход формирователя импульсов соединен с одним из выходов блока управления.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Н 407398, кл. G 11 С 29/00, 1972.

2. Авторское свидетелвство СССР

N 547837, кл. С 11 C 29/00 1975 (прототип

924758

Составитель Т. Зайцева

Редактор Ю. Середа ТехредМ.Гергель Корректор Н. Швыдкая

Заказ 2826/69 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Н-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4