Устройство для передачи сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1924889 (61) Дополнительное w авт. свид-ву— (22) Заявлено 26. 09. 80 (21 . 2986916/18-09 с присоединением заявки №вЂ” (23) Приоритет (51)M. Кл.

Н 04 L 3/02 Ьаударстванный квинтет

СССР (53) УЛК621.394. .14(088.8) . но делам нэааретеннй н аткрытнй

Опубликовано 30,04,82„Бюллетень № 16

Дата опубликования описания 30.04.82

Е. A. Гурвиц, Е. А. Котырев, Г. А. Целибее, В, Ф. Ходов и A. Ф. Кирьяков (72) Авторы изобретения (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СИГНАЛОВ

Изобретение относится к электросвязи и может быть использовано в . устройствах передачи дискретных сигналов по кабелям связи.

Известно устройство передачи сигналов, содержащее последовательно соединенные синкрогенератор и преобразователь бинарных сигналов,,а также выходной согласующий блок(1).

Однако известное устройство обладает низкой помехоустойчивостью из-за увеличения мощности флуктуационного шума.

Цель изобретения - повышение помехоустойчивости.

Для достижения указанной цели в устройство для передачи сигналов, содержащее последовательно соединенные синхрогенератор и преобразователь бинарных сигналов, а также выходной согласующий блок, введены последовательно соединенные блок согласования и фильтр, выход которого подключен к входу выходного согласующе го блока, а выход и реоб ра зо вателя бинарных сигналов подключен к входу блока согласования. Кроме того, преобразователь бинарных сигналов содержит четыре элемента И, эле5 мент ИЛИ, последовательно соединенные инвертор и первый делитель, а также второй делитель и последовательно соединенные блок задержки и де,шифратор, выход которого подключен

1О к первым входам элементов И, при этом прямой и инверсный выходы первого делителя подключены соответст" венно к вторым входам первого и вто"

15 рого элементов И, а прямой и инверсный выходы второго делителя подключены соответственно к вторым входам третьего и четвертого элементов И, причем выходы всех элементов И подключены к соответствующим входам эле,мента ИЛИ, выход которого является выходом преобразователя бинарных

Ф сигналов, входом которого являются ,первые входы блока задержки, инверформула изобретения

3 92488 тора, второго делителя и третий вход дешифратора, а второй вход блока задержки является входом устройства.

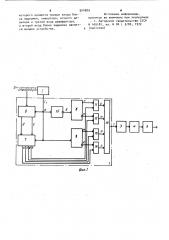

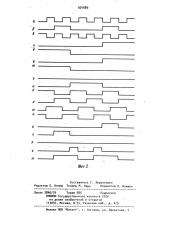

На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство передачи сигналов содержит преобразователь 1 бинарных сигнаЛов, синхрогенератор 2, блок 3 20 согласования, фильтр 4, выходной согласующий блок 5, а блок 6 задержг ки, дешифратор 7, первый делитель 8, второй делитель 9, инвертор 10, первый второй, третий и четвертый эле- 2$ менты И ll, 12, 13 и 24„ элемент

ИЛИ 15.

Устройство работает следующим образом.

С выхода источника информации на щ один вход блока 6 задержки преобразователя 1 бинарных сигналов и двухкратные биимпульсные сигналы поступает случайная последовательность бинарных сигналов (фиг.2б), на другой у$ вход которого поступает тактовая частота fr (фиг.2а) от синхрогенератора

2 с выходов первого и второго подканалов блока б задержки, задержанная информация (Фиг.2г, д соответст- yg венно) поступает на входы дешифратора

7. На выходах дешифратора 7 в зависимости от значения разрядов в дибите (00, 11, 01, 10) формируются соответственно сигналы 0001; 0010; 0100;

1000 (Фиг. 2 е, ж, з, и), которые поступают на вторые входы элементов

И 11-14.

9 4 два раза. Такое сокращение полосы

1 тракта приводит к уменьшению мощности шума вдвое и, следовательно, помехоустойчивость передаваемых сигналов на 3 дб выше. Выходной сигнал фильтра 4 через выходной согласующий блок 5, служащий для согласования с кабелем, поступает на выход устройства для передачи сигналов. !

Использование устройства повышает помехоустойчивость передачи бинарной информации за счет уменьшения полосы пропускания тракта, и следова,тельно, уменьшения мощности флуктуационного шума при сохранении заданной скорости передачи информации или дальности связи, присущей устройству для передачи однократного биимпульсного сигнала.

l. Устройство для передачи сигналов, содержащее последовательно соединенные синхрогенератор и преобразователь бинарных сигналов, а также выходной согласующий блок, о т л ич а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные блок согласования и фильтр, выход которого подключен к входу выходного согласующего блока, а выход преобразователя бинарных сигналов подключен к входу блока согласования.

Инвертированные сигналы синхро49 генератора 2 (фиг.2в) поступают на вход первого делителя 8. Сигналы с прямых и инверсных выходов первого и второго делителей 8 и 9 подаются на первые входы элементов И 11-14 (фиг.2к, л, м,н), выходные сигналы

4$ которых (фиг.2 о,п р,c) поступают на входы элемента ИЛИ 15.

На выходе элемента ИЛИ 15 формируются двукратные биимпульсные сигналы (l001, 0110, 0021, l100, фиг.2т) в зависимости ot значений разрядов в дибите (соответственно 00, 11, 01, 10). Выходные сигналы преобразователя бинарных сигналов через согласующий блок 3 поступают на вход фильтра

4 с частотой среза f, чем обеспечивается уменьшение полосы тракта в

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что преобразователь бинарных сигналов содержит четыре элемента И, элемент ИЛИ, последовательно соединенные инвертор и первый делитель, а такие второй делитель и последовательно соединенные блок задержки и дешифратор, выход которого подключен к первым входам элементов И, при этом прямой и инверсный выходы первого делителя подключены соответственно к вторым входам первого и второго элементов И, а прямой и инверсный выходы второго делителя подключены соответственно к вторым входам третьего и четвертого элементов И, причем выходы всех элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является выходом преобразователя бинарных сигналов, входом

924889 которого являются первые входы бло" ка задержки, инвертора, второго делителя и третий вход дешифратора, а второй вход блока задержки является входом устройства, 6

Источники информации, принятые во внимание при экспертизе.--1. Авторское свидетельство СССР

N 405181, кл. Н 04 L 3/00, 1972 (прототип) (Риг.!

924889 е

Ж

Составитель Г. Лерантович

Редактор Е. Кинив Техред И. Надь, Корректор Л. Бокшан

Заказ 2840/76 Тираж 685 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4