Устройство для приема самосинхронизирующейся дискретной информации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Соцналнстнчесинк

Республик 1924902 (61) Дополнительное к авт. свид-ву и 836814 (51) М. Кл. (22) Заявлено 08. 09. 80 (21) 2995229/18-09 с присоединением заявки М— (23) Приоритет

Н 04 1., 17/16

Н 04 L 7/06 фпудеретеаииый комитет

СССР

Опубликовано 30 ° 04 82 ° бюллетень М16 ао делам изобретений и открытий ( (53) УДК 621 ° 394 .662(088.8)

Дата опубликования описания 30.04.82 (72) Авторы изобретения

В

П.М. Иванов И.И. Гридякин, П.Г. Тесля и Н.е. Тхйаев

1::„, Кабардино-Балкарский филиал Проектно-техн логического обьединения по внедрению автоматизированных систем управления "Россельхозтехсистема" (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА САМОСИНХРОНИЗИРУЮЩЕЙСЯ

ДИСКРЕТНОЙ ИНФОРМАЦИИ

Изобретение относится к технике передачи дискретной информации и может быть применено в системах передачи данных, использующих асинхронный принцип.

По основному авт. св. 11 836814 известно устройство для приема самосинхронизирующейся дискретной информации, содержащее последовательно соединенные блок .обработки сигнала, элемент памяти, регистр сдвига, блок коммутации и декодер, а также последовательно соединенные приемник, накопитель и селектор синхросигнала, .выход которого подключен к разрешающему входу блока коммутации, при этом обьединенные входы приемника и блока обработки сигнала являются входом устройства.

Однако известное устройство обла" дает, низкой помехоустойчивостью, обусловленной значительным числом. необнаруживаемых ошибок.

Цель изобретения - повышение помехоустойчивости.

Для достижения укаэанной цели в устройство введены три.временных селектора, два инвертора, элемент

И, дополнительный элемент памяти, элемент задержки и элемент ИЛИ, выход которого подключен ко входу записи дополнительного. элемента памяти, ко входу стирания которого

1О через элемент задержки подключен выход селектора синхросигнала, а вы/ход дополнительного элемента памяти подключен к запрещающему входу блока коммутации, при этом выходы блока

l5 обработки сигнала через первыи и второй временные селекторы, а также через первый и второй инверторы подключены соответственно к первому и второму входам элемента ИЛИ и

20 первому и второму входам элемента И, выход которого через третий временной селектор подключен к третьему входу элемента ИЛИ.

902

3 924

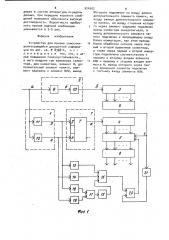

На фиг. 1 приведена структурная электрическая смема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство для приема самосинх5 ронизирующейся дискретной информации содержит блок 1 обработки сигнала, приемник 2, накопитель 3, регистр

4 сдвига, блок 5 коммутации, селектор 6 синхросигнала, элемент 7 па-. мяти, декодер 8. Приемник 2 состоит из блока 9 выделения значащих характеристических моментов восстановления (3XH8) сигнала и формирователя 10 импульсов заданной длительности, блок 1 обработки сигнала состоит из селектора 11 положительных посылок и селектора 12 отрицательных посылок. Устройство включает также первый, вторсй и третий временные селекторы 13, 14 и 15, элемент ИЛИ 16, элемент И 17, первый и второй инверторы 18 и 19, дополнительный элемент 20 памяти и элемент 21 задержки.

Устройство работает следующим образом.

Самосинхронизирующаяся импульсная троичная последовательность fZ;1 (фиг. 2), сформированная на передатчике из двоичной последовательности А;) по следующему закону:

Е =ХХ-У, Х =A Х„1, Y -— А Y „q, ХОУ0 0 (индекс соответствует порядковому номеру значащего характеристического момента модуляции передаваемого сигнала, к=1), поступает на входы приемника 2 и блока 1 обработки сигнала (фиг. 2с1), В блоке 9 выделения ЗХМВ сигнала приемника 2 происходит выделение фронтов приходящего

I сигнала, которые подаются на вход формирователя 10 импульсов заданной длительности (фиг. 25). С помощью формирователя 10 импульсов заданной длительности по ЗХИВ формируются импульсы заданной длительности, которые подаются на вход накопителя 3 (фиг. 2Ь). При окончании записи рабо чей кодовой комбинации в накопитель

3 селектор 6 синхросигнала фиксиру-, ет ее и выдает на вход блока 5 коммутации сигнал разрешения выдачи информации (фиг..21.), записанной в регистре 4 сдвига. Блок обработки сигнала выделяет в принимаемой последовательности положительные и отрицательные посылки. На входе селектора 11 положительных посылок импульс (фиг. 23) появляется при наличии положительной посылки в самосинхронизирующейся последовательности, а на выходе селектора 12 отрицательных посылок (фиг. 2 p) — при наличии отрицательной посылки. Сигналы с выходов селекторов 11 и 12 положительных и отрицательных посылок поступает соот/ ветственно на S-. и R-входы элемента

7 памяти, выполненного на RS-триггере, где преобразуются в двоичную информационную последовательнос-,ь.

Одновременно сигналы с выходов блока 1 обработки сигнала поступают на входы первого и второго временных селекторов 13 и 14 и на входы первого и второго инверторов 18 и 19. С выходов первого и второго инверторов

18 и 19 сигналы через элемент И 17 поступают на вход третьего временного селекгора 15. Первый, вторсй и третий временные селекторы 13, 14 и

15 срабатывают в том случае, если длительность соответственно положительной, отрицательной или нейтральной (нулевой) посылки меньше заданного времени селекции, что с большей вероятностью приводит к ошибке.

При срабатывании любого из воеменных селекторов 13, 14 или 15 сигнал с выхода сработавшего временного селектора через элемент ИЛИ 16 поступает на вход записи дополнительного элемента 20 памяти. В этом случае с выхода дополнительного элемента 20 памяти на запрещающий вход блока 5 коммутации выдается сигнал блокировки, по. которому кодовая комбинация из регистра 4 сдвига не передается в декодер 8. Сброс дополнительного элемента 20 памяти (возврат в исходное состояние) производится по сигналу от элемента 21 задержки, который запускается задним фронтом синхросигнала, поступающего от селектора 6 синхросигнала.

С выхода элемента 7 памяти, двоичная информация (фиг. 2 ) последовательно поступает на вход регистра 4 сдвига. По сигналу с выхода селектора 6 синхросигнала эта информационная последовательность через блок

5 коммутации поступает в декодер 8, где преобразуется в знак сообщения.

Таким образом, предлагаемое устройство для приема самосинхронизирующейся дискретной информации, входящее в состав аппаратуры передачи данных, при передаче коротких сообщений позволяет обеспечить высокую достоверность. Вероятность ошибочного приема кодовой комбинации . уменьшается в 2-5 раз.

Формула изобретения

Устройство для приема самосинхронизирующейся дискретной информации по авт. св. Р 836814, о тл и ч а ю щ е е с я тем, что, с це лью повышения помехоустойчивости,. в него введены три временных селектора, два инвертора, элемент И, дополнительный элемент памяти, элемент задержки и элемент ИЛИ, выход

924902 6 которого подключен ко входу записи дополнительного элемента памяти, ко входу записи дополнительного элемента памяти, ко входу стирания которо-! го через элемент задержки подключен выход селектора синхросигнала, а выход дополнительного элемента памяти подключен к запрещающему входу блока коммутации, при этом выходы

10 блока обработки сигнала через первый и второй временные селекторы, а также через первый и второй инверторы подключены соответственно к первому и второму входам элемента

15 ИЛИ и первому и оторому входам эле" мента И, восход которого через третий временной селектор подключен к третьему входу элемента ИЛИ.

924902

Составитель Г. Лерантович

Редактор И. Михеева Техред С.Мигунова Корректор С. Щомак

Заказ 2 1/77 Тира)н 5 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открцтий

113035, Москва N-35 Раушская наба р л. 4/5 илиал llllll "Патент, г. Уагороа, ул. Ороектиал, И