Частотно-импульсное множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (f ! (= = и. ° .р ю.% .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву 9 278233 (22) Заявлено 281279 (21) 2862969/18-24 (51 ) М. Кл.

G G 7/16

G 06 F 7/68 с присоединением заявки № (23) Приоритет

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 070582, Бюллетень ¹17 (531 УДК 681. 335. 5 (088.8) Дата опубликования описания 07.05.82 т (72) Авторы изобретения

О.М.Доронина и М.Г.Рылик

1 к

1 г т

Слениалэное констрниторское бюро микроэлектроники в приборостроении (71) Заявитель (54) ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ

УСТРОЙСТВО

Гъ

Изобретение относится к автоматике, вычислительной и измерительной технике, предназначено для перемножения величины, заданных частотой следования импульсов.

По основному авт. св. Р 278233 известно частотно-импульсное множительио-делительное устройство, со-. держащее счетчики, регистр, схемы запрета и устройство задержки, в котором производится преобразование частот Г,, Г, F в выходную частоту Г,, по формуле

В этом устройстве первый вход устройства (пс. которому поступают импульсы с ч-"стотой F ) соединен с информационными входами схем запрета первой группы, управляющие входы которых соединены с разрядными выходами первого счетчика, а выходы соединены с разрядными входами регистра, разрядные выходы регистра соединены с управляющими входами схем запрета второй группы, информационные- входы которых соединены с выходом второго счетчика, счетный вход которого соединен со вто- рым входом устройства (но которому поступают импульсы с частотой F ), а разрядные входы соединены с выходами схем запрета второй группы.

Первый вход устройства через устройство задержки соединен с цепью сброса первого счетчика, на счетный вход. которого поступают импульсы с часто той Г . Выход второго счетчика яв-. ляется вЫходом устройства (1).

Недостатком известного устройства является малая выходная частота по сравнению с частотами сомножителей, которая приводит к низкому быстродействию устройства и большой динамической погрешности, возникающей в результате потери информации о периодах частоты первого сомножителя и делителя.

Цель изобретения — уменьшение динамической погрешности и повышение быстродействия устройства.

Поставленная цель достигается тем, что частотно-импульсное множи25 телку=делительное устройство дополнительно содержит второй регистр, третий счетчик, третью и четвертую группы .схем запрета, второе устройство задержки и элемент ИЛИ, причем

ЗО второй вход устройства соединен. со

926672 счетным входом третьего счетчика, разрядные выходы которого соединены с информационными входами схем запрета третьей группы,. управляющие входы которых соединены с разрядными выходами второго регистра, а выходы — co входами элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, разрядные выходы третьего счетчика соединены с управляющими входами схем запрета четвертой группы, выходы которых соединены с разрядными входами второго регистра, а информационные входы соединены с третьим входом устройства, который через второе устрой-!5 ство задержки соединен с цепью сброса третьего счетчика.

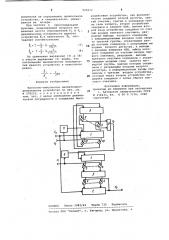

На чертеже представлена блок-схема устройства.

Частотно-импульсное множительно- 20 делительное устройство содержит счетчики 1 и 2, схемы 3 и 4 запрета, регистр 5, устройство 6 задержки, счетчик 7, регистр 8, схемы 9 и 10 запрета, устройство 11 задержки, элемент

ИЛИ 12.

На входы счетчиков 2 и 7 поступает частота Fq . Вход устройства, на который поступает частота F< через устройство 11 задержки соединен с цепью сброса счетчика 7, разрядные выходы которого соединены с информационными входами схем 9 запрета и управляющими входами схем 10 запрета. Информационные входы схем 10 запрета соединены со входом устройства, на который поступает частота

F, а выходы соединены с разрядными входами регистра 8, разрядные выходы которого соединены с управляющими входами схем 9 запрета, выходы которых подключены ко входам элемента

ИЛИ 12, выход которого соединен со счетным входом счетчика 1, разрядные выходы которого соединены с управляющими входами схем 3 запрета, инфор- 45 мационные входы которых соединены со входом устройства, на который поступает частота F этот вход через устройство 6 задержки соединен с цепью сброса счетчика 1, выходы схем 5О

3 запрета соединены с разрядными входами регистра 5, разрядные выходы которого соединены с управляющими входами схем 4 запрета, выходы которых соединены с разрядными входами счетчика 2, счетный вход которого соединен сс входом устройства, на который поступает частота F, а выход, на котором формируется выходная частота Г„, соединен с инфор- 60 мационными входами, схем 4 запрета.

Устройство работает следующим образом.

При поступлении на вход устройства очередного импульса входного сиг- 65 нала F число иэ счетчика 7 переносится в регистр 8, а сам счетчик 7 через время, определяемое устройством

11 задержки, сбрасывается в ноль.

Так как Г,=, то за время Т в =)

Т5/ счетчике 7 накопится число импульсов N, поступивших с частотой.следования F

N = Г, Т, (2)

Счетчик 7, регистр 8, схемы 9 запрета и элемент ИЛИ 12 составляет двоичный умножитель, на выходе которого формируется частотно-импульсная последовательность с частотой - следования импульсов F

Ns F> (3)

Ы, = Т,.F . (4)

Счетчик 2, регистр 5 и схемы 4 запрета образуют управляемый делитель частоты F,,на выходе которого формируется частотно-импульсная последовательность с частотой следования импульсов

)) (5) а с учетом выражений (1), (3) и (4) . л 2"

Г„= Г Г.

Данное устройство имеет более высокое быстродействие по сравнению с известным и выполняет операцию умножения со значительно меньшей динамической погрешностью.

Увеличение частоты выходной частотно-импульсной последовательности

F, а следовательно, и быстродействия достигается за счет того, что соотношение- выходных частот данного устройства и известного как видно из сравнения формул (1) и (5), составляет

Fk ч — 2

Fq (6) Увеличение частоты выходного сигнала в данном устройстве по сравнению с выходной частотой известного приводит также к уменьшению его динамической погрешности, так как при этом увеличивается частота поступления информации и периодах частот-сомгде n — число двоичных разрядов счет. чиков и регистров устройства. Последовательность импульсов с частотой

F поступает на вход счетчика 1.

При поступлении на вход устройства очередного импульса входного сигнала F число иэ счетчика 1 обратным кодом переносится в регистр 5, а сам счетчик 1 через время, определяемое устройством 6 задержки, сбрасывается в ноль. Так как,= вЂ, то за время Т, 1

Т в счетчик 1 проходйт число импульсов 1) 926672

2г а

Формула изобретения

ВПИИПИ Заказ 2983/42 Тираж 732 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 ножителей на управляемое делительное устройство, а следовательно, уменьшаются ее потери.

При частоте (, синусоидальной функции, моделирующей скорость изменения частот сомножителей F F

5 динамические погрешности данного устройства 5„ и известного 8 составляют соответственно (+ 1 о 1

2 (Г,, ) (7) (8)

Из сравнения выражений (7) .и (8) с учетом выражения (6) видно, что соотношение динамических погрешностей данного устройства и известного равно:

Частотно-импульсное множительноделительное устройство по авт. св.

Р 278233, о т л и ч а ю ш е е с я тем, что, с целью уменьшения динамической погрешности и повышения быст родействия устройства, оно дополнительно содержит второй регистр, третий счетчик, третью и четверную груп пы схем запрета, второе устройство задержки и элемент ИЛИ, причем второй вход устройства соединен со счет ным входом третьего счетчика, разрядные выходы которого соединены с информационными входами схем запре та третьей группы, управляющие входы которых соединены с разрядными вы ходами второго регистра, а выходы с входами элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, разрядные выходы третьего счетчика соединены с управ1С ляющими входами схем запрета четвертой группы, выходы которых соединены с разрядными входами второго регистра, а информационные входы соединены с третьим входом устройства, 2О который через второе устройство задержки соединен с цепью сброса тре— тьего, счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 278233, кл. G 06 G 7/16, 1968 (прототип).