Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиих

Соцмалмстмчесимх

Республик

< 1926725 (61) Дополнительное к авт. свнд-ву (22) Заявлено 050580 (21) 2920812/18-24 (51) М. Кл.

Ci 11 С 2Ч/00 с присоединением заявки №

РВудаРстак««ьй «ам«тат

СССР лв делаю «эабвете«к« в открыт«й (23) Приоритет

Опубликовано 070582. Бюллетень № 17

Дата опубликования описания 070582 (53) УДК681.327 °.6(088.8) А. Н. Иванов, А. Н. Поскребышев, В. М. и И. В. Огнев (72) Авторы изобретения (7l) Заявитель (54} УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

Изобретение относится к запоминающим устройствам (ЗУ), в частности к устройствам контроля ЗУ.

Известно устройство контроля ЗУ, содержащее блоки формирования контрольных кодов Г1 J.

Наиболее близким к предлагаемому является устройство для контроля .запоминающих модулей, содержащее регистр сдвига, регистр начального состояния, сумматоры по модулю два, ин î формационный регистр, схему контроля, регистр адреса, регистры маски и схемы И.

Известное устройство реализует

15 линейные и нелинейные коды, что позволяет существенно увеличить число проверочных тестов (23.

Недостатками известных устройств являются сложность и малое быстродействие при формировании тестов, что делает невозможным контроль ЗУ на предельных частотах обращения.

Цель изобретения - повышение бы- стродействия устройства для контроля блоков памяти.

Поставленная цель достигаетс тем, что в устройство для контроля блоков памяти, содержащее формирователь эталонов, входы которого подключены к группе выходов узла управления, сдвиговый регистр, управляющий вход которого подключен к первому выходу узла управления, схему сравнения, выходы которой подключены к входам узла управления, а одни входы схемы сравнения являются входами устройства, дополнительно введены элементы

ИСКДОЧАЮЦЕЕ ИЛИ, одни входы которых подключены к выходам формирователя эталонов, другие входы - к одним выходам сдвигового регистра, а выходы элементов,ИСКЛ0ЧАЮЦЕЕ ИЛИ подключены к другим входам схемы сравнения и являются выходами устройства, и триггер, один вход которого подключен к другому выходу сдвигового ре3 92 гистра, другой вход - к второму выходу узла управления, а выход триггера подключен к информационному вхо. ду сдвигового регистра.

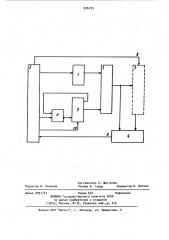

Блок-схема устройства для контроля блоков памяти приведена на чертеже.

-Устройство содержит формирователь

1. эталонов, сдвиговый регистр 2, элементы ИСКЛЮЧАЮЦЕЕ ИЛИ 3, схему 4 срав нения, узел 5 управления, триггер 6, контролируемый блок 7 памяти, управляющие входы 8 блока памяти, выходы

9 схемы сравнения и управляюцие входы 10 сдвигового регистра.

Устройство работает следующим образом.

Первоначально по сигналу с блока

5 управления на элементы ИСКЛЮЧАЮЦЕЕ

ИЛИ 3 поступает нулевой код эталона с формирователя 1 эталонов и нулевой код сдвигового регистра 2. Код элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 записывается по всем адресам контролируемого блока памяти(коды адреса и сигналы управления для блока памяти формиру» ет узел управления). Затем производится цикл считывания и сравнения информации по всем адресам схемой 4 сравнения. Результат сравнения с выходов 9 поступает в узел 5 управления. При отсутствии несравнения узел

5 управления сигналом, поступающим на вход 10, сдвигает код cäâèãoBîãî регистра 2. При этом в его нулевой разряд записывается единица., Далее повторяется запись кода с элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ 3 по всем адресам блока памяти, а затем считывание и сравнение в схеме 4 сравнения. Наличие в одном из разрядов кода, считанного из блока памяти единичной информации, отличной от нулевой информации всех остальных разрядов, позволяет при считывании и проверке выявить их взаимное влияние. Затем производится новый сдвиг кода регистра сдвига, при этом единицы записываются в нулевой и первый разряды, что позволяет при записи, считывании и сравнении определить взаимное влияние этих разрядов и всех остальных. Циклы записи, считывания и сравнения при нулевом эталоне повторяются до тех пор, пока сдвиговый регистр 2 полностью не заполнится единицами °

Последний его разряд подключен к входу триггера 6. По сигналу на входе 10 с узла управления производится запись

6725 4

10

25 изобретения.

Формула

55 единичной информации последнего разряда сдвигового регистра 2 в триггер 6. После этого производится контроль блока памяти при последователь. ном заполнении разрядов нулями на фо. не всех единиц, а формирователь 1 эталонов формирует в первый цикл записи и считывания по всем адресам по-. следовательность кодов, соответствующую изменению 0-го разряда адреса, во втором цикле последовательность кодов, соответствующую изменению 1-го разряда адреса и т.д. в цикле и-ro разряда адреса (где и = lop È, Мемкость контролируемого блока памяти.

Для подготовки кода, записываемого в блок памяти, достаточно одного такта сдвигового регистра 2 или одного такта формирователя 1 эталона.

Быстродействие устройства увеличивается, так как не используются такты пересылки эталонного кода между регистрами, суммирование по модулю два и т.п.

Устройство для контроля блоков памяти, содержащее. формирователь эталонов, входы которого подключены к группе выходов узла управления, сдвиговый регистр, управляюций вход кото" рого подключен к первому выходу узла управления, схему сравнения, выходы которой подключены к входам узла управления, а одни входы схемы сравнения являются входами устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит элементы ИСКЛЮЧАЮЦЕЕ ИЛИ, одни входы которых подключены к выходам формирователя эталонов, другие входы - к одним выходам сдвигового регистра, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к другим входам схемы сравнения и являются выходами устройства, и триггер, один вход которого подключен к другому выходу сдвигового регистра, другой вход - к второму выходу узла управления, а выход триггера подключен к информационному входу сдвигового регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССP

N 526952, кл. G ll С 29/00, 1975.

2, Авторское свидетельство СССР

М 428455, кл. G 11 С 29/00, 1972 (прототип).

926725

Составитель С. Шустенко

Техред И. Гайду Корре ктоp И. Немчик.

Редактор И. Михеева

Заказ 2991/45

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д. 4/5