Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ()926768

ИЗО6РЕТЕН ИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеез Советенм«

Сецмаектмчаекнк т ееяубянк (б!) Йонолннтельное к авт. свнд-ву(22)Заявлено 04.01.80 (2I) 2862677/18-09 (51}М. Кл.. с ярнсоеднненнею заявкн М (23)ПрнорнтетH 03 4 7/00

9вударвтеивж «еаетет

Иь.р в деваю неФретевка в еткрыт«1

Онублнковано 07. 05, 82.Бюллетень М 17

Дата ояублнковання оннсання 09. 05.82 (53) УДК 621 ° 373..42(088.8) 1

l0. Г. Покроев и Л. Г. Сир -ина

I 1

i o (72},Авторы изобретен ня

Минское производственное обьедийение-" нт (7t} Заявнтель (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

Изобретение относится к радиотех,нике и может использоваться при изме" рении параметров интегральных схем и приемо-передающих устройств..

Один из известных цифровых синтезаторов частот содержит опорный генератор, делитель частоты с постояиньк» коэффициентом деления, испульсно-фа-зовый детектор, а также блок набора частоты, блок грубой установки частоты, перестраиваемый генератор и реверсный генератор ступенчатого напряжения 01.

Однако быстродействие данного цифрового синтезатора частот невысоко.

Наиболее близким по технической сущности к предлагаемому является цифровой синтезатор частот, содержащий.последовательно соединенные опорный генератор, делитель частоты с . постоянным коэффициентом деления и импульсно"фазовый детектор, последовательно соединенные блок набора час тоты, блок грубой установки частоты, перестраиваемый генератор и делитель частоты с переменным коэффициентом деления, выход которого соединен с другим входом импульсно-фазового детектора, а также последовательно включанные цифроаналоговый преобразова" тель и фильтр нижних частот, выход которого соединен с вторым входом пе" рестраиваемого генератора, при этом второй выход блока набора частоты соединен с управляющим входом делителя частоты с переменным коэффициентом деления 21.

Однако и этот цифровой синтезатор частот имеет недостаточное быстродействие.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в известном цифровом синтезаторе частот между выходом делителя часто". ты с постоянным коэффициентом деления и входом цифроаналогового преобразователя введены последовательно соединенформула изобретения

Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, делитель частоты с постоянным коэффициентом деления и импульсно-фазовый детектор, последо" вательно соединенные блок набора частоты, блок грубой установки частоты, перестраиваемый генератор и делитель частоты с перемениым коэффициентом деления, выход которого соединен с

3 92676 ные распределитель импульсов и ре-, гистр набора кода, другой вход кото-. рого подключен к выходу импульсно-фазового детектора, при этом выход делителя частоты с постоянным коэффициS ентом деления соединен также с входом начальной установки делителя частоты с переменным коэффициентом деления.

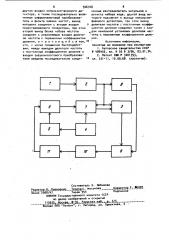

На чертеже представлена структурная электрическая схема предлагаемого синтезатора.

Цифровой синтезатор частот содер-! жит опорный генератор 1, делитель 2 частотй с постоянным коэффициентом де15 ления, импульсно-фазовый детектор 3, блок 4 набора частоты, блок 5 грубой установки частоты, перестраиваемый генератор 6, делитель 7 частоты с переменным коэффициентом деления, распределитель 8 импульсов, регистр

9 набора кода, состоящий из и триггеров, цифроаналоговый преобразователь (Ц/ П) 10 и фильтр 11 нижних частот.

Синтезатор работает следующим образом.

В исходном состоянии на блоке 4 устанавливается код требуемого значения частоты. Этот код поступает на блок 5, который формирует значение управляющего напряжения, величины емкости конденсатора или другого физического параметра, с помощью которого осуществляется выбор диапазона работы перестраиваемого генератора 6, т,е. производится его грубая настрой35. ка. Одновременно с занесением кода в блок 4 заносится началЬный код в распределитель 0 и в регистр 9. (Цепи занесения начального кода в распределитель 8 и регистр 9 на чартеже о не показаны).

В качестве начального кода регистра 9 выбран код 100... О, т.е. единица записана в старший разряд, а в остальные - нули. Этот код,преобразованный ЦАП 10 в аналоговую величину напряжения, через фильтр 11 поступает на вход перестраиваемого генератора 6, который под воздействием управляющего напряжения начинает генерировать некоторую частоту, лежащую в выбранном диапазоне частот. Эта частота делится делителем 7 частоты, коэффициент деления которого задается блоком 4, а его синхронизация осуществляется импульсами, поступающими с делителя 2 частоты. Сигналы с выходов делителей 2 и 7 частоты поступа3 ф ют на входы импульсно-Фазового детектора 3, который в зависимости от соотношения длительностей, поступающих на его входы импульсов, формирует на своем выходе, например, единичный уровень, если длительность импульса, поступающего с делителя 7 частоты, меньше длительности импульса, поступающего с делителя 2 частоты, либо нулевой уровень при противоположном соотношении длительности поступающих на его входы импульсов. Сигнал с выхода импульсно-фазового детектора 3 поступает параллельно на управляющие входы регистра 9.

По окончании первого импульса, снимаемого с делителя 2 частоты,.второй триггер регистра 9 устанавливается в единичное состояние, а первый триггер переписывает на свой выход уровень, снимаемый с импульсно-фазового детектора 3, и в дальнейшем своего состояния менять не будет.

По окончании следующего импульса, поступающего с делителя 2 частоты на вход распределителя 8, третий триггер регистра 9 устанавливается в единичное состояние, а второй триггер, аналогично рассмотренному выше случаю, перепишет на свой выход уровень напряжения, снимаемого с импульсно-фазового детектора 3, и в дальнейшем своего состояния менять не будет.

Аналогично устанавливаются в заданное состояние третий и все остальные триггеры регистра 9.

Число циклов подстройки перестраиваемого генератора 6 равно числу триггеров регистра 9. С каждым циклом uac" тоты перестраиваемого генератора 6 " ступенчато приближается к набранной на блоке 4 частоте.

Таким образом, предлагаемый синтезатор имеет значительный выигрыш в быстродействии.

3 926768 Ь другим входом импульсно-фазового де- ненные распределитель импульсов и тектора, а также последовательно вклю- регистр набора кода, другой вход коченные цифроаналоговый преобразова- торого подключен к выходу импульсно" тель и фильтр нижних частот, выход фазового детектора, при этом выход которого соединен с вторым входом S делителя частоты с постоянным коэффиперестраиваемого генератора, при этом циентом деления соединен также с вхо" второй выход блока набора частоты .,дом начальной установки делителя час" ь соединен с управляющим входом делите- тоты с переменным коэффициентом делеля частоты с переменным коэффициентом ния. деления, о т л и ч а е шийся тем, В Источники информации, что, с целью повьыения быстродейст" принятые во внимание при экспертизе . вия, между выходом делителя частоты 1. Авторское свидетельство СССР с постоянным коэффициентом деления и и 486450, кл. Н 03 8 3(06, 03.01-74. входом цифроаналогового преобразова- 2. Патент СВА 1 3401353, теля введены последовательно соеди- > кл. 331-11, 10.09.68. (прототип).

Составитель Е. Лобимова

Редактор В. Пилипенко Техред С. Иигун рре Фомак

Заказ 2998/47 Тираж 954 Подписное

8НИИПИ Государственного комитета СССР по делам изобретений и открытий

«1ЦОЯ Иосква N" ß «Раушская наб, g, Д»

4Д

Филиал ППП "Патент", г. Ужгород, ул. Проектнал,