Частотный дискриминатор

Иллюстрации

Показать всеРеферат

Союз Советски к

Социалистические

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 11. 04. 80 (21) 2910159/18-09 с присоелинением заявки Ж— (23) Приоритет (5l)M. Кл.

С 01 S 13/58

Н 03 П 13/00

3Ьеударимииый кеиитет ао делам иаебретеиий и открытий

Опубликовано 15 05 82 Бюллетень М 18

Дата опубликования описания 15.05.82 (53) УДК 621.396.

° 96(088.8) (72) Авторы изобретения

Д.И.Попов и О.В.Петрищев

/:

f л

Рязанский радиотехнический институт. (71) Заявитель (54) ЧАСТОТНЫЙ ДИСКРИМИНАТОР

Изобретение относится к радиолокации и технике связи и может использоваться в устройствах измерения частоты радиоимпульсных сигналов, отраженных от протяженных обь5 ектов, например метеообраэовании.

Известен частотный дискриминатор, содержащий ограничитель, генератор, фазовращатель и первый и второй каналы каждый иэ которых содержит . 7

1О первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок памяти, второй перемножитель и блок сложения, при этом выход ограничителя соединен с первыми входами фазовых детекторов первого и второго каналов, выход генератора соединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом фазового детектора первого канала— через фазовращатель, выход блока памяти первого канала соединен через.первый перемножитель первого канала с вторым входом блока сложения второго канала, а выход блока памяти второго канала соединен через первый перемножитель второго канала с вторым входом блока сложения первого канала 311.

Однако известный частотный дискриминатор имеет низкую чувствительность.

Цель изобретения - увеличение чувствительности.

Для достижения цели в частотный дискриминатор, содержащий ограничитель, генератор, фазовращатель и первый и второй каналы, каждый из которых содержит первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок памяти, второй перемножитель и блок сложения, при этом выход ограничителя соединен с первыми входами фазовых детекторов первого и второго

92827 каналов, выход генератора соединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом Фазового детектора первого канала - через фазовращатель, выход блока памяти nepeot-o канала соединен через первый перемножитель первого канала с вторым входом блока сложения второго канала, а выход блока памяти второго канала соединен через первый перемно-. житель второго канала с вторым входом блока сложения первого канала, введены первый и второй регистры числа, блок вычитания, а в каждый

I канал - первый блок вычитания, блок объединения и последовательно включенные второй и третий блоки вычитания, при этом в каждом канале одноименные входы блока сложения и второго блока вычитания соединены между собой, выход блока сложения соединен с входом накопителя через последовательно включенные первый блок вычитания и блок объединения, выход аналого-цифрового преобразователя соединен с вторыми входами первого и третьего блоков вычитания, выходы накопителей первого и второго каналов соединены с одноименными входами блока вычитания, выход третьего блока вычитания первого канала соединен с вторым входом блока объединения второго канала, выход третьего блока вычитания второго канала соединен с вторым входом блока объедине35 ния первого канала, а вторые входы одноименных перемножителей каждого канала соединены между собой и с выходом одноименного регистра числа.

4о

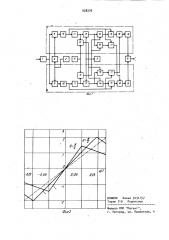

На фиг. 1 приведена структурная электрическая схема устройства, на фиг. 2 — статическая характеристика предложенного устройства (ь Т- нормированная величина расстройки частоть ) .

Частотный дискриминатор содержит ограничитель 1, генератор 2, фазовращатель 3, первый и второй регистры 4 и 5 числа, блок 6 вычитания, первый и второй каналы 7 и 8, каждый из которых содержит фазовый детектор 9, аналого-цифровой преобразователь 10, блок 11 памяти, первый перемножитель 12, второй перемножитель 13, блок 14 сложения, первый, второй и третий блоки 15-17 вычитания, блок 18 объединения и накопитель 19.

6 4

Частотный дискриминатор работает следующим образом.

Сигналы от протяженных объектов с несущей частотой F поступают на вход ограничителя 1, в котором происходит сжатие динамического диапазона исходных сигналов. Квадратурные составляющие сигнала с выхода фазовых детекторов 9 поступают в аналогоцифровые преобразователи 10, где квантуются по времени. и амплитуде.

При этом на вторые входы Фазовых детекторов 9 от генератора 2 непосредственно и через фазовращатель 3 поступает сигнал опорной частоты 1о

Задержанные в блоках 11 памяти на интервал Т цифровые коды квадратурных составляющих х 1(первый канал 7), к-i второй канал 8) поступают на первые входы первого и второго перемножителей 12 и 13. В первом и втором регистрах 4 и числа хранятся значения соответственно sin 8 и соз9

В результате выполнения операций в первом и втором перемножителях 12 и 13 и блоке 14 сложения и втором блоке 16 вычитания происходит двумерный поворот квадратурных составляющих на углы - 8 и > 8 . В первом и третьем блоках 15 и 17 вычитания данные составляющие вычитаются из незадержанных квадратурных составляющих х и у, поступающих непосредственно с выходов аналого-цифровых преобразователей 10. В результате на входах каждого блока 18 объединения образуются соответственно величины

Ок =Хк-(х -1 cOs 8 Ц к-q s1n 8), l3« =ц,-(м„- еоз8-х<-1s)n8) для первого канала 7 и

Ок »= Х<- (Хк-t 00sS — цк- $1пЭ), OK2, - 9к-(чк-1 с039 + х к-4 6!<8) для второго канала 8.

В блоках 18 объединения осуществляется вычисление величины Ек*, вттк, рк, для первого квнвлв, и Е» ГО О ка для второго канала 8. В накопителях

19 производится накопление данных с Х смежных элементов разрешения по дальности, что позволяет сгладить флюктуации поступающих сигналов и снизить влияние внутренних шумов приемника. После вычитания на выходе блока 6 образуется величина А =Ьщ, 5 9282 которая завис11т от величины

3 расстройки

Статическая характеристика дискриминатора имеет вид

А 2.Ща1яфИ 7+@ ))- )Sin(fta9 1 - )!)

Характеристики предложенного дискриминатора при №1 приведены на фиг.2. Пунктирная прямая соответствует известному устройству. 1О ! (рутизна характеристики предложенного частотного дискриминатора в пределах линейного участка в 1,41,8 раза выше,. чем у известного,что эквивалентно соответствующему повыше- 15 нию чувствительности. зо

Формула и зобрет ения

Частотный дискриминатор, содержащий ограничитель, генератор, фазовращатель и первый и второй каналы, каждый из которых содержит первый перемножитель, накопитель и последовательно включенные фазовый детектор, аналого-цифровой преобразователь, блок памяти, второй перемножитель и блок сложения, при этом выход ограничителя соединен с первыми входами фазовых детекторов первого и второго каналов, выход генераторасоединен с вторым входом фазового детектора второго канала непосредственно, а с вторым входом фазового детектора первого канала - через фазовращатель, выход блока памяти первого канала соединен через первый перемножитель первого канала с вторым входом блока сложения второго

76 G канала, а выход блока памяти второго канала соединен через первый пере1 множитель второго канала с вторым входом блока сложения первого канала, отличающийся тем, что, с целью увеличения чувствительности, введены первый и второй регистры числа, блок вычитания, а в каждый канал — первый блок вычитания, блок объединения и последовательно включенные второй и третий блоки вычитания, при этом в каждом канале одноименные входы блока сложения и второго блока вычитания соединены между собой, выход блока сложения соединен с входом накопителя через последовательно включенные первый блок вычитания и блок объединения, выход аналого-цифрового преобразова2О теля соединен с вторыми входами первого и третьего блоков вычитания, выходы накопителей первого и второго каналов соединены с одноименными входами блока вычитания, выход третьего блока вычитания первого канала соединен с вторым входом блока объединения второго канала, выход третьего блока вычитания второго канала соединен с вторым входом блока объединения первого канала, а вторые входы одноименных перемножителей каждого канала соединены между собой и с выходом одноименного регистра числа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 687941, кл. С 01 $ 7/36, 19.09.77 (прототип) .