Усилитель считывания для интегрального запоминающего устройства

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АЗТОРСМОМУ СВИДЕТЕЛЬСТВУ

Союз Советснмк

Соцналнстнчвсннк расаубпттм iii 928405

4 (б1) Дополнительное к авт. свнд-ву (22) Заявлено 05.08.76 (2l ) 2393457/1 8-24 с присоединением заявки М (23) П рнорнтет (5 3 ) M. Кл. (; 11 С 7/00

q 11 С 11/40

9вудврстмаай камктет

eCCl ае делам взо4рвтенкй к вткуытв1

Опубликовано 15.05.82. Бюллетень ¹ 18 (53) УДК 681. .327.66 (088.8) Л,ата опубликования описания 17.05.82! ф е »

Фь" Ъ:::

ХНФЮК! -::. (72) Авторы изобретения

10. В. Минков и В. И. Соломоненкс (7l ) Заявитель (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ИНТЕГРАЛЬНОГО

ЗАПОМИНАЮШЕГО УСТРОЙСТВА

Изобретение относится к вычислительной технике, в частности к микроэлектронике, и может быть использовано в производстве интегральных МОП-схем.

Известен усилитель считывания для динамических запоминающих устройств (ЗУ), состоящий из двух инверторов и двух ключевых транзисторов, причем вход первого инвертора подключен к истокам первого и второго ключевых транзисторов, сток первого ключевого транзистора подключен к выходу первого инвертора, объединенного с входом второФ

ro инвертора, а сток второго ключевого транзистора подключен к выходу второго инвертора, а затворы ключевых транзисторов подклю"ены к шинам управляющих сигналов 1) . Однако при таком построении усилителя не обеспечивается компенсация помехи от включения транзистора выборки однотранзисторной ячейки памяти, что снижает эффективную чу вствительность усилителя, потребляется значительная мощность в статическом режиме и ограничивается быстродействие. Наиболее близким к предлагаемому техническим решением является усилиS тель считывания для интегрального ЗУ, содержащий два усилительных транзистора с общим истоком, соединенных триг герной связью, стоки которых соединены соответственно с первой и второй сигнальными шинами, а общий исток соединен с первой шиной управления, два нагрузочных транзистора, истоки которых соединены с соответствующими сигнальными шинами, а стоки — с второй шиной

15 управления (2) .

Однако в интервале времени между опрокидыванием триггера и его отключением всегда существует цепь сквозного потребления через один из усилительных и один нагрузочный транзистор, усилитель потребляет энергию от источника питания и после окончания процесса опрокидывания, что ведет к увеличению потребляемой мощности и снижает его

5 4 никает информационный разбаланс напряжений.

После считывания сигнала из ячейки . на паразитную емкость плеча подается отрицательный перепад напряжения на шину 5 и положительный перепад напряжения на шину -13. При этом напряжение на затворах нагрузочных транзисторов

6 и 7 достигает значения большего, чем напряжение питания, что обеспечивает работу этих транзисторов в крутой области характеристик. После подачи сигналов на управляющие шины 5 и 13 начинается процесс опрокидывания усилителя в устойчивое состояние, направление опрокидывания усилителя определяется знаком информационного разбаланса сигнальных шин.

Как только величина разбаланса достигнет величины, большей порогового напряжения ключевых транзисторов 1 1 н 12, отпирается один из них, например

11 (эатвор его будет находиться под более высоким потенциалом). В результате МОП-конденсатор 9 разряжается через транзистор 11 на сигнальную шину, находящуюся под более низким потенциалом, а нагрузочный транзистор 6 запирается. После окончания процесса опрокидывания усилитель приходит в следующее состояние: нагрузочный транзистор 7 открыт .и, находясь в крутой потенциал соответствующей сигнальной шины на высоком уровне, транзисторы

1 и 11 также открыты и поддерживают потенциал соответствующей сигнальной шины и затвора нагрузочного транзистора 6 на низком уровне. Транзисторы 6, 2 и 12 выключены, так как напряжения затвор — исток этих транзисторов меньше порогового.

Таким образом, состояние схемы по окончании переходного процесса можно сравнить с состоянием триггера на МОП« транзисторах с дополняющими типами проводимости, т.е. здесь также отсутствуют цепи статического потребления и дифференциальный выходной сигнал на сигнальных шинах равен напряжению питания.

Это имеет большое значение для интегральных динамических ЗУ большой и сверхбольшой емкости, так как мощность, потребпяемая известными усилителями считывания, состагляет 70-80,с мощности потребления ЗУ. Применение предлагаемого усилителя позволит снизить мощность потреблений ЗУ в 2-3

3 92840 быстродействие за счет заряда параэитной емкости схемы.

Uem изобретения — уменьшение потребляемой мощности и увепичение быстродействия усилителя считы вания.

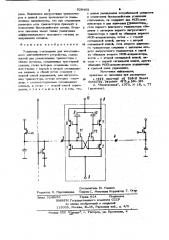

Поставленная цель достигается тем, что усилитель ссдержит два МОП-конденссатора и два ключевых транзистора, сток первого ключевого транзистора соединен с затвором первого нагрузочного транэис- gO тора и одной из обкладок первого МОПконденсатора, исток - с первой,сигнальной шиной, затвор — с второй сигнальной шиной, сток второго ключевого транзис тора соединен с затвором второго нагру- 15 эочного транзистора и одной из обкладок второго МОП-конденсатора, исток — с второй сигнальной шиной, затвор — с первой сигнальной шиной, другие обкладки

МОП-конденсаторов кЬключены к третьей шине управления.

На чертеже представлена схема усилителя считывания.

Усилитель считывания содержит два усилительных транзистора 1 и 2 с общим истоком, соединенных триггерной связью, стоки которых соединены соответственно с первой и второй сигнальными шинами 3 и 4, а общий исток соединен с первой шиной управления 5, два нагрузочных транзистора 6 и 7, истоки которых соединены с соответствующими . шинами 3 и 4, а стоки - с второй шиной области характеристики, поддерхивает управления 8, два МОП-конденсатора 9 и 10 и два клю. евых транзистора 11 и

12, сток транзистора 11 соединен с затвором транзистора 6 и одной из обкладок МОП-конденсатора 9,, исток ; с шиной 3, затвор - с шиной 4, сток транзистора 1 2 соединен с затвором транс

4О зистора 7 и одной из обкпадок МОП-конденсатора 10, исток — с шиной 4, затворс шиной 3, другие обкладки МОИ-конденсаторов 9 и 10 подключены к третьей шине управления 13.

Висходном состоянии управляющая ши-

45 иа 8 подкпючена к источнику питания (на чертеже не показан), а сигнальные шины 3 и 4 и управпяющая шина 5 заряжены до опорного напряжения, отключены от источника предзаряда (на чертеже не ноказан) и сохраняют свои потенциалы на параэитных емкостях. На шине 13 поддерживается низкое напряжение. Заряд, считанный иэ динамической ячейки памяти (на чертеже не показана) на с паразитную емкость одной из сигнальных шин, вызывает изменение ее потенциала, в результате между шинами 3 и 4 воз92840 раза. Включение нагрузочных транзисторов в данной схеме производится повышенным напряжением, что при сохранении размеров этих транзисторов приводит к повышению быстродействия схемы. Большое значение имеет также увеличение дифференциального выходного сигнала до напряжения питания.:

Формула изобретения lo Усилитель считывания для интеграль.ного запоминаюшего устройства, содержаший два усилительных транзистора с обшим истоком, соединенных триггерной связью, стоки которых ссединены соответственно с первой и второй сигнальными шинами, а обший исток соединен с первой шиной управления, два .нагрузочных транзистора, истоки которых <-оединены с соответствуюшими сигнальными. шинами, а стоки — второй шиной управления, отличающийся тем, то, 5 6. с целью уменьшения потребляемой мощности и увеличения быстродействия усилитеия считывания, он содержит два МШ-конденсатора и два ключешак анзисторае сток первого ключевого транзистора соединен с затвором первого нагрузочмого транзистора и ogaol ss обкладок первого

МОП-конденсатора, исток - с repaoN сигнальной шиной, затвор - с второй сигнальной шиной, сток второго ключевого транзистора соединен с затвором второго нагруэочного транзистора и одной иэ обкладок второго МОЙ-конденсатора, исток — с второй сигнальной шиной, затвор - с первой сигнальной шиной, другие обкладки МОП-конденсаторов подключены к третьей шине управления.

Источники информации, принятые во внимание цри экс ертизе

1. gE5Q, Toornag oR 8оИ6 Вьже

OrcvAs, ОМоЬег <873,р. ЗОЬ- Зоъ .2. Электроника, .3973, М. 38, с. 77 (прототип) .

Составитель Ю. Ушаков

Редактор О. Персиянцева ТехредС. Мигунова Корректор Г. О-аР.

Заказ 3248/64 . Тираж 624 Подписное

ВНИИПИ Государственного ксмитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4