Запоминающее устройство

Иллюстрации

Показать всеРеферат

(72) Авторы нэобретення

Н 1О. Васильев и В.В. Николаев (71) Заявнтель (54) ЗАПОИИНИЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоми- нающим устройствам статического типа и может быть, использовано в радиоло" кационных индикаторных устройствах с преобразованием радиолокационной и вспомогательной знаковой информа" ции в телевизионный стандарт.

Известно запоминающее устройство преобразователя радиолокационной .

10 информации в телевизионный стандарт, построенное на основе больших интегральных схем (БИС) запоминающих устройств с .произвольной выборкой ЗУПВ), содержащее коммутатор адре1$ сов записи считывания. и сигналов управления, и -слойную матрицу памяти, преобразователи параллельного кода в последовательный для каждого слоя матрицы (13.

Недостатком этого устройства является большая емкость преобразователей кодов, которая должна быть равна емкости строки матрицы.

Наиболее близким к предлагаемому по назначению и технической сущности является запоминающее устройство преобразователя раэверток, содер" жащее матрицу памяти, имеющую О слоев, коммутатор адресов, преобразователи кодов для каждого слоя матрицы памяти..Работает известное устройство следующим образом, На информационные входы каждого слоя матрицы поступает соответствующий разряд трехразрядного кода радиолокационного видеосигнала, На входы коммутатора адресов поступают адреса записи и считывания и сигналы управления, Выходы коммутатора адресов подключены к адресным входам матрицы, т.е. к адресным входам всех

БИС ЗУПВ. Выходы .каждого слоя мат" рицы подключены к входам преобразователей кодов данного слоя, Выходы преобразователей являются вы ходами всего устройства.1 Это уст- ройство работает в двух режимах, 92840

3 раздеяенных во;:времени, - записи и считывания. Режим работы определяется сигналами с выходов коммутатора адресов,.Считывание информации, . записанной в устройстве памяти, осуществляется во время обратного хо- да строчной телевизионной развертки.

При этом коммутатор адресов подключает к адресным входам матрицы памяти адреса считывания и. задает ре- 1О жим считывания. Йод воздействием этих сигналов, за время обратного . хода строчной развертки, информация из заданной строки матрицы памяти переносится в преобразователи кодов. Этот перенос осуществляется параллельными словами. К моменту начала прямого хода строчной развертки вся информация, записанная в трехслойной строке матрицы памяти, должна быть перенесена в преобразователи .кодов. Таким образом, емкость каждого преобразователя кодов должна быть

: равной емкости строки памяти .

Во время прямого хода строчной телевизионной развертки осуществляет

cR вывод считанной видеоинформации из преобразователя кодов на те- . левизионный монитор в виде последоватеяьного кода. Одновременно осу- ., ЗЭ ществляется запись радиолокационного видеосигнала в матрицу памяти. PewHM записи и адреса задаются коммутатором. Время, отводимое на,запись информации, эа период строчной телевизионной развертки " 64 мкс, равно прямому ходу строчной развертки50 мкс,т.е.50/6478"ь времени в .этом устройстве отводится на запись(23. .Недостаток известного устройства заключается в его сложности, так как для построения преобразователей ко" дов необходимо значительное оборудование.

Целью изобретения является упрощение аппаратурных затрат (т.е. уменьвение числа микросхем) при сохранении времени, отводимого на запись инфор" мации в запоминающее устройство.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее группу накопителей,. адрес- : å входы которых подключены к выходам коммутатора адресов, а выходык входам. соответствующего преобра" зователя кода, введены дополнительные Я группы накопителей, дополнительные коммутаторы адресов, дополнительные преобразователи кода, коммутаторы

7 1 и счетчик, выходы которого подключены к управляющим входам преобразователей кода и коммутаторов, вход счетчика подключен к синхрониэирующим входам преобразователей кода и является синхронизирующим входом устройства, адресные входы накопи" телей каждой дополнительной группы подключены к,выходам соответствующего дополнительного коммутатора адресов, выходы соответствующих накопителей каждой дополнительной группы подключены к информационным входам соответствующих преобразователя кода и до.полнительного преобразователя .кода, выходы которых подключены к информационным входам соответствующего коммутатора, выходы коммутаторов являются выходами устройства.

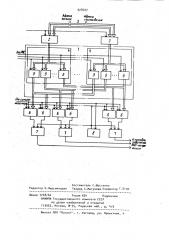

На чертеже представлена структур" ная схема запоминающего устройства, Устройство содержит матрицу памяти 1, имеющую несколько (и) слоев, . коммутаторы адресов 2, адресные входы 3, подматрицы 4 памяти, содержащие накопители 5, преобразователи 6 кода, коммутаторы 7 и счетчик 8.

- Адресные входы каждой подматрицы 4 подключены к выходам собственного коммутатора адресов 2. К входам преобразователей 6 кода каждого слоя подключены обьединенные выходы соответствующего слоя подматриц памяти, Выходы преобразователей 6 одного слоя подключены к входам коммутатора 7.

К управляющим входам преобразователей 6 и коммутаторов 7 подключен счетчик 8, на вход которого поступает сигнал тактирования преобразователей.

Устройство работает следующим образом.:

На сигнальные входы каждого слоя матрицы памяти (т.е. всех БИС ЗУНВ) поступает. соответствующий разряд кода радиолокационного видеосигнала.

На коммутатор адресов 2 поступают адреса записи и считывания и сигналы управления.

Считывание информации осуществляется циклами во время прямого хода строчной телевизионной развертки.

Длительность цикла задается счетчиком 8. В первый. цикл из матрицы памяти 1 считывается параллельное слово с числом разрядов, емкостью преобразователя (4-16 бит). Считанное слово записывается в первый. преобразо92840 ватель 6 кода; Во второй цикл считы-1 вается следующая часть строки памяти и заносится во второй преобразователь

6. Одновременно информация в виде последовательного кода выводится иэ ,nepeoro преобразователя через коммутатор 7 на выход устройстяа. В третьем цикле считанная из матрицы памяти информация записывается в первый .пре": образователь 6 и выводится иэ второго 1в и т,д. Таким образом, как и в известном устройстве, эа время прямого хода . строчной телевизионной развертки будет считана вся строка матрицы IlBMR ти. - .. 1

Построение матрицы памяти в виде подматриц, снабженных собственными коммутаторами адресов, позволяет обеспечить время, отводимое на запись информации в устройство памяти, не меньше,чем в известном устройстве.

Запись может осуществляться в любую иэ подматриц, не занятую в данный момент считыванием, так. как режим каждой подматрицы задается собственным коммута гором. Если число подматриц И, то в любой моменг времеб ни может производиться запись в И-1 подматриц памяти. Кроме того, запись осуществляется и во время об" 1а ратного хода с грочной телевизионной развертки. Это позволяет увеличить общее время,.записи в устройство. С другой стороны, при малой скорости обновления радиолокационной информагции нет. необходимости в разделении матрицы памяти на подматрицы, В этом случае для записи достаточно време" ни обратного хода строчной развертки. .Такйм образом, изменение числа под- матриц И позволяет согласовывать параметры быстродействия устройства памяти и радиолокатора, Разрядность преобразователей кода зависит от емкости строки матрицы памяти и быстродействия памяти.

Положительный эффект при использовании предлагаемого устройства . !

7 6. заключается в уменьшении оборудова", ния, необходимого для построения устройства в. зависимости от требуемой скорости записи и параметров элементов памяти.

Формула изобретения

Запоминающее устройство, содержа . щее группу накопителей, .адресные входы которых подключены к выходам коммутатора адресов, .а выходы - к входам соответствующего преобразователя кода, î T л и ч а ю щ е. " е с я тем, что, с целью упрощения устройства, оно содержит дополнительные группы накопителей, дополнительные коммутаторы адресов, до" полнительные преобразователи кода, коммутаторы и счетчик, выходы которого подключены к управляющим входам преобразователей кода и комму" таторов, вход счетчика подключен к синхрониэирующим входам преобра" зователей кода и является синхронизирующим входом устройства, адресные входы накопителей каждой догтолнительной группы подключены к выходам соответствующего дополнительного коммутатора адресов, выходы соответствующих накопителей каждой дополнительной группы подключены,к инфор" мационным входам соответствующих преобразователя кода и дополнительного преобразователя кода, выходы которых подключены к информационным:входам соответствующего коммутатора, выходы коммутаторов. являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании

1»" 1361156, кл. G 01 5 1/14, 1974.

2. Патент СМВ и 3765018, кл. Q 01 9 7/04, опублик. 1973 (прототип). t

92340/

44жа

ЭО/ЛУНЮ

4дреса сеигпь

Составитель С,Шустенко

Техред С.Иигунова Корректор Г 0i Ð

Редактор О.Персиянцева филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 3248/64 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5