Матричный накопитель для интегрального запоминающего устройства

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Ю, В. Минков, В. И. Соломоненко и П, M. Гафаров

Р (7I) Заявитель (54) МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ИНТЕГРАЛЬНОГО

ЗАПОМИНАЮШЕГО УСТРОЙСТВА

Изобретение относится к вычислитель4 ной технике, в частности к микроэлектронике, и может быть использовано для создания интегральных динамических запоминающих устройств с произвольной выборкой (ЗУПВ).

Известно интегральное МОП-ЗУПВ, основанное на применении однотранзистор9 ного динамического элемента памяти и дифференциального усилителя считыва,ь: ния (1J .

Наиболее близким к предлагаемому техническим решением является матричный накопитель для интегрального запоминающего устройства, содержащий элементы памяти, шины выборки и числовые

33 шины; каждая иэ которых разделена на полушины 21 .

Однако в известных устройствах чис-ловые полушины расположены по обе сто20 роны от усилителя считывания таким образом, что каждая иэ них пересекается с половиной общего количества шин выборки. При этом числовые полушины расходятся, удаленными от усилителя считывания концами на значительное раостояние друг от друга. На таком протяжении заметны неоднородности свойств кремниевой пластины и параметров получаемых при изготовлении элементов структур интегральной схемы (разнотолщинность подэатворного и изолирующего окисла, неравномерность глубины диффузии и концентрации примеси в диффузионных областях и др.). Это вызывает нарушение симметричности числовых полущин, что приводит к необходимости повышать величину полезного сигнала эа счет увеличения площади элементов памяти. Удеченное друг от друга расположение числовых полушин создает условия для воздействия на них нестабилиэиро ванных помех от импульсных формирователей схемы управления, расположенных по периферии кристалла.

Белью изобретения является увеличение информационной емкости и помехоэа щищенности накопителя, 928412

Указанная цель достигается тем, что в матричном накопителе для интеграль-, ного запоминающего устройства полушины числовых шин пересечены каждой шиной выборки, а элементы памяти расиоложены в местах пересечения шин выборки с одной из полушин числовых шин.

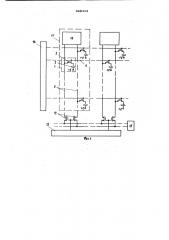

На фиг. 1 изображено .взаимное расположение элементов на кристалле ЗУПВ; на фиг. 2 - фрагмент топологии матрич- 10 ного накопителя,, Накопительподанному изобретению использованн в и нтегральном ЗУПВ емкостью"

16384 бита. Запоминающее устройство, изготовленное по г -канальной МОП технологии с самосовмещенными кремниевыми затворами и с двумя уровнями разводки иэ поликристаллического кремния, содержит элементы памяти 1, состоящие из

МОП-конденсатора 2 и ключевого транзистора 3. Шины выборки 4 выполнены из поликристаллического кремния второго уровня и являются одновременно затворными шинами ключевых транзисторов 3. Числовые полушин 5, соединен- у нные с ключевыми транзисторами 3, выполнены из алюминия и имеют контакты

6 на стоковые области пары элементов памяти 1. Конденсаторы хранения 2 образуются пленкой поликристаллического кремния первого уровня 7, на которую подается постоянное, положительное от.носительно подложки, напряжение, и инверсионным слоем, существующим в областях, где поликристаллический кремний первого уровня расположен, над участками тонкого окисла. Йля формирования диффузионных областей 8 ключевых транзисторов 3 элементов памяти 1 и для создания контактов 6 алюминиевых числовых полушки 5 к стоковым областям 8 ключевых транзисторов 3 общая обкладка 7 конденсаторов хранения

2 имеет окна 9. Числовые полушины 5 попарно соединены с усилителями считывания 10. Элементы памяти 1, шины выборки 4 и числовые полушины 5 образуют накопитель 11. Блок ключей ввода-ewaoaal. 12, дешифраторы 13 и 14 и устройство 15 вывода информации осуществляют выборку элемента памяти, вывод из накопителя считываемой информации и ввод в накопитель записываемой информации.

Улучшение симметрии числовых полушин накопителя и повышение его помехозащищенности позволяет уменьшить площадь конденсатора хранения однотранэисторного элемента памяти и тем самым разместить на кристалле интегрального

ЗУПВ накопитель большого информационного объема.

Ф ормула изобретения

Матричный накопитель для интегрального запоминающего устройства, содержащий элемент памяти, шины выборки и числовые шины, каждая из которых разделена на полушины, о т л и ч а ю— шийся тем, что, с целью увеличения информационной емкости и помехозащищенности накопителя, в нем полушины числовых шин пересечены каждой шиной выборки, а элементы памяти расположены в местах пересечения шин выборки с одной из полушин числовых шин.

Источники информации принятые во внимание при экспертизе

1. Патент США No 3838404, кл. 340-173, 1972.

2. Электроника, 1973, No 19, с. 43-51, (прототип).

92841 2

Составитель Ю, Ушаков

Редактор О, Персиянцева Техред С.Мигунова Корректор F. Огар

Заказ 3248/64 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР ио делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4