Блок выборки информации из матричного накопителя

Иллюстрации

Показать всеРеферат

CoIo3 Сееетсимк

Социалистически«

Рвспубттни (LL) К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (бт) Дополнительное к авт. санд-ву (22) Заивлено 13.08,80 (2I ) 2972776/18-24

O (5l jN. Кл.

G 11 С 11/40 с присоединением заявки М

9кударстее««ьй каи«тет CCCI ао йеаам «забрете««й

«втерыт«« (23) Прнормтет (ЬЗ) УДК681.327..66(088.8) Опубликовано 15.95.82. Бюллетень At 18

Дата опубликования опнсанн«18.05.82 (72) Авторы изобретения

А. A. Кассихин и В. Г. Хайновский (7I ) Заяынтель. (54) БЛОК ВЫБОРКИ ИНФОРМАЦИИ

ИЗ МАТРИЧНОГО НАКОПИТЕЛЯ

Изобретение относится к вычислительной технике, а именно к схемам выборки данных и микроэлектронных репрограмми. руемых постоянных запоминающих устройств с. ультрафиолетовым стиранием.

Известна схема выборки данных, содержащая адресные МОП-транзисторы, истоки которых подключены к разрядным шинам накопителя, а затворы подключены к адресным шинам tl | .

Однако известное устройство обладает недостаточным быстродействием.

Наиболее близким к предлагаемому по технической сущности и схемному решению является блок выборки информации из матричного накопителя, содержащий

МОт )-тра нзис торы (2 3

Однако указанная схема характеризуется недостаточным быстродействием, обусловленным длительным зарядом невыбранных истоковых разрядных шин, имеющих значительную емкость, после изменения адреса столбца.

11елью изобретения является повьтшение быстродействия.

Поставленная цель достигается тем, что в блоке выборки. информации из мат ричного накопителя, содержащем МОПтранзисторы, затвор первого транзистора соединен с первой адресной шиной, а его сток соединен со стоком второго транзистора и первой информационной шиной, исток первого транзистора соединен с истоками третьего и второго транзисторов и является первым выходом первой группы выходов блока, затвор второго транзистора соединен со второй адресной шиной, затвором четвертого тРанзистора и затвором пятого транзистора, ис-. ток которого соединен с.шиной нулевого потенциала, а сток — .с истоком шестого транзистора и является вторым выходом второй группы выходов блока, сток шестого транзистора соединен с первой шиной питания, сток четвертого транзистора соединен со второй информационной шиной и стоком седьмого транзистора, затвор

26

35 ао

56

3 92 которого соединен с третьей адресной шиной, а исток - с истоками четвертого и восьмого транзисторов и является вторым выходом первой группы выходов блока, затвор восьмого транзистора соединен со второй шиной питания и затвором третьего транзистора, дополнительно затвор шестого транзистора .соединен с первой адресной шиной, сток третьего транзистора соединен с первой информационной шиной, сток восьмого транзистора соединен со второй информационной шиной, затвор девятого транзистора соединен с третьей адресной шиной, его исток — с выходом второй группы выходов блока, а сток - с первой шиной питания.

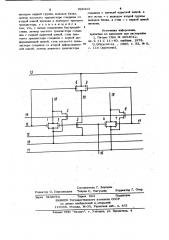

На чертеже представлена принципиальная электрическая схема блока выборки информации из матричного накопителя.

Блок содержит МОП-транзисторы 1-9, первую и вторую информационные шины 10 и 11, шину нулевого потенциала 12, первую и вторую шины питания 13 и 14, первую, вторую, третью адресные шины

15, 16 и 17, первый 18, второй 19 выходы первой группы выходов блока, первый выход 20 второй группы выходов блока.

Блок функционирует следующим образом.

Пу"ть уровень напряжения на адресной шине 16 высокий, соответствующий логической единице, и транзисторы 2, 4 и 5 включены, уровень напряжения на адресных шинах 15 и 17 низкий, соответствующий логическому нулю, и транзисторы 1 и 7 выключены, также .выключены транзисторы 6 и 9, вследствие чего потенциал выхода 20 равен потенциалу шины нулевого потенциала 12, и транзисторы накопителя, включенные между выходами 18, 20 и 19, 20 могут проводить ток. Если запоминающий транзистор, включенный между выходами 18 и 20 запрограммирован, то он не пропускает тока, и потенциал на первом выходе 18 и информационной шине

10 находится на уровне, соответствующем логическому нулю. Если запоминающий транзистор, включенный между выходами 19 и 20 не запрограммирован, то он проводит ток, разряжая выход 19 и через включенный транзистор 4 шину

11, определяя сигнал, соответствующий логической единице. Потенциалы шин 10 и 11 через транзисторы 3 и 8 передаются на выходы 18 и 19. При малой проводимости транзисторов 3 и. 8 емкость выходов 18 и 19 оказывается изолиро8413 4 ванной от емкости шин 10 и 11, что не влияет на скорость их перезаряда.

Когда осуществляется, выбор нового выхода, то уровень напряжения на адресной шине 16 .падает до логического нуля, и транзисторы 2, 4 и 5 выключаются. Пусть теперь возбуждается адресная шина 17 и транзистор, включаемый между выходом 19 и следующим выходом, запрограммирован и тока не проводит. Тогда потенциал выхода 20 поднимается трензистором 9 и запоминающий тоанзистор, включенный между. выходами 19 и 20 перестает проводить ток, не препятствуя заряду выхода 19 и шины 11 и ее быстрому достижению потенциала логического нуля.

Предлагаемый блок выборки обладает большим быстродействием, которое достигается благодаря тому, что при изменении адреса столбца, при котором потенциал на прежде выбранной адресной Шине. падает до уровня логического нуля, а на вновь выбираемой шине возрастает до уровня логической единицы, потенциал на ранее эаземлЕнной истоковой разрядной шине может возрастать быстрее до эапирания неэапрограммированного транзистора, подключенного к ней истоком, при высоком напряжении логической еди шцы на адресной шине строки.

Формула изобретения

Блок выборки информации. иэ матричного накопителя, содержащий МОП-транзисторы, затвор первого транзистора соединен с первой адресной шиной, а его сток соединен со стоком второго транзистора и первой информационной шиной, исток первого транзистора соединен с истоками третьего и второго транзисторов и является первым выходом первой группы выходов блока, затвор второго транзистора соедиен со второй адресной шиной, затвором четвертого транзистора и затвором пятого транзистора, исток которого соединен с шиной нулевого потенциала, а сток - с.истоком шестого транзистора и является выходом второй группы выходов блока, сток шестого транзистора соединен с первой шиной питания, сток четвертого транзистора соединен со второй информационной шиной и стоком седьмого транзистора, затвор котброго соединен с третьей адресной шиной, а исток - с истоками четвертого и восьмого транзисторов и является вторым

5 928413 6 выходом первой группы выходов блока, соединен с третьей адресной шиной, а затвор восьмого транзистора соединен со его исток - с выходом второй группы второй шиной питания и затвором третьего выходов блока, а сток - с первой шиной транзистора, о т л и ч а ю ш и и с я питания. тем, что, с целью повышения быстродей- S ствия, затвор шестого транзистора соеди- Источники информации, нен с первой адресной шиной, сток тре- принятые во внимание при вксперт йюе тьего транзистора соединен с первой ин« l. Патент США hh 4094012, формационной шиной, сток восьмого тран- кл. 5 11.С 11-40, онублик. 19Ò8. энстора соединен со второй ннформацион- о 2.ЕРестгоп4сь, 1980, т. 53, М 6, ной шиной, затвор девятого транзистора с. 116 (прототип).

Составитель Г. Бородин

Редактор О. Персиянцева Техред С, Мигунова Корректор Г ° Огар

Заказ 3248/64, Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и- открытий

113035, Москва, Ж-35, Раушская наб., д..4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4