Ячейка памяти для буферного регистра

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 928417

И 3О6РЕТЕ Н ИЯ.

Союз Советсник

Социапнстнчесник

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свнд-ву Р 799010 (22) Заявлено 24.06.80 (21) 2945654/18 — 24 . (51)M. Кл. с присоединением заявки М

G 11 С 19/00 ВкударстекннЫ1 квинтет

СССР но делам нмбретеиий н открытий (23) Приоритет (53) УДК 681.327. .66 (088.8) Опубликовано 15.05.82. Бюллетень М 18

Дата опубликования описания 15.05.82 (72) Автор изобретения

Б, С. Цирлин (7!) Заявитель

Институт социально-экономических проблем "АН СССР (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ БУФЕРНОГО РЕГИСТРА

Изобретение относится к вычислительной технике и может быть использовано для построения буферных запоминающих устройств.

По основному авт. св. Н 799010 известна ячейка памяти для буферного регистра, содержащая основной и вспомогательный трехстабильнв|е триггеры, каждый из которых выполнен на трех элементах И вЂ” ИЛИ вЂ” НЕ и десять входных шин, соединенных со входами этих триттеров, причем выходы всех трех элементов И-ИЛИ вЂ” НЕ основного триггера ячейки соединены со входами двух элементов И вЂ” ИЛИ-НЕ ее вспомогательного триггера, выходы которых соединены со входами двух элемейтов И вЂ” ИЛИ-.НЕ основного триггера ячейки. В буферном регистре из таких ячеек обесйечивается не только сдвиг информации, но и ее.параллельное считывание (1).

Однако, кроме указанных двух операций, никакие другие операции в этом буфернОм регистре не осуществляются, что ограничивает его область применения.

Целью изобретения является расширение области применения ячейки памяти для буферного регистра за счет обеспечения возможности осуществления одновременного реверсивного сдвига информации и параллельного ее считывания.

Поставленная цель достигается тем, что в ячейку памяти для буферного регистра введены RS-триггер и дополнительные вход

10 ные шины, первая из которых соединена с третьим входом основного трехстабильного триттера и с первым входом RS-триггера, вторая дополнительная шина соединена с третьим входом вспомогательного трехстабильного триггера и с четвертым входом

3$ основного трехстабильного триггера, третья, „ четвертая и пятая дополнительные входные шины соединены соответственно с четвертым входом вспомогательного трехстабильного триггера, второй вход RS-триггера соединен с шестой дополнительной входной шиной, третий вход RS-триггера соединен с первым выходом вспомогательного н со вторым и третьим выходами основного трехстабильно2841.7 4

5 !

55

3 9 .го триггеров, первый выход RS-rpmepa соединек с пятым входом основного трехстабильного триггера, четвертый вход RS-триггера соединен со вторым и с третьим выходами вспомогательного трехстабильного триггера.

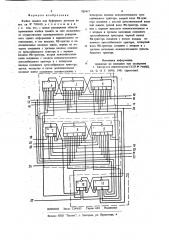

На чертеже изображена функциональная схема предложенной ячейки памяти.

Ячейка памяти содержит основной и вспомогательный трехстабильные триггеры 1 и 2, RS-триггер 3, элементы И вЂ” ИЛИ вЂ” НЕ 4 — 11, на которых выполнены соответственно триггеры 1, 2 и 3, основные входные шины 1221 и дополнительные входные шины 22 — 27, При построении буферного регистра шины 12, 13, 14, 18, 24, 25, 26 и 27 i-й ячейки памяти соединяются .соответственно с выходами элементов 5, 6, 4, 7, 10, 8; 9 и

l1 (i-1)-й ячейки памяти, а шины 15, 16, 17, 19, 20, 21, 22, 23. i-й ячейки. памяти с выходами элементов 5, 6, 4, 7, 8, 9, 10, 11 (i+I)-й ячейки памяти.

Ячейка памяти работает следующим образом.

Основной и вспомогательный триггеры 1 и

2 имеют три устойчивых состояния (значения на выходах элементов И-ИЛИ вЂ” HE 4, 5, 6 и 7, 8, 9 соответственно): 011 — информация в триггера отсутствует, 110 — в триггере записана "1", 101 — в триггера записан "0".

Пока в триггере 3 сохраняется состояние

"10" в основном и вспомогательном тригге- рах 1 и 2 ячейки памяти сдвиг информации происходит так же, как и в обычной о ячеике памяти буферного регистра, причем в основной триггер li-й ячейки памяти информация принимается из основного триггера (i — 1)-й ячейки памяти, а во вспомогательный триггер 2i.-й ячейки информация. принимается из вспомогательного: триггера (i+I)-Й ячейки памяти. При этом условием записи (стирания) информации в основном триггера li-й ячейки памяти является отсутствие (наличие) информации в основном триггера (i+1)-й ячейки памяти и наличие (отсутствие) информации в основном триггере (i — 1)-й ячейки памяти. Для вспомогательного триггера 2 условия обратны приведенным.

Сдвиг информации в основном и вспомогательном триггерах ячеек памяти буферного регистра приводит к тому, что основные триггеры ячеек i, (i+1),, оказываются заполнены информацией, а во всех вспомогательных триттерах этих. ячеек памяти инфор.мация отсутствует. По мере распространекия такого состояния от и-й ячейки памяти буферного регистра к его первой ячейке памяти дополнительные триггеры этих ячеек15

35 ю

50 памяти переводятся в состояние "01". Условием перехода дополнительного триггера

i-й ячейки памяти в состояние "ОГ является наличие такого состояния в дополнительном триггере (+1)-й ячейки памяти, наличие информации в основном триггера

i-й ячейки памяти и отсутствие информации в основном тритгере (i — 1)-й ячейки памяти и вспомогательном триггере 2 i-й ячейки.

Состояние "01" триггера 3 i-й ячейки блокФ рует запись информации в ее основной триггер 1 из основного триггера (i — 1)-й ячейки.

При этом, так же, как и в известном устройстве, в основном триггере i-й ячейки памяти оказывается записан i-й разряд сдвигаемого кода.

После того, как в основных триггерах всех ячеек памяти буферного регистра записана информация, а в их дополнительных триггерах установится состояние ."01" (при этом во всех вспомогательных триггерах информация отсутствует), происходит последовательная, начиная с первой ячейки памяти, перепись информации из основных триггеров ячеек памяти в их, вспомогательные триггеры. Условием записи информации во вспомогательный триггер 2i-й ячейки из ее основного триггера 1 является отсутствие информации в основном триггере (i — 1)-й ячейки и наличие состояние "01" . триггера (i — 1) -й ячейки. После этого информация в основном триггере i-й ячейки памяти стирается.

По мере заполнения информацией вспомогательных триггеров ячеек памяти буферного регистра их триггеры переходят в состояние

"I0". Условием перехода триггера (i — 1)-й ячейки памяти в состояние "10" является нали- . чие состояние "10" триггера (i — 1)-й ячейки памяти, наличие информации во вспомогательном триггере 2i-й ячейки и отсутствие информации в ее основном триггере 1.

После того, как во вспомогательный триггер и-й ячейки памяти буферного регистра записана. информация из ее основного триггера, с выходов всех вспомогательных триггеров, так же, как и в известном устройстве, может быть параллельно считана информация.

Как только триггер первой ячейки памяти буферного регистра окажется в состоянии 10, с выхода ее вспомогательного триттера может быль последовательно считана информация, ранее последовательно записанная в основные триггеры ячеек памяти буферного регистра.

При этом порядок следования разрядов поменяется на обратный, т.е. если код был записан в буферный регистр, начиная с п-разряда, то считывание произойдет, начиная с первого разряда. Одновременно с этим в буферный регистр может быть последовательно записан новый код.

928417

<$

ff

17

Я2.

32

И

1Ф

25

28

2f

ВНИИ11И Заказ 3249/65 Тираж 624 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Формула изобретения

Ячейка памяти для буферного регистра по авт. св. N 799010, о т л и ч а ю щ а яс я тем, что, с целью расширения области применения ячейки памяти за счет возможнос-: ти осуществления одновременного реверсивного сдвига информации и параллельного ее считывания, в нее введены RS-триггер и дополнительные входные шины, первая из которых соединена с третьим входом основного трехстабильного триггера и с первым входом RS-триггера, вторая дополнительная шина соединена с входом вспомогательного трехстабильного триггера и с четвертым входом основного трехстабнльного триггера, третья, четвертая и пятая дополнительные входные шины соединены соответственно с четвертым входом вспомогательного трехстабильного триггера, второй вход RS-триггера соединен с шестой дополнительной входной шиной, третий вход RS-триггера соединен с первым выходом вспомогательного и с вторым и третьим выходами основного трехстабильных триггеров, первый выход

RS-триггера соединен с пятым входом основного трехстабильного трютера, четвертый

1о вход RS-триггера соединен с вторым и с третьим выходами вспомогательного трехстабнльного триггера.

Источники информации, принятые вб внимание при зкснертизе

1. Авторское свидетельство СССР К 799010, кл. G 11 С 19/00, 1981 (прототип).