Умножитель частоты

Иллюстрации

Показать всеРеферат

Союз Советскнн

Социалистические

Респубпик

К АВТОРСКОМУ СВИДИТИЗЬСТВУ (ф! ) Дополнительное к авт. свид-ву (22)Заявлено 06.06.80 (2!) 2939560/18-21 (53)М. Кл. с присоединением заявки М и 03 9 19/10

Н 03 К 3/64

Гоеудеретмниыб квинтет

СССР ве делам наебретеннй н етнрытнй (23)Приоритет (53) УЛ,К 621. 374. .4(088.8) Опубликовано 15. 05. 82. Бюллетень М 18

Дата опубликования описания 15 . 05 . 82 (72) Автор изобретения

А.С, Карпицкий (7!) Заявитель (54) УИНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к измери тельной технике и может быть исполь. зовано при обработке информации, представляемой в виде периодических частотно-импульсных последовательностей.

Известно устройство, содержащее генератор эталонной частоты 10,фор" мирователь импульсов, блок управления, электронные ключи, мультивибратор, делитель частоты с постоянным коэффициентом деления, оавным коэффициенту умножения К, управляемый делитель частоты с переменным коэф" фициентом деления, блоки переноса, регистры памяти (Ц .

Однако данное устройство обладает недостаточно высокой точностью измерения частоты следования входной им-. пульсной последовательности, так как измерение производится в течение только одного периода; а также данное устройство предназначено только для однократного измерения частоты импульсной последовательности.

Целью изобретения является повышение точности и расширение функциональных возможностей за счет мно3 гократного измерения в течение коротких промежутков времени частоты входной импульсной последовательности. ! о

Поставленная цель достигается тем, что в умножитель частоты, содержащий генератор эталонной частоты,вы- . ход которого подключен к первым входам первого и второго ключей, вы-. ход первого иэ которых соединен с ! е первым входом управляемого делителя частоты, второй вход которого соединен с выходом блока переноса, первый и второй входы которого подключены соответственно к выходу управляе мого делителя частоты и к выходу первого регистра памяти, второй вход первого ключа соединен с первым выходом блока управления, второй

9286 выход ко горого соединен с первым входом третьего ключа, выход второго ключа подключен ко входу делителя частоты, второй регистр памяти,формирователь импульсов, введены формирователь временных интервалов, сумматор и блок запуска, первый выход которого подключен ко входам обнуле»

1 ния делителя частоты и регистров памяти и к установочному входу формиро !О вателя временных интервалов, информационный вход которого соединен через третий ключ с выходом формирователя импульсов, а выход подключен ко второму входу второго ключа и к первому входу блока управления,второй вход которого подключен ко второму выходу блока запуска, при этом разрядные выходы делителя частоты соединены с первыми разрядными вхо- щ дами, кроме первого старшего, сумматора, вторые разрядные входы которого, кроме второго старшего, подключены к выходу второго регистра памяти, первый и второй входы которого д соединены соответственно с выходом управляемого делителя частоты и с первым выходом сумматора, второй выход которого подключен к третьему входу блока переноса, а выход делителя частоты соединен со входом первого регистра памяти.

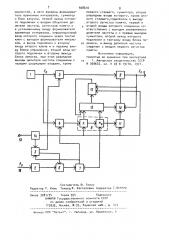

На чертеже .представлена функциональная схема устройства.

Устройство содержит генератор эталонной частоты, формирователь 2 импульсов, блок 3 управления, ключи

4-6, формирователь 7 временного интервала, делитель 8 частоты с постоянным коэффициентом деления на двух делителях с постоянными коэффициентами деления К и Чв, управляемый делитель 9 частоты с переменным коэффициентом деления, блок 10 переноса, регистры 11 и 12 памяти, сумматор 13, блок 14 запуска. На чертеже также

° показаны шина 15 старт-импульса, шина 16 входной импульсной последовательности.

10 при этом блок 14 вырабатывает на своем первом выходе импульс, который переводит в начальное состояние формирователь 7 временного интервала, обнуляет делитель 8 частоты и регистры 11 и 12. В это же время на втором выходе блока 14 вырабатывается сигнал, под действием которого блок 3 управления, закрывая ключ 5, запрещает прохождение импульсов опорной частоты с генератора 1 на вход управляемого делителя 9 частоты и, открывая ключ 6, позволяет проходить на информационный вход формирователя 7 временного интервала импульсной последовательности частоты fp с шины

16. Под действием импульсной последовательности через формирователь 2 с выхода ключа 6 на выходе формирователя 7 временного интервала формируется импульс положительной полярности длительностью N0T, который на время Н ОТ! открывает ключ 4 и на его выходе в течение этого времени проходит импульсная последовательность опорной частоты с генератора 1. Сразу же по окончании импульса на вы ходе формирователя 7 временного интервала блок 3 управления закрывает ключ 6 и открывает ключ 5, переводя устройство в режим воспроизведения, Снова в режим измерения устройство может быть переведено следующим старт-импульсом с шины 15.

В режиме измерения на вход делиNo теля 8 частоты за время --- = N Т о х

Йо поступает N = --- f импульсов и по

1 fx 0 окончании измерения в регистре 11 зафиксируется результат, равный цеN лой части числа ---, где К и N gК! О коэффициенты деления делителей 8, соответственно

N q1 Г Noто

KN î ) Г f - k. Nî или

Устройство работает следующим образом.

Возможны два режима работы устройства: первый режим - измерение, второй режим - воспроизведение импульсной последовательности.

Режим измерение начинается всякий раз по приходу на вход блока !4 запуска по шине 15 старт-импульса, В делителе 8 зафиксируется число

8 n<(N

1 можно считать, что отношение

KNo

5п» равно дробнои части отношения

KNo (N Ьп

928610 6

Обозначим (шр ) =(--„- „ -) (q) АР-, В регистрах 11 и 12 будет записан код периода входного сигнала, с точ1 ностью до ----. Можно считать, что ь KN0 отношение --- - - (q f; т. е. при

KNo измерении периода последовательнос" ти частоты f получается остаток Ь п.1, 1 измеренный с погрешностью d><„

М Кс =КМОР т.е. ошибка d уменьшена в Ио раз: дп Ф

q1 0 ""0

В режиме воспроизведения устройство работает следующим образом.

Каждым выходным импульсом управляемого делителя 9 с блока 10 переноса в управляемый делитель 9 заносится либо число(ай с регистра 11 памяти, когда на выходе старшего разряда сумматора 13 сигнал логического нуля, либо число(ц) + 1, когда на выходе старшего разряда сумиатора 13 сигнал логической единицы.

Если управляемый делитель 9 будет осуществлять деление частоты fy только на u cao(q ), то это приведет к тому, что каждый i-ый импульс будет роявляться на выходе с опережением на время i T0 (q ).

Чтобы повысить точность воспроизведения в данном устройстве, непрерывно производится суммирование остатков 5п1, что приводит к тоиу, что делитель 9 осуществляет деление частоты генератора 1 следующим образом: когда текущее значение суммы остатков меньше числа N0K то осуществляется деление на (q) когда текущее значение суммы остатков больше или равно числу NpK, то осуществляется деление на (q) + 1.

Таким образом осуществляется за держка появления импульса на выходе устройства на время Т0 в тот момент, когда расчетное опережение равно или превышает То.

Это реализуется следующим образом. Сумматор 13 производит текущее сложение остатков дп„. Причем на входы первого слагаемого поступает начальное значение суммы остатков п„, а на входы второго слагаемогопредыдущее значение суммы остатков с выходов регистра 12. Значение суммы каждый раз фиксируется в регистре

12 импульсом с выхода управляемого делителя 9 частоты. Как только текущее значение суммы остатков превысит или сравняется с числом КОМ, то на выходе старшего разряда сумматора

13 вырабатывается сигнал логической единицы. Этот сигнал, поступая на выход блока 10 переноса, формирует на его выходе число )qj + 1, которое заносится в делитель частоты 9. Это и обеспечивает деление частоты fy на !чйслоЯ + 1 и задержку импульса на,выходной kUHHe устройства на время

То . Причем вероятность того, что будет задержан (i + 1)-ый импульс.вместо i-го в данном устройстве значительно меньше по сравнению с известныи.

Таким образом, данное устройство позволяет многократно производить измерение исходной частоты импульсной последовательности и с точностью сколь угодно близкой к Т0 воспроизводить импульсную последовательность умноженной исходной частоты, причеи воспроизводить при отсутствии на входе исходной импульсной последовательности, при этом данное устройство имеет стабильный коэффициент умножения, более высокую -точность уиножения и воспроизведения, более широкие, чем у известного устройства возможности.!

25 е

35 формула изобретения

Умножитель частоты, содержащий

40 генератор эталонной частоты, выход которого подключен к первым входам

1 первого и второго ключей, выход первого иэ которых соединен с первым входом управляемого делителя частоты, 45 -второй вход которого соединен с выходом блока переноса, первый и второй входы которого подключены соответственно к выходу управляемого делителя частоты и к выходу первого регистра памяти, второй вход первого ключа соединен с первым выходои блока управления, второй выход которого соединен с первым входом третьего ключа, а выход второго ключа подключен к входу делителя частоты, второй регистр памяти, формирователь импульсов, отличающийся ( тем, что, с целью повышения точности и расширения функциональных воз928610

Составитель Ю. Тюпич

Редактор Т. Кинь Техред Ж. Кастелевич Корректор C шекмар

Заказ 3281/74 тираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, N-35, Раушская наб., д 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 можностей, в него введены формирвватель временных интервалов, сумматор и блок запуска, первый выход которого подключен к входам обнуления делителя частоты, регистров памяти и к установочному входу формирователя временных интервалов, информационный вход которого соединен через третий ключ с выходом формирователя импульсов, а выход подключен к второму входу второго ключа и к первому входу блока управления, второй вход которого подключен к второму выходу блока запуска, при этом разрядные выходы делителя частоты соединены с первыми разрядными входами, кроме первого старшего, сумматора, вторые разрядные входы которого, кроме второго старшего, подключены к выходу . второго регистра памяти, первый и второй входы которого соединены соответственно с выходом управляемого делителя частоты и с первым выходом сумматора, второй выход которого подключен к третьему входу блока петр реноса, а выход делителя частоты соединен с входом первого регистра памяти.

Источники информации, принятые во внимание при экспертизе

Авторское свидетельство СССР rP 369672, кл. Н 03 B 19/10, 1971