Многопороговый логический элемент четности

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (928653

ИЗОВВЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсник

Социалие тически к

Республик

Г (61) Дополнительное к авт. свид-ву (22)Заявлено 10.07.80 (2l) 2954891/18-21 с присоединением заявки М (23 (51)M. Кл.

Н 03 К 19/20

3Ьаударстваиый комитет

) Приоритет о

Опубликовано 15.05.82. Бюллетень М 18 (53) УДК621 ° 374 (088.8) по делам изабретеиий и открытий

Дата опубликования описания 15, 05. 82 (?2) Авторы изобретения

И.A.Ïàëüÿíîâ, В.И.Потапов и И.А.Чернакова

Омский политехнический институт (71) Заявитель (54) ИНОГОПОРОГОВь(Й ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

ЧЕТНОСТИ

Изобретение относится к автоматике и вычислительной технике, в част- . ности к элементам пороговой логики, Известен многопороговый логический элемент, позволяющий реализовать функцию четности, содержащий линейный сумматор, подключенный к резистивному делителю, соединенному с многопороговым дискриминатором Г1 1.

Недостатком указанного элемента

1о является низкая технологичность при интегральном исполнении, обуславливаемая тем, что используя полупроводниковую технологию трудно получить высокоомные резисторы, определяющие

15 пороги срабатывания однопороговых дискриминаторов, с заданной точностью уже для величин порогов 7,8. Это в свою очередь, ограничивает число входных переменных элемента, от которых реализуется многопороговая функция.

Наиболее близким по технической сущности к изобретению является многопороговый логический элемент, содержащий резистивный делитель, вход которого подключен к положительному полюсу источника питания, выходы соединены с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход. каждого из которых соединен с выходом последующего логического элемента

И-НЕ L2J.

Недостаток известного устройстванизкая технологичность при интегральном исполнении при числе входов свыше

5-6.

Цель изобретения - повышение технологичности при интегральном исполнении.

Поставленная цель достигается тем, что в многопороговый логический we-:.: мент четности, содержащий резистивный делитель, вход которого подключен к положительному полюсу источника питания, выходы соединены с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, 3 9286 второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ, RS-триггер на логических элементах И-НЕ, вход уста" новки в ноль которого подключен к ши- 5 не стробирующего сигнала, дополнительно введены линейный сумматор с парафазным .выходом,,два транзистора, вход установки в единицу RS-триггера соединен с входом логического элемен- 10 та И-HE с наибольшим порогом срабатывания, прямой и инверсный выходы

RS-триггера подключены соответственно к базам второго и первого дополнительных транзисторов, коллекторы . 15 которых объединены и подключены к выходу резистивного делителя, эмиттер: первого дополнительного транзистора подключен к прямому выходу линейного сумматора, эмиттер второго дополни- 20 тельного транзистора подключен к инверсному выходу линейного сумматора.

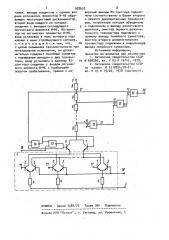

На чертеже приведена принципиальная схема многопорогового логического элемента четности. 25

Иногопороговый логический элемент четности содержит линейный сумматор 1 с парафазным выходом, содер>нащий для каждого входа переключатель

30 тока на транзисторах 2 и 3, эмиттеры которых через резистор 4, определяющий вес входа, подключены к отрица" тельному полюсу источника 5 питания.

О

Коллекторы транзисторов 2 подключены к эмиттеру первого дополнительного транзистора 6. Коллекторы транзисто. ров 3 соединены с эмиттером второго дополнительного транзистора 7, коллектор которого соединен с коллектором первого дополнительного тран40 зистора 6 и через деЛитель из резисторов 8 подключен к положительному полюсу источника 9 питания, Иногопороговый дискриминатор состоит из последовательно соединенных двухвходовых логических элементов И-НЕ 10, Вход 11 каждого элемента И-HE 10 соединен с соответствующим резистором 8 делителя, развязывая, тем самым, каждый последующий дискрими,натор с меньшим порогом срабатывания от предыдущего. Вход 12. каждого элемента И-НЕ соединен с выходом 13 элемента И-НЕ с ближайшим меньшим порогом срабатывания. Вход установки в ноль RS-триггера на логических элементах И-НЕ 14 и 15 подключен к шине 16 стробирующих сигналов, а

53 4 вход установки в единицу соединен со входом 11 логического элемента ИНЕ 10 с наибольшим порогом срабатывания. Выход логического элемента ИНЕ 15, являющийся инверсным выходом

RS-триггера, подключен к базе первого дополнительного транзистора 6.

Выход логического элемента И-НЕ l4, являющийся прямым выходом RS-триггера, соединен с базой второго дополз нительного транзистора 7. Входные клеммы l7 линейного сумматора соединены с базами транзисторов 2. Базы транзисторов 3 подключены к клеммам l8 источника опорного напряжения, Клемма 19 подключена к положительному полюсу источника питания. Выходные сигналы многопорогового логического элемента четности снимаются с выхода 20.

Источники питания и опорного напряжения на чертеже не показаны. Одно. пороговый дискриминатор на элементе И-НЕ 10, один из входов которого соединен с клеммой 19, имеет наименьший порог срабатывания. Однопороговый дискриминатор на элементе

И-НЕ 10, выход которого является выходом многопорогового логического элемента четности, имеет наивысший порог срабатывания.

Принцип работы рассмотрим на примере восьмивходового многопорогового логического элемента четности.

Значения весовых коэффициентов входов линейного сумматора равны единице. Пороги срабатывания дискриминаторов на элементах 10 равны:

Т =1, Т2 — — 2, Т =3 1q

Перед началом работы в шину l6 поступает стробирующий сигнал, устанавливая RS-триггер на элементах

И-НЕ 14 и l5 в нулевое состояние.

При этом на выходе элемента И-НЕ

15 устанавливается высокий уровень напряжения, открывающий транзистор

6, включенный в цепь прямого выхода линейного сумматора 1. На выходе элемента И-НЕ 14 устанавливается низкий потенциал, который закрывает транзистор 7, включенный в цепь инверсного выхода линейного сумматора 1.

Если на все входные клеммы 17 линейного сумматора 1 поданы низкие уровни напряжения, соответствующие нулевым значениям переменных, то все транзисторы 2 закрыты, Формула изобретения

Иногопороговый логический элемент четности, содержащий резистивный делитель, вход которого подключен к положительному полюсу источника пи5 92865 а транзисторы 3 открыты, Однако ток через цепь резисторов 8 отсутствует, поскольку транзистор 7 закрыт. Это приводит к тому, что на входах 11 всех логических элементов И-НЕ 10 5 присутствует высокий потенциал, который определяет высокий уровень напряжения на выходе 20, соответствующий логической единице.

Если положительный потенциал

10 присутствует только на одной из входных клемм 17 линейного сумматора 1, то соответствующий транзистор

2 открываетсл, а транзистор 3 закрывается. При этом ток от положительного полюса источника 9 питания через резисторы 8, открытые транзисторы 6 и 2 и резистор 4 поступает к отрицательному полюсу источника 5 питания. Потенциал на входе 11 логического элемента И-НЕ 10 с порогом срабатывания Т-1 понижается, что приводит к появлению на его вы. ходе высокого потенциала, а на выходе 20 устанавливается низкий уровень 5 напряжения, соответствующий логическому нулю. Если на входные клеммы

17 линейного сумматора подан двоичный набор, содержащий две или три единицы, то открываются соответствен-З0 но два или три транзистора 2, закрываются два или три транзистора 3 и срабатывают однопороговые дискриминаторы на логических элементах

И-НЕ 10 с порогами Т =1, Т =2 или з5

T =1, T =2, Т =3. В первом случае на выходе 20 многопорогового логического элемента присутствует высокий уровень напряжения, во второмнизкий, что соответствует логической 40 единице и нулю.

Число открытых транзисторов 2 и 3 линейного сумматора 1 всегда равно числу входов элемента. Кроме того, 45 если число открытых транзисторов 2 четно (нечетно), то четно (нечетно) и число открытых транзисторов 3.

Указанное свойство используется,для организации работы многопорогового

50 логического элемента четности при наличии во входном коде четырех или более единиц. При поступлении на входные клеммы 17 линейного сумматора четырех единиц, открываются соот55 ветствующие четыре транзистора 2 и закрываются четыре транзистора 3. Ток, протекающий через цепь резисторов 8, вызывает понижение потенциала в точке 21 до величины, достаточной для того,чтобы RS-триггер изменил свое состояние на противоположное. Это приводит к закрываюнию транзистора 6 и о ткрыванию транзистора 7, подключенного к инверсному выходу линейного сумматора 1 ° Количество открытых тран. зисторов 3 линейного сумматора 1, в рассматриваемом случае, также равно четырем, поэтому в точке 21 сохраня" ется низкий потенциал и на выходе 20 многопорогового элемента устанавливается высокий уровень напряжения,соответствующий логической единице. о

При поступлении на входные клеммы

17 линейного сумматора 1 пяти, шести, семи или восьми переменных, равн 4х единице, RS-триГгер устанавливается в единичное состояние, закрывает транзистор 6 и открывает транзистор 7, подключая, тем самым, цепь делителя из резисторов 8 к инверсно" му выходу линейного сумматора. В этом случае оказываются открытыми три, два, один или ни одного транзистора 3 линейного сумматора 1 и срабатывают соответственно три, два, один или ни одного дискриминатора на элементах И-НЕ 10 с порогами Т вЂ” — 1, Т =2, Т =3. При срабатывании трех или одного дискриминатора на выходе

20 формируется низкий уровень напря" .жения, соответствующий логическому нулю. Если срабатывают два однопороговых дискриминатора или не срабаты" вает ни один, то на выходе 20 появляется высокий уровень напряжения, соответствующий логической единице.

Указанные изменения в структуре многопорогового логического элемента позволяют при реализации функции четности в два раза сократить число порогов у многопорогового дискриминатора за счет исключения однопороговых дискриминаторов с порогами срабатывания — +1; -+2,...,п. Это приво"

n, yl дит к улучшению технологичности при производстве элементов в интегральном исполнении за счет исключения наиболее высокоомных высокочастотных резисторов из резистивного делителя.

1 !

1

I !. ВНИИПИ . Заказ 3284/76 Тираж 954 Подписное филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

7 9286 тания, выходы соединены с одними вхо дами логических элементов И-HE образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ, RS-триггер на логических элементах И-НЕ, вход установки в ноль которого подключен к шине стробирующего сигнала, отличающийся тем, что, 10 с целью повышения технологичности при интегральном исполнении, он дополнительно содержит линейный сумматор с парафазным выходом и два транзистора, .вход установки в единицу RS- )s триггера соединен с входом логического элемента И-НЕ с наибольшим порогом срабатывания, прямой и ин53 8 версный выходы RS-триггера подключены соответственно к базам второго и первого дополнительных транзисторов, коллекторы которых объединены и подключены к выходу резистивного делителя,. эмиттер первого дополнительного транзистора подключен к прямому выходу линейного сумматора, змиттер второго дополнительного транзистора подключен к инверсному@ выходу линейного сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

И 608266, кл. Н 03 К 19/42, 1978.

2. Авторское свидетельство СССР по заявке Н 2718834/18-21, кл. Н 03 К 19/20, 1978 {прототип).