Устройство программного управления исполнительными механизмами

Иллюстрации

Показать всеРеферат

iii930274

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ С®ИДЕТЕЛЬСТВУ

Союз Советскнк

Соцналистнческнк

Республик (61) Дополнительное к авт.санд-ву(Sl)M. Кл.

G 05 В 23/02 (22) Заявлено 2 7,02.80 (2 l )2888288/18-24 с присоединением заявки М

Пкударетааклай кемнтет

СССР ао делам лза4рателил и еткрытнй (23) Приорнтет

Опубликовано 23.05.82. Бюллетень М 1g

Дата опубликования описания 27,05.82 (53) УДК еа-50 (088.8).

И. .;„ ям м »= ь

» j 1

Специальное конструкторское бюро Титан (71) Заявитель (54) УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ

ИСПОЛНИТЕЛЬНЫМИ МЕХАНИЗМ АМИ

Изобретение отнссится к автоматике и может быть использовано в системах управления различным технологическим оборудованием.

Известно устройство управления с последовательной обработкой входных снг

5 палов, содержащее коммутатор входных сигналов, логический блок, обеспечивающий последовательную обработку входных сигналов и формирсвание выходных управ ляюших сигналов, а также программируемую память, адресный регистр, указывающий адрес входа нли выхода, дешифратор и выходной регистр для хранения выход» ных управляющих сигналов и выдачи нх . на исполнительные механизмы.

Выхопные управляющие сигналы, сформированные в логическом блоке, посту лают на триггеры выходного регистра, Выбор требуемого триггера осуществляется дешифратором по адресу, указаню20 му в адресном регистре (1).

Недостатком устройства является отсутствие ксегтроля правнльнос ги записи выходных управляющих сигналов,в триггеры выходного реестра.

Наиболее близким техническим решением к предлагаемому изобретению является устройство, которое содеркит адресную шину, шину синхронизации, шину "За-. пись 1, шину «Запись О», дешифратор, группу элементов И, группу 7-К триггь ров выходного регистра и коммутатор.

Адресная шина устройства соединена с входом дешифратора и с адресным входом коммутатора.. Выходы двшифратора соединены с первыми входами логических схем

И, вторые входы которых соединены с ппе ной синхронизадии. Выход каждого smмента И соединен с синхрснизируюшим входом соответствующего триггера вье» хопного регистра. Шины «Запись 1» и

Запись 0 устройства сюе вгнены соей» ветственно с, входами T и К триггеров выходы которых соединены с исполнительными механизмами тг с соответствующими информационными входами коммутатора.

930274 4

Выход коммутатора является контрольным выходом устройства.

При поступлении кода адреса по адресной шине на вход дешифратора посжц-, ний подготавливает соответствующий эж- 5 мент И к прохождению через него импу льса синхронизации на выбранный триггер выходного регистра. Одновременно с кодом адреса подается сигнал по одной иэ шин Запись l или "Запись О, в зави- . симости от того, в какое состояние должен быть установлен выбранный триггер.

Затем поступает импульс синхронизации. и перевоцит данный триггер в требуемое состояние. Аналогично происходит переключение остальных триггеров выходного регистра. Контроль правильности установки каждого триггера осуществляется с помощью коммутатора, т.к. его выходной сигнал в каждый цанный момент вре- о мени соответствует состоянию триггера, код адреса которого установлен на адресной шине (2g .

Недостаток известного состоит в том, что его схема предлагает программную реализацию контроля правильности установки триггеров в заданное состояние.

Действительно, чтобы опре целить соответствует ли новое состояние триггера за1 данному, необходимо запомнить, какой из ЗО сигналов (Запись О или Запись 1 ) был подан на его вход, затем после установки триггера опросить через коммутатор его выход и сравнить состояние выхода с поцававшимся входным сигналом. Та-zs кая организация контроля .требует,. по крайней мере, выполнения двух дополнительных команц - считывание состояния триггера и сравнение. Все это приводит к уцлинению программы управления и, ао следовательно, к снижению быстроцейст вйя устройства и к увеличению объема памяти программ, Hemü изобретения - повышение быстроцействия и упрощение устройства путем уменьшения объема памяти программ в системе управления, составной частью которой является данное устройство, путем аппаратной реализации контроля правильности установки триггеров выходного регистра.

Поставленная цель достигается тем, что в устройство, соцержашее дешифратор, выходы которого через соответствующие эжменты И и триггеры соединены с соот-. ветствуюшими информационными входами коммутатора и с выходами устройства, адресный вход коммутатора и вход цешифратора подключены к адресной шине, втopble входы элементов И подключены к шине синхронизации, вторые входы триг геров - к шине Запись 1», а третьи входы триггеров - к шине Запись О ", введе-- ны последовательно соединенные элемент

НЕ, первый дополнительный элемент И, эжмент ИЛИ, второй дополнительный элемент И и триггер, третий дополнительный элемент И и эжмент зацержки, @br» ход которого подключен к второму входу второго дополнительного элемента И, а вхоц — к шине синхронизации, выход коммутатора соецинен с входом элемента HE и через третий дополнительный эжмент

И с вторым входом элемента ИЛИ, вторые вхоцы первого и третьего цополни-; .

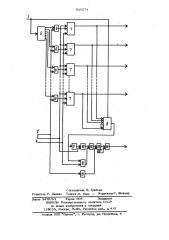

1 тельных элементов Й поцключены соответстственно к шинам Запись 1" и Запись О, На чертеже показана схема предлагаемого устройства.

Устройство управления содержит адресную шину 1, шину 2 синхронизации, шину 3 «Запись 1», шину 4 "Запись 0, а.цешифратор 5, группу элементов И 6,, группу триггеров 7 выходного регистра, коммутатор 8, элемент HE 9, первый дополнительный элемент И 10, второй дополнительный элемент И 11, эжмент

ИЛИ 12, третий дополнительный элемент

И 13, триггер 14 ошибки и элемент 15 задержки. Адресная шина 1 связана с вхо. дом дешифратора 5 и с адресным входом коммутатора 8. Выходы цешифратора 5 соединены с первыми входами эжментов

И 6 группы, вторые входы соединены с шиной 2 синхронизации, а выхоцы - с синхрониэируюшими входами - К триггеров 7 выхоцного регистра. Шина Запись

1" соединена с Т -входами триггеров 7, а также с вторым входом первого дополнительного эжмента И 10. Шина Запись

0 соединена с К-входами триггеров 7, а также с вторым входом второго цополнительного элемента И 11. Выходы триг геров 7 соединены с исполнительными механизмами (не показаны) и с соответствуюшими информационными входами коммутатора 8. Выход коммутатора 8 соединен с первым входом второго дополнительного элемента И 11 через элемент НЕ

9 с первым входом первого цополнительного элемента И 10. Выходы дополнитель. ных элементов И 10 и 11 соецинены с элементом ИЛИ 12, выход которого соединен с первым входом третьего дополнительного элемента И 13. Второй вхоц третьего дополнительного элемента И 13 соединен с шиной 2 синхронизации через

5 930 элемент задержки 15, а выход — с входом Установка 1 триггера ошибки 14, второй вход которого используется для установки его в исходное состояние.

Устройство работает слецуюшим образом. При поступжнии кода адреса по адресной шине 1 на вход дешифраторв 5 послешгий поцготввливает соответствующий элемент. И 6 к прохождению через него импульса синхронизации. Одновременно с коцом адреса подается сигал либо .по шине 3 Запись 1", либо по шине 4 Запись О», в зависимости от того, в какое состояние должен быть установжн выбранный триггер 7 выходного регистра.

Поступающий затем импульс по шине 2 синхронизации переводит триггер 7 в требуемое состояние. Так как адресный код . одновременно поступает и нв коммутатор

8, то на его выходе появляется сигнал, соответствуюший состоянию переключаемого триггера 7. Этот сигнал совместно с сигналами на шинах Запись 1 и Запись 0 анализируется дополнительными элементами, введенными в устройство.

При неправильной установке выбранного триггера 7 на выходе элемента ИЛИ 12 устанавливается еакничный уровень, поэтому эацержанный сигнал синхронизации с шины 2 через третий дополнительный элемент И 13 устанавливает .в единичное состояние триггер 14 ошибки. Условиями формирования единичного уровня сиг нала на выходе третьего дополнительного элемента 13 являются единичный сигнал нв шине 3 Запись 1 и нулевой сигнал на выходе коммутатора 8, что приводит к срабатыванию первого дополнительного элемента И 10; единичный сигал на шине 4 Запись О, и единичный сигнал на выходе коммутатора 8, что приводит к срабатыванию второго дополнительного эжмента И 11.

Иэ приведенного описания схемы и работы предлагаемого устройства вицно, что при кажцом переключении любого триггера

7 выходного реестра можно проконтролировать правильность его установки в тре буемое состояние по выходному сигналу триггера ошибки 14, При этом не требу ются дополнительные затраты времени.

Таким образом, предлагаемое техниче-. ское решение позволяет аппаратными срзц274 устройства.

1О

35 стввми осуществлять контроль правильности установки триггеров выходного регист ра. Переход от программной реализации контроля к аппаратной приводит к уменьшению числа, комвнц в программе управжння, что, в свою очередь, обеспечивает уменьшение требуемого обьема памяти программ и повышение быстродействия

Формула изобретения

Устройство программно го управления исполнительными механизмами содэржвщее дешифратор, выходы которого через соответствующие элементы И и триггеры соединены с соответствующими информационными входами коммутатора и с выходами устройства, адресный вход комму татора и вход дешифратора подключены к адресной шине, вторые входы элементов И подключены к шине синхронизации1вторые входы триггеров - к шине "Запись 1, а третьи входы триггеров - к шине Запись

О», о т л и ч в ю щ е е с я тем, что, с целью повышения быстродействия и уп рощения устройства, в него введены пос ледовательно соединенные элемент НЕ, первый дополнительный элемент И, элемент ИЛИ, второй дополнительный эжмент И и триггер, а также третий дополнительный эжмент И и эжмент задержки, выход которого подключен к второму вхо-. ду второго цополнительного эжмента И, а вход - к шине синхронизации, выход коммутатора соединен с входом элемента

НЕ и через третий дополнительный элемент И с вторым вхоцом эжментв ИЛИ, вторые входы первого и третьего допоп нительных элементов И подключены соответственно к шинам Запись 1» и За лись О.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании

Ж 2004088, кл. G 05 В 15 02, опублик. 1977.

2. Патент Японии М 63-38394,кл. G 05 В 23/02, опублик. 1978 (протеже .

930274

Составитель В. Грибова

Редактор P. Бицика Техред М. Надь р Корректор С. Шекмар

Заказ 3470/63 Тираж 908. Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-Ç5, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4