Устройство для выборки элементов памяти в накопителе

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (930385

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сете з Сееетсннк

Социалистически к республик (61) Дополнительное к авт. саид-ву— (22) Заявлено 16. 09.80 (21) 2982607/18-24 (51)М. Кл.

G 11 С 11/40 с присоединением заявки М— (23) Приоритет3Ьсударстеваыв кепатвт

CC C1 ю аеаам яэвбфвтекк1 я еткрытяй

Опубликовано 23. 05. 82. Бюллетень М 1 9 (53) УД К 681. 327. .6(088.8) Дата опубликования описания 23.05. 82

Н. А. Подопригора, Э. П. Калошкин, Т. Я. Мамедов, l0. И. Савотин и А. И. Сухопаров

/

-, (72) Авторы изобретения (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫБОРКИ ЭЛЕМЕНТОВ

ПАИЯТИ В НАКОПИТЕЛЕ

Изобретение относится к вычислительной технике и может быть исполь-! зовано в запоминающих устройствах.

Известны устройства для управления элементами памяти динамического типа на биполярных транзисторах которые содержат п-р-п транзисторы и ,построены по ключевой схеме l1) и 523.

Известные устройства имеют малую надежность.

Наиболее блиэкин по технической .сущности является устройство, которое содержит один двухэмиттерный и два одноэмиттерных транзистора ()).

Это устройство имеет низкую надежность, обусловленную тем, что в процессе формирования сигнала выборки при считывании шина управления переключает большой ток, а амплитуда сигнала по шине выборки элементов памяти при считывании невелика.

Цель изобретения - повышение надежности устройства для выборки элементов памяти в накопителе..

Поставленная цель достигается тем, что в устройство для выборки элементов памяти в накопителе, содержащее двухэмиттерный и-р-и транзистор, база которого соединена с адресной ши. ной, первый эмиттер — с шиной выборки элементов памяти при записи, а второй эмиттер - с шиной выборки элементов памяти ири считывании, и-р-и транзистор, коллектор которого соединен с вторым эмиттером двухэмиттерного п-р-п транзистора и через нагрузочный резистор с первой шиной питания, шину управления и вторую шину питания, введен р-и-р транзистор, база которого подключена к шине ,управления, коллектор - к базе и-р-и транзистора, а эмиттер — к адресной шине, причем коллектор двухэмиттерного и-р-и транзистора подключен к первой шине питания, а эмиттер и-р-и транзистора - к второй шине питания.

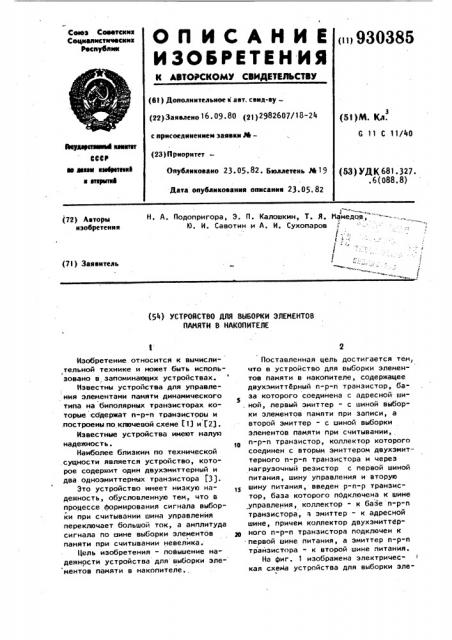

На фиг. 1 изображена электричес" кая схема устройства для выборки элеФормула изобретения

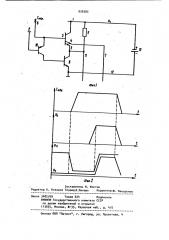

3 930 ментов памяти в накопителе; на фиг.2диаграмма работы устройства.

Устройство содержит первую шину 1 питания, шину 2 управления двухэмиттерный и-р-и транзистор 3 с двумя эмиттерами 4 и 5, адресную шину 6, шину 7 выборки элементов памяти при записи, и-р-и транзистор 8, нагрузочный резистор 9, р-и-р транзистор 10, шину ll выборки элементов памяти при считывании, вторую шину

12 питания, источник 13 питания.

Устройство работает следующим образом.

8 режиме покоя ток Q â ыине б и напряжение на шине 2 равны нулю.

Напряжение на шине 11 (U< 3 равно напряжению шины 1 (О !), а напряжение на шине 7 равно нулю, так как транзистор 3 закрыт. Поступление в шину 6 адресного тока приводит к включе нию транзисторов 10 и 8. Потенциал шины .11 понижается до величины, рав-. ной остаточному напряжению между коллектором и эмиттером.насыщенного транзистора 8, и происходит считывание информации из элементов памяти.

Затем повышается потенциал шины 2, что вызывает отпирание транзистора 3, увеличение напряжения на шинах 11 и

7 и проведение. записи в элементы памяти. Формирование временной диаграммы управления элементами памяти завершается выключением тока в шине 6 и понижением напряжения на шине 2 (0 ). Потенциал шины 7 (0.) падает до нуля, а потенциал шины 11 остается равным напряжению шины l.

Предлагаемое устройство позволяет уменьшить по сравнению с известным ток нагрузки по шине управления, 385. 4 уменьшить значение напряжения логического нуля, т.е. увеличить амплитуду сигнала, по шине выборки элементов памяти при считывании, что повышает надежность устройства.

1в Устройство для выборки элементов памяти в накопителе, содержащее двухэмиттерный и-р-fl транзистор, база которого соединена с адресной шиной, первый эмиттер — с шиной выборки эле 5 ментов памяти при записи, а второй эмиттер — с шиной выборки элементов памяти при считывании, и-р-и транзистор, коллектор которого соединен с вторым эмиттером двухэмиттерного и-р-и транзистора и через нагрузочный резистор с первой шиной питания, шину управления и вторую шину питания, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введен р-и-р транзистор, база которого подключена к шине управления, коллектор - к базе и-р-и транзистора, а эмиттерк адресной шине, причем коллектор

5в двухэмиттерного и-р-и транзистора подключен к первой шине питания, а эмиттер и-р-и транзистора - к второй шине питания.

Источники информации, принятые во внимание при экспертизе

1. Патент США М 3827034, tea. 340-173, уб . 1974.

2. Патент франции М 2176709, кл. G 11 С 7/00, опублик. 1973.

40 3. 1SS СС Digest of Techn1саl

Papers, 1978, рр.194-155 (прототип).

Составитель В. Костин

Редактор A. Козориэ ТехредЛ.Пекарь Корректор Ю. Макаренко

Заказ 3482/69 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и .открытий

313035, Москва, 3-35, Рауиская наб., д. 4/5

Оилиал ППП "Патент", г. Ужгород, ул. Проектная, 4