Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соватсиин

Социалистические республик

< 930388 (61) Дополнительное к авт. свид-ву (22) Заявлено 26. 02. 79 (21) 2730076/18-24 (51)М. Кл., с присоединением заявки М

G 11 С 29/00

3Ьеудлрстееннмй кемнтет

СССР не делам нэебретеннН н еткрытнй (23) Приоритет

Опубликовано 23. 05. 82 ° Бюллетень М 19

Дата опубликования описания 25. 05. 82 (53) УД К681 327 .66(088.8) (72) Авторы изобретения

A. Д. Доля и Л. И. Кириченко (7l ) Заявитель

I чс;-. с (54) ЗАПОМИНЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к цифровой вычислительной технике и может быть применено в цифровых вычислительных машинах и системах.

Известны запоминающие устройства (ОЗУ), в которых защита адресного тракта может быть осуществлена с помощью контрольного кода адреса, сопровождающего каждое слово информации в ОЗУ при хранении, либо с помощью суммарного контрольного кода слова и адреса, по которому это слово хранится (11.

Недостатком таких ОЗУ является невозможность осуществления предварительного контроля путем записи, последующего чтения информации из ячеек и сравнения записанной и прочитанной информации.

Наиболее близким по технической сущности является запоминающее устройство, содержащее последовательно соединенные регистр адреса и дешифратор, блок оперативных запоминающих матриц и постоянную запоминающую матрицу, входы которых соединены с выходом дешифратора, усилители считывания-записи и усилители считывания, входы которых соединены соот5 ветственно с выходами блока оперативных запоминающих матриц и постоянной запоминающей матрицы, регистр слова и регистр контрольного кода, входы которых соединены соответстio венно с выходами усилителей считывания-записи и усилителей считывания, и блок контроля, три входа которого соединены соответственно с выходом регистра слова, регистра

I5

I контрольного кода.и регистра адреса (21.

Недостатком такого запоминающего устройства является его недостаточ ная надежность.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что запоминающее устройство с

930388 ф

1О

2О

50 э5 самоконтролем содержит последовательно соединенные регистр адреса и дешифратор, выходы дешифратора подключены к входам блока матричных накопителей, оперативной и постоянной памяти, входы-выходы матричных накопителей оперативной памяти соединены с входами-выходами усилителей записи-считывания, выходы матричного накопителя постоянной памяти соединены с входами усилителей считывания, входы-выходы усилителей считывания подключены к входам регистра слова, выходы усилителей считывания соединены с входами регистра контрольного кода, выходы регистра слова и регистра контрольного кода соединены с входами блока контроля, в него введены элемент И, узел блокировки, блок определения неисправной комбинации, регистры неисправного кода, первые входы которых подключены к выходу блока контроля, вторые — к выходу регистра адреса и соответствующему входу блока контроля. Выходы регистров неисправного кода соединены с входами блока определения неисправной комбинации, выход которой соединен с третьим входом одного из регистров неисправного кода и входом узла блокировки, первый и второй входы элементов.

И соединены соответственно с выходом узла блокировки и выходом регистра слова.

Блок определения неисправной комбинации содержит элемент сравнения, первый, второй и третий регистры, вход третьего регистра подключен к одному из входов элемента сравнения, другие входы которого являются входами блока, выходы элемента сравнения подключены к входам соответствующих регистров, выход третьего регистра является выходом блока.

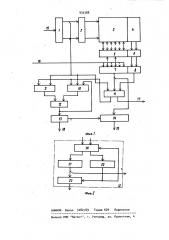

На фиг. 1 представлена структурная схема устройства; на фиг. 2блок определения неисправной комбинации.

Устройство содержит регистр 1 адреса, дешифратор 2 адреса, блок

3 матричных накопителей оперативной памяти, блок 4 матричных накопителей постоянной памяти, хранящий контрольный код адреса соответствующих ячеек, усилители 5 считывания-записи, усилители 6 считывания, регистр

7 слова, регистр 8 контрольного кода, фиксирующий контрольные разряды адреса, сопровождающие каждое слово информации, первый и второй регистры

9 и 10 неисправного кода, блок 11 контроля, блок 12 определения неисправной комбинации, узел 13 блокировки обращения и элемент И 14.

Запоминающее устройство подключается к внешним абонентам с помощью следующих шин: 15 - входные шины адреса; 16 - входные шины слова;

17 - шина сигнала ошибки; 18 — шины кода блокировки неисправного адреса;

19 - выходные шины слова.

Регистр 1 адреса подключается к двшифратору 2, выходы которого соединены с входными адресными шинами блока 3 запоминающих матриц, регистр

7 слова подключен к усилителям 5 считывания-записи, а выход регистра 7 соединен со входом блока 11 контроля.

Входы регистров 9 и 10 соединены с выходом регистра 1 адреса, а выходы регистров 9 и 10 подключены к входам блока 12 определения неисправной ком бинации, выход узла 13 блокировки обращения выдает на схему И 14 код адреса неисправной комбинации.

Блок 3 и секции 4 управляются об.щим дешифратором 2 адреса. При обра. щении по любому адресу следует обращение в блок 3 (для чтения или записи информации) и секцию 4 (только . для чтения хранящейся информации) ° .-Секция 4 используется для хранения

35 контрольного кода адреса ячейки, в которую следует обращению.

Блок 12 определения неисправной комбинации содержит элемент 20 сравнения, первый регистр 21 (кода сравнившихся разрядов), второй регистр ао

22 (признаков сравнения разрядов), блок 23 выдачи кода.

Устройство работает в режимах записи и чтения информации как обычное оперативное запоминающее устройв ство.

При записи информации в оперативное .запоминающее устройство адрес ячейки, находящийся на входных шинах 15 адреса и записываемое слово, находящееся на входных шинах 16 слова, поступают соответственно на регистр 1 адреса и регистр 7 слова.

Поступивший адрес через дешифратор

2 адреса выбирает необходимую ячейку блока 3 и через усилители 5 считывания-записи и блок 3 записывается состояние регистра 7. Одновременно по адресу, зафиксированному на

5 93 регистре 1, через дешифратор 2 из блока 4 матричных накопителей постоянной памяти на регистр 8 выбирается контрольный код адреса. Адрес с регистра 1 адреса поступает в блок

11 контроля, сворачивается и сравнивается с состоянием регистра 8.

В случае несоответствия блок 11 выдает сигнал ошибки на шины 17 и на управляющие входы регистров 10 и 9.

Это говорит о неисправности адресного тракта, в частности об отказе выхода ступени дешифратора. Устройство переходит в режим определения отказавшего выхода ступени дешифратора. Псевдоисправный адрес при следующем обращении с регистра 1 адреса переписывается на регистр 9 неисправного адреса по сигналу управления из блока 11. Следующий псевдоисправный адрес фиксируется на регистре 10 неисправного адреса. В блоке 12 определения неисправной комбинации происходит выделение об" щей части кодов всех псевдоисправных адресов.

Элемент 20 сравнения производит сравнение кодов, находящихся на регистрах 9 и 10. Коды сравнившихся разрядов фиксируются на регистре

21, а признаки сравнения поразрядно - на регистре 22.

В блоке 13 блокировки обращения выделяются разряды кода адреса, определяющие отказавшую ступень и выход дешифратора для выдачи их на шины 18, блокируя тем самым обращение во все ячейки ОЗУ, за исключением ячейки или группы ячеек, выбираемой оказавшим выходом дешифратора.

Чтение информации из запоминающего устройства происходит аналогично описанному выше для операции записи. Адрес поступает на регистр 1 через вход 15, а прочитанное слово выдается на шины 19 через элемент

И 14 при отсутствии сигнала блокировки из блока 13.

Предлагаемое устройство позволяет выявить ошибки в адресном трак- те, блокировать обращения в часть

ОЗУ, непригодную для использования, оохранить работоспособной остальную часть ОЗУ, что увеличивает надежность запоминающего устройства.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее последователь0388 6

15 го

25 зо

50 но соединенные регистр адреса и дешифратор, выходы дешифратора нодключены к входам блока матричных накопителей оперативной и постоянной памяти, входы-выходы матричных накопителей оперативной и постоянной памяти соединены с входами-выходами усилителей записи-считывания, выходы матричного накопителя постоянной памяти соединены с входами усилите" лей считывания, входы-выходы усилителей считывания подключены к входам регистра слова, выходы усилителей считывания соединены с входами регистра контрольного кода, выходы регистра слова и регистра контрольного кода соединены с входами блока контроля, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены элемент

И, узел блокировки, блок определения неисправной комбинации, регистры неисправного кода, первые входы которых подключены к выходу блока контроля, вторые — к выходу регистра адреса и соответствующему входу блока контроля, выходы регистров неисправного кода соединены с входами блока определения неисправной комбинации, выход которой соединен с третьим входом одного из регистров не" исправного кода и входом узла блокировки первый и второй входы элеменЭ та И соединены соответственно с выходом узла блокировки и выходом регистра слова.

2. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что блок определения неисправной комбинации содержит элемент сравнения, первый, второй и третий регистры, вход третьего регистра соединен с выходом второго регистра, вход-выход третьего регистра подключен к одному из входов элемента сравнения, другие входы которого являются входами блока, выходы элемента сравнения подключены к входам соответствующих регистров, выход третьего регистра является выходом блока.

Источники информации, принятые во внимание при экспертизе;

1. Авторское свидетельство СССР

И 333559, кл. G 06 F 11/08, 1970.

2. Авторское свидетельство СССР

N 335718, кл. G 11 C 11/00, 1970 (прототип).