D-триггер

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соаетсинк

Социалистичесник

Респубпик (»)930597 (61) Дополнительное к авт. спид-ву

b (22) Заявлено14. 11. 80 (21) 3004417/18-21 с присоединением заявки М (23) Приоритет (5! )М. Кл.

Н 03 К 3/286

3Ьаудврствевный камитвт

CCCP аа делвм ивавретенвй н аткрыткй

Опубликовано 23.05 ° 82 ° Бюллетень 1ггЪ 19

Дата опубликования описания 23:05. 82 (53) УД К 621. 373. .544(088.8) г

1 (72) Авторы

-изобретения т

В.П.Грибок, С.В.Солецкий и А.И.Воловик j;r = г

Г

Р г (71) Заявитель (54) О "ТРИГГЕР

Изобретение относится к импульсной и вычислительной технике и может быть использовано при построении различных устройств дискретной обработки информации на схемах с непосредственными связями.

Известен О-триггер, содеркаций основной триггер на элементе 2И-2ИЛИ-НЕ и инверторе, через который выход элемента 2И-2ИЛИ-НЕ основного триггера та соединен с первым входом первого входа И элемента 2И-2ИЛИ-НЕ основного триггера, и вспомогательньпг триггер на двух элементах И-ИЛИ-НЕ 11 .

Однако этот О-триггер имеет слож3S ную схему и обладает узкими функциональными возможностями: информационный вход D подключается непосредственно к основному триггеру, что не

20 дает возможности получения пгирокого класса входных логических функций, кроме того, при включении обратной связи с выхода вспомогательного триггера на вход О, в О-триггере не обеспечивается устойчивого режима счета.

Известен также О-триггер, содержащий первьпг и второй элементы И-ИЛИ-НЕ, первый и второй инверторы и элемент

И-НЕ, первьп1 и второй входы которого соединены соответственно с О-вхо-дом и тактовыМ входом D-триггера, выход элемента И-НЕ соединен с первыми входами первой и второй групп входов по И первого элемента И-ИЛИ-НЕ, выход которого соединен с первым входом первой группы входов по И второго элемента И-ИЛИ-НЕ с входом первого инвертора, выход которого соединен со вторым входом первой группы входов по И первого элемента И-ИЛИ-НЕ, второй вход второй группы входов по И первого элемента -IQIH-HE соединен с так товым входом О-триггера и первым входом второй группы входов по И второго элемента И-ШЫ-НЕ, второй вход второй группы входов по И ко горого соединен с выходом второго ынвертора (21. ность.

Целью изобретения является упрощение О-триггера.

Поставленная цель достигается тем, что в D-триггере, содеряацем первый и второй элементы И-ИЛИ-ПЕ, первый и второй инверторы и элемент И-НЕ, первый и второй входы которого соеди- 10 нены соответственно с 0-входом и тактовым входом О-триггера, выход элемента И-НЕ соединен с первыми входами первой и второй групп входов по

И первого элемента И-ИЛИ-НЕ, выход 15 которого- соединен с первым Иходом первой группы входов по И второго элемента И-ИЛИ-НЕ и входом первого инвертора, выход которого соединен со вторым входом первой группы входов по И первого элемента И-ИЛИ-НЕ, второй вход второй группы входов по И первого элемента И-ИЛИ-НЕ соединен с тактовым входом 0-триггера и перВым Входом второи группы Входов по

И второго элемента И-ИЛИ-НЕ, второй вход второй групггы входов по И которого соединен с выходом второго инвертора, вход второго инвертора соединен с выходом второго элемента

И-ИЛИ-НЕ, второй вход первой группы входов по И которого соединен с выходом элемента И-НЕ.

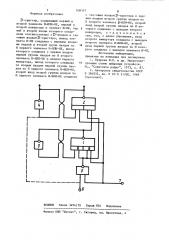

На чертеие показана структурная схема О-триггера.

Р-триггер содерхсит первый и вто—

35 рой 2 элементы И-ИЛИ-НЕ, первый 3 и второй 4 инверторы и элемент И-НЕ 5, первый и второй входы которого соедипецы соответственно с О-входом 6 и

40 тактовым входом 7 О-триггера, выход элемента И-НЕ 5 соединен с первыми входами первой и второй групп в> г>дов по И первого элемента И-ИПИ-НЕ l выход которого соединен с первым входом первой группы входов по И второ45

ro элемента И-ИЛИ-НЕ 2 и входом первого инвертора 3, выход которого соединен со вторым входом первой группы входов по И первого элемента ИИЛИ-НЕ 1, соединен с тактовым входом 7 0-триггера и первым входом втоpotl группы входов по И второго элемента И-ИПИ-НЕ 2, второй вход второй группы входов по И которого соединен с выходом второго инвертора 4, 55 а вход второго инвертора. 4 соединен с выходом второго элемента И-HJ1H-НЕ 2

1 второй вход первой группы входов по

3 ) ЗП > 17

Недостатком этого 0-триггера нв»я-. ется его относительно большая слок4

И ко горого соедивец с выходом элемента 11-НЕ 5.

D-триггер работает следующим образом.

Предполо>хим, что перед подачей тактового импульса на входе 6 присутствует низкий логический сигнал, Это вызовет высокий логический потелциал на выходе входного логического элемента 5. Допустим, что на выходе элемента И-ИЛИ-НЕ присутствует единичный (высокий) логический сигнал . Тогда ца выходе инвертора 3 оказывается низкий логический сиг-нал, подтверждающий высокий логический выходной сигнал на элементе

И-ИЛИ-НЕ !. В этом случае на обоих входах элемента И-ИЛИ-HE 2 оказываются единичные логические сигналы и на выходе этого элемента формируется низкий логический уровень, вызывающий появление высокого логическо— го сигнала на выходе инвертора 4.

Пусть в момент t начинается положительный тактовый импульс. При этом на обоих входах элемента И-ИЛИ1IE оказываются высокие логические сигналы. Вследствие этого на его выходе формируется низкий логический сигнал, а потом — высокий логический сигнал на выходе инвертора 3.

Поскольку на входе 6 присутствует нулевой логический сигнал, а на входах элемента И-ИЛИ-НЕ 2 присутствуют оба высоких логических сигнала, других изменений потенциалов на составных частях 0-триггера в момент йл, не происходит.

По окончании тактового импульса и на входах элемента И-ИЛИ-НЕ 2 ока2. зывается низкий логический сигнал. В резульгате этого на выходе элемента

И-ИЛИ-НЕ 2 формируется единичный логический сигнал, после чего на выходе инвертора 4 появляется низкий логический сигнал. Поскольку на входе

6 присутствует нулевой логический потенциал, а на входах элемента И-ИЛИНЕ 1 оба единичных логических сигнала, других изменений потенциалов на составных частях 0-триггера в момент не происходит.

Если к моменту t начала следу>>щего тактового импульса логический сигнал на входе 6 останется нулевым, то тактовый импульс не Mo>zeT изменить выходные сигналы составных частей

D-триггера. Действительно, высокий логический сигнал на выходе входно5 930 го логического элемента 5 поддер>ави†вается низким логическим сигналом на входе 6; низкий логический сигнал на выходе элемента И-ИЛИ-НЕ 1 поддеряивается высокими логическими сигнала» 5 ми на двух входах — с выхода входного логического элемента 5 и с выхода инвертора 3, высокий логический сигнал на выходе инвертора 3 поддерживается низким сигналом на его вхо- !О де — с выхода элемента И-ИЛ!1-НЕ 1;

) высокий логический сигнал на выходе элемента И-ИЛИ-НЕ 2 поддерживается вследствие того, что на одном иэ входов присутствует нулевой логический 15 сигнал — с выхода элемента И-ИЛИ-НЕ 2 и с выхода инвертора 4. Низкий логический сигнал на выходе инвертора 4 поддерживается высоким логическим потенциалом на его входе — с выхода щ элемента И-ИЛИ-НЕ 2.

Предпопох<им, что после окончания тактового импульса t логический сигнал на входе 6 изменяется с нулевого на единичный. Тогда при поступлении И следующего тактового импульса t на обоих входах входного логического элемента 5 оказываются высокие логические уровни, и его выходной логический сигнал становится нулевым. После это- щ го на одном из входов элемента И-ИЛИНЕ 1 появляется нулевой логический сигнал, а на его выходе формируется единичный логический сигнал, который устанавливается на выходе инвертора

33

3 низкий логический сигнал. Поскольку на обоих входах элемента И-ИЛ11НЕ 2 присутствуют высокие логические сигналы, других изменений потенциалов на составныхчастях D"триггера с задери40 кой в момент 5 не происходит.

По окончании тактового импульса на выходе логического элемента 5 формируется высокий логический сигнал.

После этого на обоих входах элемента

И-ИЛИ-НЕ 2 оказываются высокие логические сигналы. Таким образом, на вы-. ходе этого элемента формируется низкий сигнал, который устанавливает высокий логический сигнал на выходе

S0 инвертора 4. Поскольку на одном из входов элемента И-ИЛИ-НЕ 1 присутствует низкий логический сигнал, других изменений.потенциалов на составных частях 0-триггера не происходит, Если к моменту 1 начала следуИ

7 юцего тактового импульса логический сигнал на в::оде 6 останется единичным, то на обоих входах входного ло59 7 6 гического элемента 5 и элемента

И-И11И-HL 1 оказываются единичные логические сигналы. Вследствие этого на выходе элемента И-ИЛИ-НЕ 1 и на выходе логического элемента 5 формируются низкие логические сигналы.

Низкий логический сигнал с выхода элемента И-ИЛИ-HE формирует высокий сигнал на выходе инвертора 3, Поскольку на элементе И-ИЛИ-НЕ 2 присутствуют два высоких логических сигнала (с выхода инвертора 4 и тактовый импульс) в момент 1. сигналы на выходах измениться не могут.

Однако, по окончании формирования низкого логического сигнала на выходе входного логического элемента 5 на одном из входов элемента И-ИЛИ-НЕ 1 оказывается низкий логический сигнал.

Таким образом, на выходе Ътого элемента вновь формируются высокие логические сигналы. Высокий логический сигнал с выхода элемента И-ИЛИ-НЕ 2 устанавливает низкий логический сиг" нал на выходе инвертора 4. Поскольку на одном из входов элемента И-ИЛИНЕ 1 в момент t> присутствуют низкие логические сигналы {с выхода инвертора 3 и со входа тактовых импульсов

7), в момент t сигнапы на триггере не меняются .

После формирования высокого логического сигнала на выходе логического элемента 5, на входах элемента

И-ИЛИ-НЕ 2 оказываются высокие логические сигналы. Это вызывает появление на ее выходе низкого логического сигнала, который формирует высокий логический сигнал на выходе инвертора 4, т.е. на выходах триггера образуется кратковременный выброс.

Таким образом, все режимы работы

0-триггера при приеме информации по входу 0 полностью рассмотрены: если в момент прихода следующего тактового импульса на входе 0 сохранится высокий логический сигнал, то работа 0-триггера будет повторять его функционирование в момент t7, если же сигнал изменится на нулевой, то работа 0-триггера будет повторять его функционирование в момент

Таким образом, D-триггер обеспечивает нормальное функционирование при использовании более простых элементов, что позволяет сократить затраты оборудования на его реаппэациюв

93059

Формула изобретения

ВНИИПИ Заказ 3494/79 Тираж 954 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

D-триггер, содержащий первый и второй элементы И-ИЛИ-НЕ, первый и второй инверторы и элемент И-НЕ, пер- 5 вый и второй входы которого соединены соответственно cD-входом и тактовым входом О-триггера, выход элемента И-НЕ соединен с первыми входами первой и второй групп входов по

И первого элемента И-ИЛИ-НЕ, выход которого соединен с первым входом первой группы входов по И второго элемента И-ИЛИ-НЕ и входом первого инвертора, выход которого соединен со вторым входом первой группы входов по И первого элемента И-ИЛИ-НЕ, второй вход второй группы входов по

И первого элемента И-ИЛИ-НЕ соединен

7 8 с тактовым входом 1.1-триггера и пер- вым вхоДом второй группы входов по

И второго элемента 1-ИЛИ-НЕ, второй вход второй группы входов по И которого соединен с выходом второго инвертора, о т л и ч а в шийся тем, что, с целью упрощения, вход второго инвертора соединен с выходом второго элемента И-ИЛИ-НЕ, второй вход первой группы входов по И которого соединен с выходом элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н. и др. Иикроэлектронные схемы цифровых устройств, M. "Советское радио", 1973, с. 87.

2. Авторское свидетельство СССР

1"- 396332, кл. Н 03 1(21/00, 1969 (прототип).