Синхронный демодулятор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 930644 (61) Дополнительное к авт. санд-ву(22) Заявлено 13. 06. 79 (21) 2778563/18-21 с присоединением заявки М (23) Приоритет

Опубликовано 23.05 82. Бюллетень Юг19

Дата опубликования описания 23 ° 05.82 (5 I ) M. КМ.

Н 03 K 9/02

Гасударственный квмктет

СССР ао делам кзебретеннй

II втерыткй (53) УДК 621. 374.,. 3(088.8) p е.

В. М, Бреннерман и В. В. Шевчук

1 (72) А вторы изобретения (71) Заявитель (54} СИНХРОННЫЙ ДЕМОДУЛЯТОР

Изобретение относится к импульс: ной технике и может быть испольэовано для демодуляции импульсных сигналов, промодулированных по амплитуде.

Известен синхронный детектор с управляемым устройством запоминания 11 ).

Недостаток этого детектора заключается в низкой помехоустойчивости из-за наличия аддитивной помего хи, которал подавляется лишь частично.

Известен также синхронный демодулятор, содержащий блок масштабного IS суммирования, блок выборки - запоминания, состоящий из и ключевых элементов и и конденсаторов, первые выводы которых подключены ко входам блока масштабного суммирования и блок упоавления (2).

Недостатком известного пемодулятора является низкая помехоустойчивость при большом уровне помел;

Оель изобретения - повышение помехоустойчивости.

Поставленная цель достигается тем, что в синхронном демодуляторе с и выборками входного сигнала, содержащем блок масштабного суммирования, выход которого подключен к выходной шине, а входы - к выходам блока выборки- запоминания, состоящего из ключевых элементов и кон- . денсаторсгв, первые выводы которЫ подключены к выходам блока выборкиэапомининия, и блок управления, блок выборки - запоминания состоит иэ (n-1) синхронных детекторов, в которых ключевые элементы подключены между общей шиной и выходами блока выборки- запоминания, вторые выводы конденсаторов объединены и

Ф подключены к входной шине, а выходы блока управления подключены к управляющим входам. ключевых элементов:

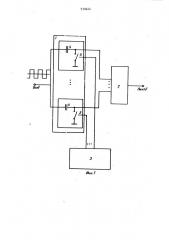

На фиг, 1 показана функциональная схема синхронного модулятора;

3 93064 на фиг. 2 - диаграммы входного, выходного и управляющих сигналов.

Синхронный демодулятор с и выборками входного сигнала содержит блок

1 выборки — запоминания, блок 2 масштабного суммирования и блок 3 управления. Блок 1 выборки - запоминания выполнен в виде (n-1) синхронных детекторов, каждый из которых состоит из конденсатора 4 и ключевого

1О элемента 5. Первые выводы конденсаторов подключены к соответствующим входам" блока 2 масштабного суммирования, а вторые выводы обьединены и подключены к входной -шине. Ключевые элементы 5 включены между первыми выводами конденсаторов 4 и общей шиной, а управляющие входы ключевых элементов соединены с соответствующими

»выходами блока 3 управления.

Синхронный демодулятор работает следующим образом.

На вход синхронного ремодулятора поступают сигналы знакочередующихся п(рямаугольных импульсов с аддаптивной помехой (на фиг. 2) о(»(«(-»l A +» (»() где i - номера положительных и отрицательных импульсов;

А - полезный сигнал; {й.) - значения помехи, соответствующие моментам

- моменты выборок сигнала в

1 синхронных детекторах 1. зз

Если синхронный демодулятор содержит и синхронных детекторов, то для получения одного значения полезного сигнала используется последовательность из (и+1) импульсов. Положительная полярность управляющих сигналов U U „(ôèã. 2) соответствует открытому состоянию ключевых элементов 5. Когда ключевой элемент 5 открыт, конденсатор 4 включен 4з между общей шиной и входом устройства и происходит заряд конденсатора до величины входного сигнала. По отрицательным фронтам управляющих сигналов происходит запоминание на конденсаторах ", соответствующих этому моменту времени значений входного сигнала. Входное сопротивление блока

2 масштабного суммирования должно быть достаточно велико, чтобы исключить погрешности разряда конденсаторов 4. На конденсаторе 1-ro синхронного детектора оказывается запомнен4 4 ным значение 0(t,), причем на вход блока 2 масштабного суммирования после размыкания ключевого элемента 5 оно включается с обратным знаком. В момент времени п „ на внходах синхронных детекторов появляется напряжение величиной 0(й„ „)- 0(t;)

Выходные сигналы синхронных детекторов суммируются в блоке 2 масштабного суммирования с весовыми коэф1-1 фициентами (11 " (1п

Поэтому в момент времени t на

llw1 выходе устройства имеем

1-1

u»,„=Z,I-1) " (u(Ä;,)-Щ „))=

i""-1 . С1-"

„М,) v())=

Ь1

)-1

=Г (-»("„1((- (A If(»»)J-(И A f(»nиl))= У „"+ — 1 (-1)iC1 "„1 f(< )

«=1 Е Ч

1+1 1» П+1 С1 1

„)1И1((-1)1 " - f(t Рi (-, 11 — 11

П П, 1 П

+1 Pi+1 (А . C, "

Q — „=1;2 (-1) „-0

C (- ) С„ („)=ь" „,..., „„), 1-1 где 6" - конечная разность и-го порядка.

Следовательно

ЬУ (t1, - ) н Д, » "2

ЪЬ(х 2"

Коэффициент подавления помехи и и 7 2

hhnf- „,..., „)

Для ()= S1n Hif e»ти

-д" (,...g )=f P (-1) C„Sihk3(E <„-=

Ф 1=1

Л» ь»-Х в "1 (s(nnf A»)»»п Gi»«tin )

Наибольшая величина h ЩД (1» -А))= fh15ih Jl E(5t.

5 930644

Тогда наименьшее значение подавления б

Формула изобретения

2. Авторское свидетельство СССР

М 656164, кл. H 02 M ?/09, 05.04. 79

3s (прототип}.

-n

=(SinJif lItj = Мп — аЖ р

Для низкочастотной помехи к . -„(п оп 3

При =50 Гц и f 5 кГ4 коэффициент подавления равен 4070, 260000, 16600000,..., соответственно для п=2,3,4,....

Таким образом достигается значительное уменьшение помех.

Управляющие сигналы могут быть и другими : отпирая ключевые элементы лишь на один такт, соответствующий запоминаемому значению входного сигнала. Однако при сигналах 1, В выходное напряжение демодулятора имеет удобную форму, в виде монотонно нарас" тающего сигнала U (фиг. 2) до знаВЬ!х чения А.

Блок масштабного суммирования может быть выполнен на основе известных схем с применением суммирующих операционных усилителей.

Предлагаемое изобретение обеспечивает исключение постоянной и значительное уменьшение переменной сос-. тавляющей помехи; при частоте модупя ции 5 кГц помеха частотой 59 Гц уменьшается больше, чем в 63,3 раза при п=2, в 4070. раз при п=3, в 260000. раз при п=4 и т.д.

Синхронный демодулятор с и выборками входного сигнала, содержащий блок масштабного суммирования, выход которого подключен к выходной шине, а входы - к выходам блока выборки запоминания», состоящего из ключевых элементов и конденсаторов, первые выводы которых подключены к выходам блока выборки - запоминания, и блок управления, о т л и ч а ю щ и и с. я тем, что, с целью повышения помехоустойчивости, блок выборки-запоминв- ния состоит из и-1 синхронных детекторов, в которых ключевые элементы под ключены между общей шиной и выходами блока выборки - запоминания, вторые выводы конденсаторов объединены и подключены к входной шине, а выходы блока управления подключены к управляющим входам ключевых элементов.

Источники информации, принятые во внимание при экспертизе

1. Дж. Грен, Дж. Тоби и Л. Хьюлсман, проектирование и применение операционных усилителей. M., "Мир", 1974, с, 382-389, фиг. 9.29.