Интегрирующий время-импульсный преобразователь

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ к лвтоескомь свидетельств

Союз Советскик

Соцкалкстнческна

Республик (и) 930659 (Sl ) Дояолннтельное к авт. санд-ву (22) Занвлено 24. 06. 76(21) 2375328/! 8-21 (53)M. Кл. с нрнсоеинненнем заявкн М

H 03 1(13/20

9еудерстиев6 кеметет

СССР ае делам взебретеекй н епеытяй (23)ПркорнтетОпублнковано 23. 05.82. Бюллетень М19 е

Дата ояублнковання оннсання 23.05.82 (53) УДК 681. 325. (088.8)

В. Д. Иихотин, С. В. Ткачев, С. 6. Шах

Э, К. Шахов и В. И. Шляндин

С (72) Авторы нзобретення пензенский политехнический институт (71} Заявитель (54) ИНТЕГРИРУ10фйй ВРЕНЯ-NHAYBbCHbN

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к цифробой электроизмерительной технике и может быть использовано в цифровых приборах специального и универсального назначения для измерения напря- жения постоянного тока, средневыпрямленного значения напряжения переменного тока, векторных составляющих переменного напряжения.

Известен аналого-цифровой. преобразователь, содержащий интегратор, первый вход которого соединен с источником преобразуемого напряжения, а выход подключен к входу блока сравФ 3$ нения, второй вход которого соединен с генератором циклов, а выход подключен к управляющему входу переключателя, через который соединя=, ется выход биполярного источника образцового напряжения с вторым вхо" дом интегратора

Недостатком известного устройства является иевоэможность изменения в аироких пределах длительности цикла преобразования.

Известен цифровой интегрирующий вольтметр, содержащий интегратор, выход которого соединен с первым входом блока сравнения, источник калиброванного напряжения, выходы которого соединены с входами переключатеч ля; первый. вход дополнительного интегратора подсоединен к выходу источника калиброванного напряжения и через ключ к. выходу дополнительного бяока,сравнения, входы сумматоров соединенй с выходом дополнительного интегратора и с выходом генератора тактовых импульсов, выход сумматора соединен с вторым входом блока сравнения,- первый вход дополнительного блока сравнения соединен с вы-, ходом дополнительного интегратора, а второй вход - с виной источника. порогового напряжения, раздельные входы триггера соединены с выходом генератбра тактовых импульсов и с

93065

3 выходом блока сравнения, выход триггера соединен с управляющим входом ключа„ а второй вход интегратора

I соединен с вторым входом дополнительного интегратора 21.

Недостатком данного устройства являются ограниченные функциональные возможности, Цель изобретения - расширение функциональных возможностей. 30

Поставленная цель достигается тем, что в интегрирующий время-импульсный преобразователь, содержащий два блока сравнения, два интегратора, первые входы которых объединены, -второй вход первого интегратора соединен с выходом переключателя, входы которого соединены с двумя выходами биполярного источника образцового напряжения, первый выход которого соединен с вторым входом второго интегра тора, выход которого соединен с первым входом первого блока сравнения, второй. вход которого соединен с выходом первого интегратора, выход генератора циклов соединен с первым входом триггера, второй вход которого соединен с выходом первого блока сравнения, а выход соединен с входом "Сброс" второго интегратора, ЗВ введены элементы ИЛИ и дополнительный триггер, причем вход второго блока сравнения соединен с выходом первого интегратора, а выход - с первым входом элемента ИЛИ, второй вход ээ которого соединен с выходом генератора циклов, а выход - с первым вхо» дом дополнительного триггера, выход которого соединен с управляю-» щим входом переключателя, а второй щ вход соединен с выходом nepsoro блока сравнения . ,!

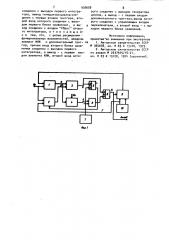

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - диаграммы, поясняющие его работу.

Устройство содержит интеграторы 1 и 2, блоки 3 и 4 сравнения, триггер

5, элемент ИЛИ 6, генератор 7 циклов, триггер 8, переключатель 9, биполярный источник 10 образцового на-. пряжения. На фиг. 2 обозначено: напряжение 11 на выходе интегратора 1; напряжение 12 на выходе интегратора 2; напряжение 13 на выходе генера- >> тора 7; напряжение 14 на выходе блока 3; напряжение 15 на выходе блока 4; напряжение 16 на выходе тригУ

9 4 гера 5; напряжение 17 на выходе триггера 8. В процессе работы устройства выходное напряжение интегратора 1 то убывает, то возрастает в зависимости от знака образцового напряжения

Но. Изменение направления интегрирования осуществляется в момент срабатывания одного из блоков сравнения.

Рассмотрим сначала процесс, происходящий в частном цикле преобразования Т„- Т1„+ T<„, находящимся внутри полного цикла преобразования Т

Иэ фиг. 2 видно, что приращение интеграла на выходе интегратора 1 за время Т.!и равно его приращению за время Т „и равно 0 Следовательно, будет выполняться соотношение Т я Ъ.,4т1 + I Тф )

Д щ и;"1 (v„-.,y =p,

В Ф1Фт1в иэ которого следует

О %я

О Я -Т )

J r+ у я

Из выражений {1) и l2) видно что среднее значение 0„ на интервале Т, пропорционально разности Т, -Т

Qn 1n

Кроме того, длительность частного цикла Т„ зависит от величины О„.

Поэтому для noworo цикла преобразования сумма приращений напряжения иа выходе интегратора при-интегрировании Ох + Uo и сумма приращений при интегрировании Ох- Оо в общем случае ие будут равны нулю, как зто происходит в частном цикле преобразования. В данном случае при равенстве постоянных времени интеграторов

1 и 2 выполняется равенство, о 4, « 1 { 4 Ом" f-1ст.-ст !-U- (3) и 1 в

О где 0„- напряжение на интеграторе

1 в начале цикла преобразования;

U<- йапряжение на, интеграторе

1 в конце цикла преобразования;

QT - сумма интервалов времени, е течение которых осуществляется интегрирование разности {U>- U<);

ЕТ„„- сумма интервалов времени, в течение которых осуществляется интегрирование суммы

{u„+ оо). откуда получаем

5 93065

KBK следует из (3) при произвольном цикле преобразования разность интегралов от преобразуемого U и образцового 0п напряжений эа время цикла Т отлична от нуля и равна

U<- 0<, причем эта величина случайна и может принимать значение от 0 доЩо . Из-за неравенства нулю раз" ности 0„- 0И возникает погрешность, абсолютное значение которой в маса- 10, табе выходной величины преобразователя определяется выражением

ChT -a -ьт = ---".- — -- L. (ll)

Ок UH к н- U U о О 15

Следовательно, для ее исключения в результат преобразования необходимо ввести попоавку )d"tl со знаком, противоположным знаку O T. Для этого в устройстве, в начале и в конце каждого цикла преобразования проис.ходит срабатывание триггера 5, который разрешает интегрирование входных напряжений интегратора 2, в результате чего срабатывание блока 3 ээ происходит не в момент равенства нулю выходного напряжения интегратоba 1, как это осуществляется внутри цикла преобразования, а несколько раньше через интервал времени ЬТ11.< ко- 30 ч

11Щ з ,:торыи может быть определен из вйражения Тн<ц > a(a} с й0ц q "< e) ) Ф р) ® 3

О 6 ьт = --S ° r„° (б)

0н к

Щк) 200

Из сравнения выражений (4) и 40

{6) следует, что для ввода поправки необходимо удвоить значения аТ1К ° н(к)

При этом функция преобразования принимает вид

5. и и ВТ „%6ТИ11аТ = —" Т (7)

К Q Ц ) ° где 0к- среднее значение входного напряжения за цикл преобразования. 30

Из выражения (7) видно, что для преобразования интегрального (среднего) значения входного напряжения в код при помощи предлагаемого преобразователя необходимо применять реверсивный счетчик импульсов, причем в течение интервалов времени ЭТ пи dT11 счетчик должен заполняться на "Сложение", 9 6 а в течение интервалов 3Т1 и ьТ на

1п К вычитание.

Предлагаемое устройство можно ис-. пользовать в качестве базового блока при конструировании различных приборов — вольтметров постоянного напряжения, измерителей средневыпрямленного значения напряжения, фазочувст,вительных вольтметров для измерения ортогональным составляющих гармонических колебаний. Для измерения средневыпрямленного значения напряжения достаточно выбрать цикл преобразования равным и совпадающим с полупериодом входного напряжения. При этом,,например, в положительный полупериод ре= зультат заносится в реверсивный счетчик со. знаком "+", а в отрицательный -, с знаком минус. Для получения результата интегрирования с противоположным. знаком необходимо поменять порядок заполнения реверсивного счетчика на обратный. Аналогично осуществляется фазочувствительное детектирование с той лищь разницей, что циклы преобразования задаются от внешнего генератора синхроимпульсов. Операция фазочуаствительного (синхронного) детектирования будет осуществляться в цифровом виде и поэтому высокоточно, 4Т0 позволяет расширить области применения устройства.

Положительный эффект достигается эа. счет того, что цикл интегрирования может варьироваться в широких пределах. Повышение точности достигается sa счет того, что основной интегратор 1 работает в ограниченном (величиной Ов) динамическом диапазоне,.что позволяет повысить линейность преобразования. К .стабильности U> не предъявляется жестких требований.

Формула изобретения

Интегрирующий время-импульсный преобразователь, содержащий два бло-.. ка сравнения, два интегратора, первые входы которого объединены, второй вход первого интегратора соединен с выходом переключателя, входы которого соединены с двумя выхода ми биполярного источника образцового напряжения, первый выход которого соединен с вторым входом второго интегратрра„ выход которого соединен с первым входом первого блока сравнения, второй .вход которого

7 930659 8 соединен с выходом первого интегра-, рого соединен с выходом генератора тора, выход генератора циклов сое- циклов, а выход - с первым входом динен с первым входом триггера, вто- дополнительного триггера, выход которой вход которого соединен с выхо- рого соединен с управляющим входом дом первого блока сравнения, а вы- переключателя, а второй вход - с выход соединен с входом "Сброс" второ- ходом первого блока сравнения. го интегратора, о т л и ч а ю щ и йс я тем, что, с целью расширения Источники информации, функциональных возможностей, введены принятые во внимание при экспертизе элемент ИЛИ и дополнительный триг- 1в 1.,Авторское свидетельство СССР гер, причем вход второго блока срав- У 365038, кл. Н 03 K 13/20 1973 нения соединен с выходом nepsoro 2. Авторское свидетельство СССР интегратора, а выход - с первым вхо- по заявке в. 2037545/,18-21, дом элемента ИЛИ, второй вход кото- кл. Н 03 К 13/20, 19711 (прототип).

930659

Составитель D. Титов

Редактор M. Данканич Техред И. Надь Корректор И. Иуска

--б

Заказ 3527/82 Тираж 954 подписное

ВНИИХИ Государственного комитета СССР по делам изобретений и открытий

:113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал lW патент"; г. Ужгород, ул. Проектная, 4