Устройство дельта-модуляции с цифровой адаптацией

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (930664

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИЯЕТЕПЬСТВУ

Союз Советскик

Социалистических

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 24. 09. 80 (21) 2986438/18-у1 с присоединением заявки М (23) Приоритет(51)M. Кл.

Н 03 K 13/22 Вкудврствснный квкнтвт

СССР пв делам нзебретеннй и открытий (53) Уд< 621. 3Ó6. .9(088.8) Опубликовано 23. 05. 82, Бюллетень Эй 19

Дата опубликования описания 23 05 82

1 (72) Авторы изобретения

В.В.Кузнецов и И.S.Ñèòíëêîâñêèé! !

Новосибирский электротехнический институт связи (71) Заявитель (54) УСТРОЙСТВО ДЕЛЬТА-МОДУЛЯЦИИ С ЦИФРОВОЙ

АДАПТАЦИЕЙ блока PJ.

Изобретение относится к области электросвязи и может быть использовано при разработке цифровых передатчиков сигналов.

Известно устройство, содержащее дельта-модулятор, адаптивную логику, счетчик, делитель частоты, два генератора импульсов (1) .

Недостатком известного устройства является его сложность.

Известно устройство, содержащее высокочастотный дельта-модулятор, сигнальный вход которого соединен с шиной входно1.о сигнала, первый генератор тактовых импульсов и второй генератор тактовых импульсов, выход которого соединен.с счетным входом триггера, первый выход которого соединен с входом логического

Недостатком этого устройства является его сложность и, следовательно, его низкая надежность.

Цель изобретения — повышение надежности.

Поставленная цель достигается тем, что в устройство дельта-модуляции, содержащее высокочастотный дельта-модулятор, сигнальный вход которога соединен с шиной входного сигнала, первый генератор тактовых импуль-. сов и второй генератор тактовых импульсов, выход которого соединен с е счетным входом триггера, первый выход которого соединен с входом логического блока, введены делитель частоты импульсов, реверсивный счетчик

1j и два элемента И, причем выходы высокочастотного дельта-модулятора соединены с первыми входами элементов

И, вторые входы которых соединены с соответствующими выходами триггера, информаци чнный вход которого соединен с выходом реверсивного счетчика, входы которого соединены с выходами соответствующих элементов И, выход логического блока соединен с уп 930664 ра вляющим входом управляемого делителя, вход которого соединен с выходом первого интегратора импульсов, а выход — с синхронизирующим входом высокочастотного дельта-модулятора.

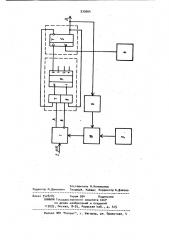

На чертеже представлены блок-схема устпойства дельта-модуляции с цифровой адаптацией.

Устройство содержит высокочастотный10 дельта-модулятор (ВДИ) 1, сигнальный вход которого соединен с шиной 2 вход-, ного сигнала, генератор 3 тактовых импульсов и генератор 4 тактовых им. пульсов, выход которого соединен 1 с счетным входом триггера 5, первый . выход которого соединен с входом логического блока 6, выходы модулятора соединены с первыми входами элементов I): 7 и 8, вторые входы которых со- 2о единены с соответствующими выходами триггера 5, информационный вход которого соединен с выходом реверсивного счетчика 9, входы ,которого соединены с соответ- 25 ствующими выходами элементов И 7 и 8, выход блока 6 соединен с соответствующими выходами элементов

И 7 и 8, выход блока 6 соединен с управляющим входом управляемого делителя 10, вход которого соединен с выходом генератора 3, а выходс синхронизирующим входом модулятора 1.

Устройство дельта-модулятора с цифровой адаптацией работает следующим образом.

Входной аналоговый сигнал f(t), поступающий на шину 2 подается на дельта-модулятор 1, работающий на высокой тактовой частоте, что обеспечивает высокое качество аналог-дельта преобразования. На выходе ВДМ 1 имеются две цифровые последовательности, представляющие собой прямой и инверсный дельта-сигналы, которые поступают через элементы 7 и 8 соответственно, на входы реверсивного счетчика 9. Причем, если последний разряд, подключенный к тактируемому

50 триггеру 5, в момент тактирования находится в положении "1" - открывается элемент 8 и в счетчике 9 сумми" руются импульсы, в другом случае открывается элемент 7 и счетчик 9 вычитает импульсы. Тактирование триггера 5 осуществляется на частоте

Fc,от низкочастотного генератора 4.

Блок 6 логики управляет в зависимости от сигнала на выходе триггера 5 коэффициентом деления делителя 10, что позволяет производить цифровое компандирование.

Таким образом, предлагаемое устройство сохраняя яараметры извест-! ного, значительно проще его.

Формула изобретения

Устройство дельта-модуляции с цифровой адаптацией, содержащее высокочастотный дельта-модулятор, сигнальный вход которого соединен с шиной входного сигнала, первый генератор тактовых импульсов и второй генератор тактовых импульсов, выход которого соединен с счетным входом триггера, первый выход которого соединен с входом логического блока. о т л.и ч а ю щ е е с я тем, что,с целью повышения надежности, в него введены делитель частоты импульсов, реверсивный счетчик и два элемента И, причем выходы высокочастотного дельта-модулятора соединены с первыми входами элементов

И, вторые входы которых соединены с соответствующими выходами триггера, информационный вход которого соединен с выходом реверсивного счетчика, входы которого соединены с выходами соответствующих элементов И, выход логического блока соединен с управляющим входом управляемого делителя, вход которого соединен с выходом первого генератора импульсов, а выходс синхронизирующим входом высокочастотного дельта-модулятора.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3699566, кл.Н 03 К 13/22, 1072.

2. Патент США 11 3652957, кл. Н 03 К 13/22, 1972.

930664

Составитель H.Êîíîâàëîâ

Редактор M.Äàíêàíè÷ Техред И. Рейвес Корректор А.Дзятко

I Ф

»

Заказ 3528/83 Тираж 954 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва, N-35, Раушская наб, д. 4/5

»» °

Филиал ППП "Патент" ° г. Ужгород, ул. Проектная, 4