Асинхронная коммутационная система

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистические республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к эвт. свид-ву (22) Заявлено 19, 11.80 (21) 3007602/18-21 с присоединением заявки М (23) Приоритет

Опубликовано 23.05.82. Бюллетень ¹ 19 (5 l ) M. Кл.

Н 03 К 17/00

1Ъаударсткнный комитет

Ссср ае делам изобретений в открытки (53 ) УД К 68 1.32 (088.8) Дата опубликования описания 25.05.82 (72) Автор изобретения

В. А. Авдеев (7 I ) Заявитель

Таганрогский радиотехнический институт и (54) АСИНХРОННАЯ КОММУТАЦИОННАЯ СИСТЕМА

Изобретение относится к автоматике и коммутационной технике.

Известны асинхронные коммутационные системы, содержащие блоки дешифрации, уплотнения, логических эпементов, памяти и управления (1 .

Наибопее близким к изобретению является асинхронная коммутационная система, содержащая блок дешифрации, блок уплотнения, информационные входы кото о рого соединены с первой группой информационных входных шин, а выходы подключены к информационным входам блока логических эпементов, выходы которого соединены с выходными шинами, блок памяти, 15 информационные входы которого подключены к второй группе информационных входных шин, а управляющие входы соединены с управляющими входами блока уппотнения и блока логических элементов и управ20 пяющими выходами блока управления(2).

Недостаток известных устройствнизкое быстродействие.

Ilem изобретения — повышение быстродействия асинхронной коммутационной системы.

Поставленная цель достигается тем, что в асинхронной коммутационной системе, содержащей бпок дешифрации, блок уплотнения, информационные входы которого соединены с первой группой информационных входных шин, а выходы подкпючены к информационным входам блока логических элементов, выходы которого соединены с выходными шинами, блок памяти, информационные входы которого подкпючены к второй группе информационных входных шин, а управляющие входы соединены с управляющими входами блока уплотнения и блока логических элементов и управляющими выходами блока управпения, введены бпок формирования адреса и блок приоритета, входы которого соединены с управляющими входными шинами, а выходы подкпючейы к адресным входам блока уплотнения и блока формирования

1адреса, информационные входы которого

3 9306 соединены с третьей группой информационных входных шин,t управляющие входы —. с выходами блока управления, а выходы— с адресными входами блока памяти, группа выходных шин которого подключена через блок дешифрации к адресным входам бпока логических эпементов, а дополнитепьный выход соединен с входом блока управ пения.

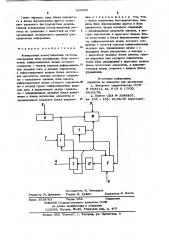

На чертеже представлена блок-схема и асинхронной коммутационной системы.

Устройство содержит бпок 1 уплотнения, информационные входы которого соединены с группой информационных, входных шин 2, а выходы подкпючены к информационным входам блока 3 логи.ческих эпементов, выходы которого соединены с выходными шинами 4, блок 5

Ф памяти, информационные входы которого подключены к группе информационных входных шин 6, а управляющие входы соединены с управпяющими входами блока

1 уплотнения и блока 3 погических элементов и управляющими выходами блока

7 управления, бпок 8 приоритета, входы которого соединены с управляющими входными шинами 9, а выходы подключены к адресным входам блока 1 уппотнения и блока 10 формирования адреса, информационные входы которого соединены с группой информационных входных шин 11, уцравпяющие входы — с выходами блоке 7 управления, а выходы — с адресными входами бпока 5 памяти, группа выходных шин которого подключена

Зэ через блок 12 дешифрации к адресным входам блоке 3 логических эпементов, а допопнитепьный выход соединен с входом блока 7 управпения.

Асинхронная коммутационная система работает следующим образом.

При вычислении неординарных соединений блок 10 формирования адреса содержит регистры, каждый из которых соответствует опредепенной шине из группы информационных входных шин 2 и предназначен для хранения начального адреса ячейки блока 5 памяти, начиная с которой в последующих ячейках блока 5 памяти записывается программа коммутации о выбранной информационной входной шины

2 с требуемыми выходнъ1ми шинами 4.

При вычислении ординарных соединений бпок 10 формирования адреса содержит фиксированные формирователи адреса и И не.имеет связей с группой информационных входных шин 11. Кроме того, отсутствует подключение допопнитепьного ин69 4 формационного выхода блока 5 памяти к входу блока 7 управления.

Перед началом работы в блок 5 памяти через группу информационных входных шин 6 вводится программа коммутации, каждое слово которой включает в себе адрес выходной шины 4- и выдепенный бит, принимающий значение логического нуля или единицы. Если выделенный бит равен нулю, то следующее спово относит1

4 ся к массиву спов, составляющему программу коммутации информационных входных шин из группы 2 с определенными выходными шинами 4. Наличие единицы в выделенном бите указывает на конец такого массива.

Кроме того, в регистры блока .10 формирования адреса записываются через группу информационных входных; шин 11 начальные адреса соответствующих массивов, распо пагаемых в бпоке 5 памяти. В бпок & приоритета по управляющим входным шинам 9 поступает сигнап вызов на передачу информации в приемники, подключенных информационными входами к выходным шинам 4 и выводами к информационным входным шинам группы 2.

Блок 8 приоритета при наличии свободного канапа между блоком 1 уплотнения ,и бпоком 3 погических элементов под;ключает соответствующую информацион нуюю входную шину группы 2 к этому каналу и производит считывание иэ соответствуюшего регистра блока 10 формирования адреса начального адреса, который в свою очередь выполняеТ считывание слова из ячейки блока 5 памяти.

Адрес выхода считанного слова декодируется в бпоке 12 дешифрации, сигнал с выхода которого подкпючает промежуточную пинию через блок 3 погических эпементов к .соответствующей выходной . шине 4. В наибопее простом варианте бпок 3 погических элементов состоит из элементов И, а блок 1 уплотнения представляет собой мупьтиплексор. Еспи выделенный разряд считанного спова иэ ячейки блока 5 памяти равен нулю, то сигналом блока 7 управления увеличивается на единицу адрес, храняшийся в регистре блока 10 формирования адреса, и осуществляется считывание слова из следующей ячейки блока 5 памяти. Этот процесс продолжается до тех пор пока ! считанное слово будет содержать в выделенном бите единицу, которая указывает на окончание цикла передачи информации.

930669

СостввитеЪь В. Чачанкцзе

Редактор М. -Данканнч Техред М. Рейвес Корректор М. Коста

Заказ 3528/83 Тираж 954 Подци снов

ВНИИПИ Государственного комитета СССР по делам изобретений и открытнй

113035, Москва, Ж-35, Раушская нвб„д. 4/S

Филиал ППП Патент, r. Ужгорсщ уп. Проектная, 4

Таким образом, ввод блока прноритета и блока формирования адреса позволяет увеличить быстродействие предлагаемой- асинхронной коммутационной системы по сравнению с известной зв счет 5 организации асинхронного принципа распределения информации.

Формула изобре те ния

Асинхронная коммутационная система, содержащая блок дешифрации, блок уплотнения, информационные входы которого соединены с первой группой,информацион- 1> ных входньис шин, в выходы подключены к информационным вхадам блока логических элементов, выходы которого соединены с выходными шинами, блок памяти, информационные входы которого псдключе-26 ны к второй группе информационных входных шин, а управляющие входы соединены с управляющими входами блока уплотнения и блока логических элементов н управляющими выходами блока управце« ния,отличающаяся тем,что, с целью повышения быстрадействня, введены блок формирования адреса и блок приоритета, входы которого соединены с управляющими .входными шинамя, а выходы подключены к адресным входам блока уплотнения и блока формирования адреса, информвцнонные входы которого сое-. динены с третьей группой информационных входных шин, управляющие входы - с выходами блока управления, а выходыс адресными входами блока памяти, груцпа выходных шин которого подключена через блок дешифрации к адресным входам блока логических элементов, а дополня тельный выход соединен с входом бпокв . управлении.

Источники ннформацня, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N. 593311, кп. Н 03 К 17/ОЬ, 04.03.78.

2. Патент США l4 3588837,,кл. 235 - 155, 15.03.79 (прототип).