Устройство для временного компандирования информации

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистические

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (8!)М. Кл . (22)3a влено 23 07.8 0 (21) 2962867/18-09 с присоединением заявки М (23) Приоритет

Н 04 J. 3/16!)

H 03 К 13/24

Ркудерстеснный квинтет

СССР пе делан наебретеннй н еткрытнй

Опубликовано 23. 05. 82. бюллетень hh 19

Дата опубликования описания 23. 05. 82 (53) УЛК. 621. 394. .676(088.8) А.А. Калинцев, Е.Ш. Прусс, О.С. Тихонов и В. /стюжайинг

1.: ",.;;.

С (72) Авторы изобретения

C . I (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО КОМПАНДИРОВАНИЯ

ИНФОРМАЦИИ

Изобретение относится к радиотехнике и может использоваться в спутниковых системах связи с многостанционным доступом и временным уплотнением (ИДВУ) сигналов земных станций (ЗС) в стволе ретранслятора.

Известно устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты, те блок перебора адресов записи, первый элемент И, элемент ИЛИ, блок памяти и первый регистр, управляющий вход которого объединен с управляющим вхо15 дом второго регистра, информационные входы которого соединены с соответствующими выходами блока памяти, информационные входы которого соеди— нены с соответствующими выходами

20 третьего регистра, последовательно соединенные второй делитель частоты, блок перебора адресов считывания и второй элемент И, выход которого соединен с вторым входом элемента

ИЛИ, и третий и четвертый элементы

И, первые входы которых являются входами сигнала огибающей 31).

Однако известное устройство имеет длительное время компандирования и сложно.

Цель изобретения — сокращение времени компандирования и упрощение устройства за счет уменьшения общего числа элементов.

Поставленная цель достигается тем, что в устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты, блок перебора адресов записи, первый элемент И, элемент ИЛИ, блок памяти и первый регистр, управляющий вход ко" торого объединен с управляющим входом второго регистра, информационные входы которого соединены с соответствующими выходами блока памяти, информа93071" ционные входы которого соединены с соответствующими выходами третьего регистра, последовательно соединенные второй делитель частоты, блок перебора адресов считывания и второй элемент И, выход которого соединен с вторым входом элемента ИЛИ, и третий и четвертый элементы И, первые входы которых являются входами сигнала огибающей, введены блок задерж- te ки и третий делитель частоты, при этом вход блока фазовой автоподстройки частоты соединен с выходом блока задержки, первый и второй входы которого являются входами соответствен- но сигнала огибающей и циклового сиг1 нала, первый и второй выходы пере атчика соединены соответственно с уп- завляющим и информационным входами третьего регистра, управляющий вход первого регистра соединен с выходом четвертого элемента И, второй вход которого, объединенный с первым входом второго делителя частоты является входом тактового сигнала, а первый и второй выходы второго делителя частоты соединены соответственно со входом третьего делителя частоты, и с вторым входом третьего. элемента И, выход которого соединен с вторым зо входом второго. элемента И и с входом считывания блока памяти, вход записи которого соединен с выходом третьего делителя частоты и с вторым входом первого элемента И, а вторые зз входы первого и второго делителеи частоты, блока перебора адресов записи и блока перебора адресов считывания являются входами сигнала сброса.

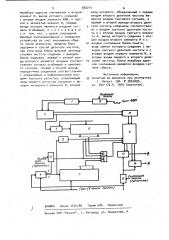

На чертеже дана структурная элект40 рическая схема предлагаемого устройства.

Ф

Устройство для временного компандирования информации содержит блок

1 фреевой автоподстройки 1оастотв, передатчик 2, первый 3, второй 4 и третий делители частоты блок 6 перебора адресов записи, блок 7 перебора адресов считывания, блок 8 памяти, первый 9, второй 10, третий 11 и четвертый 12 элементы,И, первый 13, 50 второй 14 и тре",ий 15 регистры, блок

16 задержки, э,фемент ИЛИ

Устройствг работает следующим об-, разом.

На вхог, олока 16 задержки поступа- ют импул. ы с цикловой частотой МДВУ, а на управляющий вход, поступает огибающая информационного текста. Причем изменение огибающей пакета приводит к изменению величины задержки

С выхода блока 16 задержки сигнал формы "меандр" поступает на блок 1.

I фаза этого сигнала совпадает с фазой цикла накопления.

Непрерывный цифровой поток, поступая в третий регистр 15 делится на слова, которые в параллельном виде подаются на входы блока 8 памяти.

Благодаря введению блока 16 задержки цикл накопления задержен относительно предыдущего цикла МДВУ, таким образом, что окончание цикла накопления совпадает по времени с окончанием информационного пакета, при этом требуется минимальный объем блоков памяти. Действительно, уменьшение требуемого объема блоков памяти до минимально. необходимой величины, равной числу бита в пакете, достигается исключительно за счет использования в качестве периода накопления (в компрессоре — это период записи, в экспандере — период. считывания) интервала времени между двумя соседними пакетами данной стадии и размещения (в компрессоре) интервала считывания в конце периода накопления так, что к началу следующего цикла накопления оказываются свободными все ячейки памяти и готовыми к записи новой информации.

Таким образом, использование предлагаемого устройства временного компандирования в каналообразующей аппаратуре системы спутниковой связи позволяет снизить долю блоков памяти в объеме названного оборудования.

Формула изобретения

Устройство для временного компандирования информации, содержащее последовательно соединенные блок фазовой автоподстройки частоты, передатчик, первый делитель частоты, блок перебора адресов записи, первый элемент И, элемент ИЛИ, блок памяти и первый регистр, управляющий вход которого объединен с управляющим входом второго регистра, информационные входы которого соединены с соответствующими выходами блока памяти, информационные входы которых соединены с соответствующими выходами третьего регистра, последовательно соединенные второй делитель частоты, блок

9307

15 го

РеиЮмЩЖ

ВНИИПИ Заказ 3534/85 Тираж b85 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

5 перебора адресов считывания и второи элемент И, выход которого соединен с вторым входом элемента ИЛИ, и третий и четвертый элемент И, первые входы которых являются входами сигнала огибающей, о т л и ч а ю щ е ес я тем, что, с целью сокращения времени компандирования и упрощения устройства за счет уменьшения общего числа элементов, введены блок задержки и третий делитель частоты, при этом вход блока фазовой автоподстройки частоты соединен с выходом блока задержки, первый и второй входы которого являются входами соответственно сигнала огибающей и циклового сигнала, первый и второй выходы передатчика соединены соответственно с управляющим и информационным входами третьего регистра, управляющий вход первого регистра соединен с выходом четвертого элемента И, второй

14 6 вход которого, объединенный с первым входом второго делителя частоты является входом тактового сигнала, а первый и второй выходы второго дели" теля частоты соединены соответственно с входом третьего делителя частоты и с вторым входом третьего элемента И, выход которого соединен с вто-! .рым входом второго элемента И и с входом считывания блока памяти, вход записи которого соединен с выходом третьего делителя частоты и с вторым входом первого элемента И, а вторые входы первого и второго делителей частоты, блока перебора адресов считывания являются входами сигнала сброса.

Источники информации, принятые so внимание при экспертизе

1. Патент США Н 3825899, кл. 340-172.5. 1974 (прототип).