Устройство регулирования избыточности в симплексных системах связи

Иллюстрации

Показать всеРеферат

И.И. Сушкевич, А.М. Савченко, Ф.Г. Киндиренко, Л.И. Ровнов и П.Л. Мартыненко

1 (72) Авторы изобретеиия (7! ) Заявитель (S4) УСТРОЙСТВО РЕГУЛИРОВАНИЯ ИЗБЫТОЧНОСТИ

В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ

Изобретение относится к технике передачи дискретной информации и может быть использовано. в автоматизи рованных системах управления при передаче информации по симплексным каналам связи.

Известно устройство регулирования избыточности в симплексных системах связи, содержащее последовательно соединенные блок памяти и блок запрета, а также последовательно соединенные блок сравнения, блок совпадения и счетчики, выходы которых объединены и подключены ко второму входу .блока запрета и входу блока памяти, ко второму входу кото .рого подключен выход блока запрета, при этом выход блока памяти подключен к другим входам блока совпадения (11.

Однако формирование известным устройством значения кратного повторения информации не учитывает условия приема информации каждым абонен том сети и определяется rio частоте приема информации всеми абонентами сети связи. В действительности же условия приема информации абонентами сети неодинаковы. Поэтому при

5 переходе от передачи информации або" ненту сети с хорошим качеством кана ла к передаче абоненту с плохим качеством канала при применении известно ного устройства имеет место неприем информации этим абонентом и дополнительная нагрузка сети связи повторной передачей информации, при переходе от передачи информации абоненту с плохим качеством канала к передаче информации абоненту с хорошим качеством канала информация передает" ся с большим числом повторений, что приводит к излишней занятости сети.

Цель изобретения — оптимальное регулирование числа повторений пере" дач.

Поставленная цель достигается тем, что устройство регулирования избы3 93072 точности в симплексных системах связи, содержащее последовательно соединенные блок памяти и блок запрета, а также последовательно соединенные блок сравнения, блок совпадения".и счетчики, выходы которых обьединены и подключены ко второму. входу блока

: запрета и входу блока памяти, ко вто рому входу которого подключен выход блока запрета, при этом выход бло- 16 ка памяти подключен, к другим входам блока совпадения, введены последова" тельно соединенные коммутатор сооб" щений, анализатор адресов и оперативный запоминающий блок, последова- 1$ тельно соединенные декодер информа" ции, счетчик блоков с ошибками, ана» лизатор состояния канала и формирователь квитанций, а также счетчик блоков и декодер квитанций, вход которого подключен ко второму выходу коммутатора сообщений, а выход через

-оперативный запоминающий блок подсое,динен ко входу блока сравнения, при этом третий выход коммутатора сообщений через последовательно соединен" ные декодер информации и счетчИк

- блоков подсоединен ко второму входу анализатора состояния канала, третий вход которого подключен к объединенным вторым входам формирователя квитанций, счетчика блоков с ошибками,,,счетчика блоков и третьему выходу декодера информации, четвертый выход которого подсоеДинен к третьему вхо" . 3$ ду формирователя квитанций, выход ко. торого подсоединен к третьему входу блока памяти, к четвертому входу ко" торого подключен четвертый выход коммутатора сообщений.

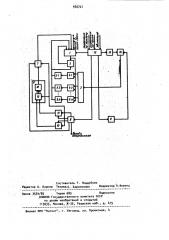

На чертеже дана структурно-электрическая схема устройства.

Устройство содержит блок памяти, блок 2 запрета, блок 3 сравнения, блоки совпадения 4.1-4.п,, счетчики 5. 1-5.п, анализатор 6 состояния

1$ канала, формирователь 7 квитанций, декодер 8 информации, декодер 9 квитанций, счетчик 10 .блоков, счетчик

11 блоков с ошибками, коммутатор 12 сообщений, анализатор 13 адресов, оперативный запоминающий блок 14,при этом анализатор состояния канала 6 содержит сумматор 15 и дешифратор 16. Сообщение, подлежащее передаче,содержащее адресную и информационную части, через коммутатор l2 сообщений записывается в блок 1, памяти. После этого информация начинает считываться в канал связи. Считывание информации ведется до появления на выходе блока 1 памяти сигнала "Конец информаций", которйй поступает на блок

2 запрета и блоки 4.сдвпадения. Одновременно с записью информации в блок

1 памяти адресная часть сообщения через коммутатор 12 сообщений поступает на анализатор 13 адресов, который производит считывание состояния ячейки оперативного запоминающего блока 14 о качестве канала связи по поступившему адресу в блок 3 сравнения. Блок 3 сравнения дешифрирует информацию о качестве канала связи в необходимое число повторений инфор" мационной части в. сообщении и выдает на одном из своих выходов сигнал, разрешающий прохождение сигнала

"Конец информации" через один из блоков совпадения 4 на подключенный к нему один из счетчиков 5.

Повторное считывание информации фэ блока 1 памяти производится по сигналу "Повторить передачу", который формируется из сигнала "Конец инфор" мации",, прошедшего через блок 2 эап" рета. Повторное считывание информации из блока 1 памяти ведется до тех пор, пока один из счетчиков 5 не просчитает выбранный обьем счета,т.е. выбранное число. повторений информационной части. В этом случае на выходе одного иэ счетчиков 5 появится сигнал, который запретит прохождение сигнала ".Конец информации " через блок 2 запрета и поступает на вход блока 1 памяти как сигнал "Конец передачи". После этого считывание информации в канал связи прекращает" ся.

Принятая иэ канала связи и демодулированная информация поступает на коммутатор 12 сообщений, который направляет ее на декодер 8 информации; линейного (n,М) кода. В начале приема информации декодер 8 информации обнуляет счетчик 10 блоков, счетчик блоков 11 с ошибками и устанавливает

s исходное состояние сумматор 15 анализатора 6 сщ;тояния канала и формирователя 7 квитанций..Декодер 8 информации декодирует информацию и выдает на.счетчик !1 блоков с ошибками.

Счетчик 10 блоков подсчитывает общее число блоков в декодируемой информации. По окончании декодирования счетчик .10 блОков будет содержать общее число блоков, а счетчик 11 бло930721

25

ЭО ков с ошибками .- число блоков с ошиб- ками в принятой информации, В результате работы сумматора 15 и дешифратора 16 анализатора состояния канала определяется отношение числа блоков с ошибками к общему числу принятых блоков, характеризующее состояние канала связи с тем абонентом,от которого принята Ййформация, поступившая на декодер 8 информации.

По окончании декодирования иэ декодера 8 информации в блок формирователь 7 квитанций поступает опоэнаватель, представляющий некоторую кодовую комбинацию. Поступление опоэнавателя в формирователь 7. квитанций разрешает считывать информацию с дешифратора 16 анализатора 6 состояния канала. В результате данных операций в формирователе 7 квитанций будет сформирована квитанция, несущая в себе информацию о качестве канала связи. Квитанция через блок 1 памяти поступает на выход.

Квитанция, принятая передающим . устройством, через коммутатор 12 сообщений поступает на декодер 9 квитанций, где производится ее декодирование, сравнение опознавателей и вы- . деление кодовой комбинации оценки состояния канала связи. Выделенная

1комбинация записывается в оперативный запоминающий блок 14 по адресу, указанному анализатором 13 адресов.

Техническая эффективность устройства по сравнению с известным заключается в увеличении пропускной способности симплексных каналов связи между абонентами сети.

Увеличение пропускной способности каналов связи при применении предлагаемого устройства происходит эа счет более рационального выбора числа повторений информационной части сообщения, учитывающего условия приема информации каждым абонентом сети. .Кроме этого, применение предлагаемого устройства позволит повысить эффективную скорость передачи vi.óìåíb шить время доставки информации в системе связи.

Формула изобретения

Устройство регулирования избыточности в симплексных системах связи, содержащее последовательно соединенные блок памяти и блок запрета, .а также последовательно соединенные блок сравнения, блок совпадения и счетчики, выходы которых объединены и подключены ко второму входу блока. запрета и входу блока памяти, ко второму входу. которого подключен выход блока запрета, при этом выход блока памяти подключен к другим входам блока сов15 .падения, о т л и ч а ю щ е е с я тем, что, с целью оптимального регулирования числа повторений передач, t введены последовательно соединенные коммутатор сообщений, анализатор адщ ресов, оперативный запоминающий блок; последовательно соединенные декодеринформации, счетчик блоков с ошибка-. ми, анализатор состояния канала и формирователь. квитанций, а также счетчик блоков и декодер квитанций, вход которого подключен .ко. второму выходу коммутатора сообщений, а выход через оперативный запоминающий блок подсоединен ко входу блока сравнения, при этом третий выход коммутатора сообщений через последовательно соединен- . ные декодер информации и счетчик блоков. подсоединен ко второму входу анализатора состояния канала, третий

Э5 вход которого подключен к объединенным BTopblM входам формирователя кви-. танций, счетчика блоков с ошибками, счетчика блоков и третьему выходу декодера информации, четвертый выход

40, которого подсоединен к третьему вхо ду формирователя квитанций, выход которого подсоединен к третьему входу блока памяти, к четвертому входу которого подключен четвертый выход коммутатора сообщений.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

4 507949,кл.Н 04 L 5/22, 1974 ;(прототип) .

930721 б

Составитель Т. Поддубняк

Редактор А. Кушнир Техред f. аритонцик Корректор"А.Ференц

Заказ 3534/85 Тираж 685,, Подписное ,ВНИИПИ,Государственного комитета СССР по делам изобретений и открмтий

113035, Иосква, ф-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r, Ужгород, ул. Проектная, 4