Устройство символьной синхронизации

Иллюстрации

Показать всеРеферат

(В "»»».. 1 -

»

А.Е. Панасенко и Ю.В. Васильев

/ (72) Авторы изобретения.(71) Заявитель (54) УСТРОЙСТВО СИМВОЛЬНОЙ СИНХРОНИЗАЦИИ

Изобретение относится к технике передачи дискретной информаций и может .быть использовано в приемных уст- ройствах дискретной информации...Устройство символьной синхронизации по авт. св. Н 339009 содержит перемножители, систему фазовой автоподстройки частоты, бло анализа ин. формации и блок формирования сигнала ошибки, причем в блок формирования

)О сигнала ошибки включены интеграторы с сбросом, выходы которых через стро. бируемые схемы памяти подключены к соответствующим входам сумматоров,на

>s которые также подается сигнал с выхода системы фазовой автоподстройки частоты, выходы сумматоров через соответствующие двухполупериодные выпрямители подключены к входам вычитающего устройства, выходной сигнал с которого подается на вход системы фазовой автоподстройки частоты С13.

Ьднако,данное устройство имеет большое время вхождения в синхронизм при приеме биполярных сигналов.

Цель изобретения - сокращение времени вхождения в синхронизм при приеме биполярных сигналов. Поставленная цель достигается тем, что в устройство символьной синхронизации, содержащее перемножители, систему фазовой автоподстройки частоты, блок анализа информации и блок формирования сигнала ошибки, причем в блок формирования сигнала ошибки включены интеграторы со сбросом, выходы .которых через стробируемые схемы памяти подключены к соответствующим входам сумматоров, на которые также подается .сигнал с выхода системы фазовой автоподстройки частоты, выходы сумматоров через соответствую щие двухполупериодные выпрямители подключены к входам вычитающего устройства, выходной сигнал с которого

93072

3 подается на вход системы фазовой автоподстройки частоты, в блок формирования сигнала ошибки введены последовательно соединенные блок сравнения и дополнительный перемножи" тель, при этом выходы сумматоров подключены к входам блока сравнения,, выход одного из двухполупериодных выпрямителей через дополнительный перемножитель подключен к соответ- 10 ствующему входу вычитающего устройст.ва °

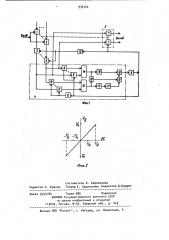

На фиг. 1 дана структурная электрическая схема предлагаемого устройства; на фиг. 2 - дискриминацион- 15 ная характеристика блока формирования сигнала ошибки.

Устройство содержит перемножите1пи 1 и 2, интеграторы 3 и 4 со сбросом, блок 5 анализа информации, систему фазовой автоподстройки частоты (ФЛПЧ) 6, блок 7 Формирования сигнала ошибки, состоящий из стробируемых схем памяти 8-11, линий задержки 12 и 13, сумматоры 14 и 15, двухполупериодные выпрямители 16 и 17; вычитающее устройство 18, дополнительный перемножитель 19, блок 20 сравнения и усилитель 21, Устройство работает следующим образом.

Напряжение от каждого интегратора 3 и 4 поступает. на две группы стробируемых схем памяти 8 и 9, 10 и 11 в блоке 7 формирования. Первая группа стробируемых схем памяти 8

35 и 9 открь:вается импульсной последовательностью, вырабатываемой системой ФАПЧ 6, а вторая группа стробируемых схем памяти 10 и 11 - той же

40 последовательностью, но сдвинутой на половину длительности символа при помощи линии 12 задержки. Напряжение со стробируемых схем памяти 8 и 9, 10 и 11 суммируется в сумматорах 14

45 и 15 и приводится к одинаковой полярности в двухполупериодных выпрямителях 16 и 17. Напряжение, снятое в середине символа, удваивается с помощью усилителя 21.

Напряжение с выходов сумматоров

14 и 15 сравнивается при помощи блока 20 сравнения, который формирует йа

2 4 выходе единичный сигнал положительной полярности при совпадении знаков и отрицательной полярности - при несовпадении. 8 соответствии с полярностью единичного сигнала, поступающего на знаковый вход дополнительно го перемножителя 19, на выходе которого формируется соответствующий знак величины удвоенного напряжения, которое вычитается с учетом своего знака в вычитающем устройстве 18 из напряжения, снятого с интегратора в конце символа, что позволяет формироватв на выходе блока 7 формирования дискриминационйой характеристики, на фиг. 2.

Полученное на выходе вычитающего устройства 18 напряжение поступает на вход системы ФАПЧ 6. Сброс интеграторов 3 и 4 производится сигналом с выхода системы ФАПЧ 6, прошедшим. через линию 13 задержки.

Таким образом, предлагаемое устройство позволяет обеспечить формирование дискриминационной характеристики с однозначной зависимостью от величины расстройки, что сокращает время вхождения в синхрониэм и повышает тем самым эффективность корреляционных приемников многоосновных сигналов.

Формула изобретения

Устройство символьной синхронизации по авт, св. Р 339009, о т л ич а ю щ е е с я тем, что, с целью сокращения времени вхождения в синхронизм при приеме биполярных сигналов, в блок формирования сигнала ошибки введены последовательно соединенные блок сравнения и дополнительный перемножитель при этом выходы сумматоров подключены к входам блока сравнения, выход одного из двухполупериодных выпрямителей через дополнительный перемножитель подключен к соответствующему входу вычитающего устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторскбе свидетельство СССР

М 339009, кл. Н 04 L 7/00, 1970 (прототип).

930722

Составитель В. Евдокимова

Редактор А. Кушнир Техред Е. Харитончик Корректор Л.бокшан

Заказ 3534/85 Тираж 685 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, M-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4