Устройство для приема дискретной информации

Иллюстрации

Показать всеРеферат

(72) Авторы изобретеяяя

8.И.!(отов и Ф.Г.Фомичев (71) Заявятель (54) УСТРОЙСТВО @В ПРИЕМА ДИСКРЕТЙОЙ ИЙФОРИАЦИП

Изобретение относится к электро связм и может использоваться в аппаратуре сеансной связи для приема сообщений с ограничеиным временем передачи по каналу связи .

Известно устройство для приема дискретной информации, содержащее . узел синхронизации-по посылкам, flepвый выход которого подключен к первому входу блока декодирования че- . рез регистрирующий узел, -а к второ» му - через блок синхронизации по циклам, другой вход которого соединен с выходом регистрирующего узла Ц.

Недостаток известного устройства заключается в nnoxoN использовании пропускной способности канала- связи, что обусловлено больюой долей синхронизирующей информации в сообщении.

Например, для наиболее оптимальной системы синхронизации с переменным щагом с усредняющим устройством беэ блокировок для вхождения в синхро2 ниэм треб щтся около 60 посылок

), С. иь- зо1.

Цель изобретения " увеличение объема принимаемой информации, а следовательно, и коэффициента использования пропускной способности канала связи.

Восставленная цель достигается тем, что в устройство для приема дискретной инфюриации, содержащее узел синхронизации по посылкам, пераФ выход которого подключен к первому входу блока.декодирования через регистрирующий узел, а к второ. му " через блок синхронизации по циклам, другой вход которого соеди" неи. с выходом регистрирующего узла, введены переключатель, формирователь сигналов записи, элемент задержки, адресный регистр, формирова" тель сигналов считывания и последовательно соединенные входной элемент И и блок памяти, выход которого подключен к другому входу регист93073 рирующего узла и к первому входу переключателя, второй вход которого соединен с выходом входного элемента И, а третий вход соединен с выходом блока декодирования, при этом выход переключателя подключен к входу узла синхронизации по посылкам, дополнительный выход которого соединен с другим входом входного элемента И и с входами формирователя сигналов записи и элемента задержки, выход которого подключен через адресный регистр к адресному входу блока памяти, а через формирователь сигналов считыванияк считывающему входу блока памяти, записывающий вход которого соединен с выходом формирователя сигналов записи.

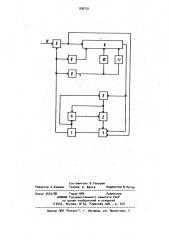

На чертеже дана структурная схема устройства.

Устройство содержит узел I синхронизации по посылкам, блок 2 декодирования, регистрирующий узел 3, блок 4 синхронизации по циклам, входной элемент И 5, блок 6 памяти, переключатель 7, фориирователь 8 сигналов записи, элемент 9 задержки, адресный регистр 10 и формирователь 11 сигналов считывания, Вход устройства 12 через последовательно соединенные входной элемент И $ и блок 6 памяти подключен к входу регистрирующего узла 3 и к первому .входу переключателя 7. Второй вход йереключвтеля 7 соединен с выходом входного элемента И 5, третий вход с выходом блока 2 декодирования, а выход переключателя 7 под".. ключен к входу узла синхронизации яо посылкам, Первый выход узла 1 синхронизации по посылкам подключен

- к первому входу блока 2 декодирования через регистрирующий узел 3, а к второму входу " через блок 4 синхронизации по циклам, другой вход которого соединен с выходом регистрирующего узла 3. Дополнительный выход узла синхронизации по посылкам соединвн с другим входом входного элемента И 5, с входом формирователя 8 сигналов записи и с входом элемента 9 задержки, выходом подключенного через адресный регистр 10 к адресному входу блока памяти, а через формирователь 11 сигналов считывания - к считывающему входу блока 6 памяти, записывающий вход кото1 4 рого соединен с выходом формирователя 8 сигналов записи.

Устройство работает следующим образом.

Принимаемое сообщение, из состава которого исключены синхронизирующие импульсы, необходимые для синхронизации по посылкам (серии "точек") поступает на вход устройства 12. На входном элементе И 5 двоичные посылки сообщения стробируются частотой

F p „, поступающей с узла 1 синх1 б ьь

1 ронизации по посылкам, где Ь, - минимальная величина коррекции фазы регистрирующего импульса.

Пачки "единиц" и "нулей" (в дальнейшем именуемые элементарными сим 0 волами), соответствующие единичным и нулевым посылкам фазового пуска и ! информации с выхода входного элемента И Б поступают на вход блока 6 памяти, в котором каждый элементарный символ запоминается по сигналу записи, формируемому с частотой формирователем 8 сигналов записи и по адресу,.выдаваемому адресным регистром 10.

Импульсы тактовой частоты постузо лают также через элемент 9 задержки в адресный регистр 10, осуществ ляя сиену адреса, а также в формирователь 11 сигналов считывания, осу" ществляя считывание информации иэ 5 блока 6 памяти по адресу, выдаваемому адресным регистром 10. Со следующим тактом частоты Р@ происходит запись очередного элементарного символа в ту ячейку памяти блока 6, из в которой предыдущим тактом частоты

Г был считан элементарный символ.

Адреса записи и считывания, формируемые адресным регистром I0, периодически повторяются, при этом цикл

4 повторения равен объему памяти блока 6, например, если объем блока памяти равен 4800 двоичных разрядов, то элементарный символ будет считан из блока 6 памяти через 4800 тактов в частоты. Таким образом, блок б памяти по существу осуществляет задержку элементарных символов на необходимое время. Элементарные символы с выхода входного элемента И 5 по55 ступают также через переключатель 7, устанавливаемый в исходное состояние сигналом с блока 2 декодирования, на вход узла 1 синхронизации упрощает также устройство передачи сообщений для аппаратуры сеансной связи, что в некоторой степени компенсирует объем вводимого дополнительного оборудования.

Формула изобретения

Устройство для приема дискретной информации, содержащее узел синхронизации по посылкам, первый выход которого подключен к первому входу блока декодирования через регистрирующий узел, а к второму - через блок синхронизации по циклам, другой вход которого соединен с выходом регистрирующего узла, о r л ич а ю щ е е с я тем, что, с целью увеличения объема принимаемой информации, введены переключатель, формирователь сигналов записи, элемент задержки, адресный регистр, формирователь сигналов считывания и no"" следовательно соединенные входной элемент И и блок памяти, выход которого подключен к другому входу ре": гистрирующего узла и к первому входу переключателя, второй вход которого соединен с выходом входного элемента И:, а третий вход " соединен с выходом блока декодирования, при этом выход переключателя подключен к входу узла синхронизации по посылкам, дополнительный выход которого соединен с другим входом входного элемента И и с входами формирователя сигналов записи и элемента задержки, вы" ход которого. подключен через адресный регистр к адресному входу блока памяти, а через формирователь сигналов считывания - к считывающему входу блока памяти, записывающий вход которого соединен с выходом формирователя сигналов записи.

Источники информации, принятые во внимание при экспертизе

1. Мартынов Е.И. Синхронизация в системах передачи дискретных сообщений. И., "Связь", 1972, с. 155 ,:(прототип).

5, 930731 по посылкам. Последний выделяет фронты принимаемых посылок и по ним подстраивает фазу регистрирующих импульсов, поступающих в регистрирующий узел 3 и блок 4 синхронизации 5 по циклам. К моменту поступления сигналов фазового пуска с выхода блока 6 памяти, регистрирующие импульсы будут находиться в зоне устойчивой регистрации посылок. Регистрирующий узел 3 в этой зоне принимает рещение о знаке принимаемой посылки. С выхода регистрирующего узла 3 информация поступает на вход блока 4 синхронизации по циклам и вход блока 2 декодирования. Блок 4 синхронизации по циклам выделяет сигнал фазового пуска и выдает его в блок 2 декодирования, где осуществляется декодирование и прием инфор- 20 мации. При этом блок 2 декодирова" ния выдает сигнал на управляющий вход переключателя 7, в результате чего на вход узла 1 синхронизации по посылкам поступают элементарные 2$ символы сообщения, с выхода блока

$ памяти, по которым регистрирующие импульсы удерживаются в зоне устойчивой регистрации посылок до конца приема сообщения. По окончании 30 приема сообщения блок 2 декодирования снимает управляющий сигнал с входа переключателя 7, и устройство возвращается в исходное состояние.

Таким образом, предлагаемое уст". ройство приема не требует передачи специальной синхронизирующей последовательности импульсов (серии "точек" 1 для цепей синхронизации по посылкам, так как она осуществляется по посылкам фазового пуска и информации. Благодаря этому уменьшает" ся длина передаваемого сообщения и увеличивается коэффициент использования пропускной способности канала связи. Этот эффект особенно заметен при малых длиных передаваемых сообщений, когда длинные серии "точек" и сообщения соизмеримы.

Исключение передачи синхронизирующей последовательности "точек"

93073 1

Составитель 6. Гальцов

Редактор A.Êóâíèð Техред 3. фанта Корректор И.Муски

Заказ 3535/86 Тираж 685 Подписное

ВНИИПЙ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, N-35, Рауаская на6., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4