Устройство для распознавания слитно произнесенных слов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскими

Социалистических

Республик ()932299 (61) Дополнительное к авт. свид-ву (22) Заявлено 17. 11. 80 (21) 3007233/18-10 с присоединением заявки № (23) Приоритет

Опубликовано 30.0582. Бюллетень ¹ 20

Р )М К з

G L 1/02

G F 3/16

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621.395. .6 (088.8) Дата опубликования описаиия30.05.82

С.Б.Аврин, A. Á.Êîïåéêèí, Г.В.Москаленко-; -- ——

В.A.Ìî÷àëîâ и Г.M.Ïåòðîâ (72) Авторы изобретения (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СЛИТНО

ПРОИЗНЕСЕННЫХ СЛОВ

Изобретение относится к области распознавания речевых сигналов, а также к устройствам вычислительной техники, в частности к периферийным устройствам ввода речевой информации в вычислительные машины и может быть использовано для подачи команд при работе с графическим дисплеем, управления работами, в информационно-поисковых системах и т.д.

Известно устройство распознавания слитной речи, работа которого основана на соединении установившихся стационарных звуков, полученных при обучении (1).

Недостатком известного устройства является невозможноеть автоматического обучения устройства за счет составления эталонов при помощи на борного поля, что приводит к уменьшению надежности. Наиболее близким к предлагаемому является устройство автоматического распознавания речи, содержащее предпроцессор, вычислительные блоки, запоминающие устройства и блок управления (2).

Недостатком известного устройства является необходимость вычисления большого числа промежуточных величин, что снижает его быстродействие.

Цель изобретения — увеличение быстродействия устройства эа счет уменьшения количества вычислительных операций.

Поставленная цель достигается тем, что в устройство, содержащее предпроцессор, первый выход которого соединен с первыми входами первого и второго запоминающих устройств, выходы которых соединены с соответствующими входами первого вычислительного блока, а его выход подсоединен

15 к перво у входу второго BH cJIHTBJlbного блока, второй вход которого подсоединен к выходу третьего запоминающего устройства, а первый и второй выходы соединены соответственно с первыми входами третьего и четвертого запоминающих устройств, причем выход четвертого запоминающего устройства соединен с третьим входом второго вычислительного блока, блок управления, вход которого подключен к второму выходу предпроцессора, а первый и второй выходы подсоединены соответственно к четвертому и пятому входам второго вычислительного блока и к первому и второму входам

932299 третьего вычислительного блока, третий выход блока управления соединен с вторым входом первого запоминающего устройства и шестым входом второго вычислительного блока, а четвертый выход блока управления сое- динен с вторыми входами второго, третьего и четвертого запоминающих устройств, введены два дополнительных запоминающих устройства, первый и второй входы каждого иэ которых соединены соответственно с первым и вторым, с третьим и четвертым выходами третьего вычислительного блока, а выходы дополнительных запоминающих устройств соединены соответственно с третьим и четвертым входами третьего вычислительного блока, пятый вход которого сое динен с вторым выходом предпроцессора, а пятый выход соединен с 20 седь ым входом второго вычислительного блока, первый и второй выходы которого соединены соответственно с шестым и седьмым входами третьего вычислительного блока.

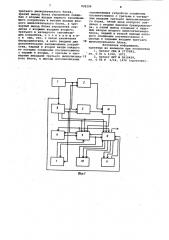

На фиг.l представлена блок-схема предлагаемого устройства; на

Фиг.2 " блок-схема блока управления; на фиг.З - блок-схема алгоритма ра- боты устройства. 30

Устройство содержит предпроцессор

1, первое запоминающее устройство 2, второе запоминающее устройство 3, первый вычислительный блок 4, второй вычислительный блок 5, третье запоминающее устройство б, четвертое запоминающее устройство 7, блок 8 управления, третий вычислительный блок 9, пятое и шестое запоминающие. 40 устройства 10 и 11, регистр 12 длины реализации, 13 — память для длин эталонов, генератор 14 тактов, счетчик

15 адреса блоков запоминающих устройств 3, б и 7, счетчик 16 отсчета эталона, схема 17 совпадения кодов, счетчик 18 номера эталона, схема 19 совпадения кода с кодом числа эталонов, счетчик 20 отсчета реализации, схема 21 совпадения кодов.

В тексте приняты следующие обозначения:

i — номер отсчета реализации;

Р; — отсчет реализации; д — число отсчетов реализации; номер отсчета эталона;

n — номер эталона1 э„. — отсчет эталона; и

3. — число отсчетов в и-м этан лоне;

N — число эталонов;

A — адрес блоков запоминающих устройств 3, б и 7; н

m, — мера сходства между Р; и

Ц а

И". — частичная мера сходства реа"1 лизации до l-ro отсчета с и-м эталоном до j-го отсчета;

V„ — номер отсчета реализации, на 1 котором проходит граница. слов, при условии, что i-й отсчет реализации сравнивается с

j-м отсчетом .n-ro эталона;

S - максимальная мера сходства

1 на -м отсчете реализации;

X . - номер отсчета начала слова реализации при условии, что оно кончилось в i-м отсчете;

У„ — номер распознанного слс ва, при условии, что оно кончается на. i-м отсчете1 порядковый номер слова от конца реализации; е — номер распознанного слова; у — номер отсчета, соответствующий концу распознанного слова;

N — число эталонов.

Устройство работает следующим образом.

В процессе обучения Диктор произносит все эталонные слова. Предпроцессор 1 преобразует их в последовательность векторов Э1,...,Э „, Il=l N, которые запоминаются в запоминающем устройстве 3. Длины эталонов 3 поступают в блок 8 управления.

В процессе распознавания речь преобразуется в предпроцессоре 1 в последовательность векторов признаков Р,,...,Р„, которые запоминаются в запоминающем устройстве 2. В блок

8 управления и вычислительный блок 9 поступает длина реализации 1.

Процесс распознавания разбивается на два этапа. Первый этап синхронизируется сигналами, вырабатываемыми блоком 8 управления. B исходном состоянии в счетчики сигналов i, j

n, A, т.е. в счетчики 20 и 16, 18 и

15, записана единица (фиг.2).

В начале процесса распознавания предпроцессором запускается генератор 14 тактов. Счетчик j 16 и счет-. чик А 15 считывают".такты. При достижении j значения Э схема 17 совпадения кодов выдает импульс, который увеличивает на единицу значение счетчика и 18 и записывает в счетчик.

16 единицу, счетчик A 15 продолжает считать. Этот процесс продолжается, пока значение счетчика 18 не достигает N, при.этом схема 19 совпадения кодов выдает импульс, который уьеличивает на единицу значение счетчика 20 и записывает единицу в счетчик и 18 и счетчик A 15. Когда значечение счетчика 20 достигает 1, схема 21 совпадения кодов выдает импульс, 932299 который записывает единицу в счЕтчик

20 и останавливает генератор 14 тактов. На этом первый этап распознавания заканчивается.

Работа вычислительных блоков íà lIepвом этапе распознавания заключается

B следующем (фиг.l). В блОк 4 приходят величины Р„. и Э" из запоминающих устройств 2 и 3 соответственно. На выходе блока выдается мера сходства

m< между входными величинами. и

В блок 5 поступают информационные сигналы m "; иHэ б6лnоoк а 44, Ми, из

Р 1 -Ч запоминающего устройства б, Ч„" из запоминающего устройства 7, S

1 иэ блока 9. Данный блок вычисляет 5 величины M и V.. которые эаноминаюти и ся в запоминающих устройствах б и 7 соответственно и поступают на входы блока 9. Блок 9 вычисляет величи ну S; a также величины У(и Х, ко 20 торые запоминуются в запоминающих устройствах 10 и 11 соответственно.

Алгоритм р боты блоков 5 и 9 зависит от значений поступающих в них управляющих сигналов i, j n и для основных комбинаций значений этих сигналов заключается в следующем (фиг.3).

j=I, n=I блок 5 произнодит вычисления и и, и

М11 Щ11 1 V«9 11 блок 9 вычислений не производит

2. 1< j <Э«, n=l, i=1 и " и. и блок 5:М =max IM„.,«,m"; 1, V„>. — — 1„ блок 9 вычислений не произ водит.

3, j= Э n=l i=1 блок 5: аналогично пункту 2, и. и блок 9: Si=М, Y„-п, Х„- =V ).

4 . j =l l

5. 1 cj <Эи, 1

40 аналогично пункту 2. б» j= Эи, 1<п<14, i= 1 блок 5 аналогично пункту 2. и и

EJIoK 9:ес и М„-j S1 то S„™„,У(=п если M;- - SÄ:, то блок 9 вычислений не производит, 10

30

Формула изобретения

Устройство для распознавания слитно произнесенных слон, содержащее предпроцессор, первый выход которого соединен с первыми входами первого и вторбго запоминающих устройств, выходы которых соединены с соответствующими входами первого вычислите льного блока, а его выход подсоединен к первому входу второго вычислительного блока, второй вход которого подсоединен к выходу: третьего запоминающего устройства, а первый и второй выходы соединены соответственно с первыми входами третьего и четвертого запоминающих устройств,,причем выход четвертого запоминающего устройства соединен с третьим входом второго вычислительного блока, блок управления, вход которого подключен к второму выходу предпроцессора, а перный и второй выходы подсоединены соответственно к четвертому н пятому входам второго вычислительного блока и к первому и второму входам

50 и 55 ,М1 4Ä .«+

65

7. j=l, n=l, 1

8. 1

9. j= 3, к n=l, 1<1«? блок 5 аналогично пункту 8.

Блок 9 аналогично пункту 3.

10. j=l, 1

Блок 9 вычислений не производит.

11.

Блок 9 вычислений не производит.

12. j= J„, lcn

Блок 9 аналогично пункту б.

- Второй этап процесса распознавания состоит в рассмотрении нычислительным блоком 9 содержимого запоминающих устройств 10 и 11 с целью определения последовательности номеров распознаваемых слов. На этом этапе на адресный вход запоминающих устройств 10 и 11 подается сигнал g из блока 9. Величины

У и Х« поступают иэ этих запоми нающих устройств на входы блока 9, который нычисляет последовательность номеров распознанных слов е+-« ° ° -,eq °

Алгоритм вычисления состоит и, сл едующем:

1. t=l, е =у„, у=Х« -1

2. t=t+l,-е =у«), р=Х«)-1

3. если у=О, то конец, иначе на пункт 2.

Повышение быстродействия предлагаемого устройства достигается введением двух новых запоминающих устройств и изменениями сн язей между имеющимися блоками, что сделало возможным производить распознавание с меньшим количеством вычислений.

Кроме повышения быстродействия предлагаемое устройство использует меньший объем памяти, чем известное.

932299 третьего вычислительного блока, третий выход блока управления соединен с вторым входом первого запоминающего устройства н шестым входом второго вычислительного блока, а четвертый выход блока управления соединен с вторыми входами второго, третьего и четвертого запоминающих устройств., о т л и ч а ю щ е ес я тем, что, с целью увеличения быстродействия, в него введены два дополнительных запоминающих устройства, первый и второй входы каждого из которых соединены соответственно с первым и вторым, с третьим и чет вертым выходами третьего вычислитель-,15 ного блока, а выходы дополнительных запоминающих устройств соединены соответственно с третьим и четвертым входами третьего вычислительного блока, пятый вход которого соединен с вторым выходом предпроцессора, а пятый выход соединен с седьмым входом второго вычислительного блока, первый и второй выходы которого соединены соответственно с шестым и седьмым входами третьего вычислительного блока.

Источники инФормации, принятые во внимание при экспертизе

1. Патент США Р 3770892, кл. G 01 Т 1/02, 1973.

2. Патент ФРГ Р 2610439, кл. G 06 F 3/16, 1976 (прототип).