Устройство для вычисления логарифмов чисел

Иллюстрации

Показать всеРеферат

О Л И С А Н И Е

И306РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социапистическии

Республик (6l) Дополнительное к авт.свиц-ву—

{22) Заявлено 30.06.80 {21) 2949 764у18 24 с присоединением заявки,%(23 т Приоритет

Опубликовано 30.05.82. Бюллетень № 20

Дата опубликования описания 03.06.82 (51 ) М. Кл. (06 Р 7/556 фщдарстеанай комитет

СССР ю делая изееретеиий и атермтий (53) УДК 681

° 3 (088.8) (72) Авторы изобретения

Г. Е. Пухов, А. И. Стасюк, Ф. Е. Лисняк и A. И. Гузенко, В(.ЕСОЮЗтт " з ИАТЕГ:""

ТЕХНР . " стицньлиo оt ...А (71) Заявитель

Киевский ордена Трудсвого Красного Знамени инженеров гражданской авиации (54) УСТРОт{СТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМОВ

ЧИСЕЛ

Изобретение относится к вычислительной технике и может быть использовано в составе универсальных вычислительных ма, шин или специализированных вычислительных устройств для вычисления с высокой

5 точностью и быстроцействяем логарифмов чисел с произвольным основанием, например, в системах автоматического управления динамическими обьектами.

Известно устройство, содержащее регистр результата, счетчик с управляемым коэффициентом пересчета, коммутатор, два блока памяти, тря счетчика, элементы ИИЛИ, причем второй вход первого блока памяти соединен с вхоцом второго блока памяти, выход которого подключен к первой группе вхоцов элементов И-ИЛИ, вторая группа вхоцов которого соединена с выходами первого счетчика, подключенного своим входом к выходу счетчика с уп-2о равляемым коэффициентом пересчета 11.

Недостатком устройства является низ кая точность из-за необходимости реализации кусочно-линейной апроксимации, няз2 кое быстродействие, определяемое необходимостью органязации пересчета коэффициентов, я относительная сложность, оп ределяемая наличием двух блоков памяти.

Наиболее близким к предлагаемому по технической с щности является устройстве, соцержащее регистр числа, первый и второй регистры результатов, накопитель, блок управления, элементы И, ИЛИ, схему сравнения, блок деления, кольцевой сдвигающий регистр, причем первые входы элементов ИЛИ первой группы являются ° информационными вхоцами устройства, вгорые входы подключены к соответствующим выходам блока деления, а выходы - к соответствующим входам регистра числа 2).

Не достатком известного устройства является относительная сложность, опрецеляемая необходимостью работы устройстве в трех режимах, а также наличие накопителя, низкое быстроцействяе, определяемое необходимостью реализация в кажцом из (Р +ттт) тактов определенного количества микротактов, ограниченные функцнона93249 1 льныо возможности, так как в известном устройстве опрецеляется только натуральный логарифм числа (что обьясняется наличием в накопитегю значений8®,Д = Р, 1-в ° ° 11 О1 1в °

Цель изобретения — расширение функциональных возможностей, увеличение быстроцействия и упрощение устройства для вычисления логарифмов чисел.

Указанная цель постигается тем, что О в устройство цля вычисления логарифмов чисел, содержащее три регистра, цва элемента ИЛИ, схему сравнения и сдвигающий регистр, дополнительно введены два сумматора по модулю два, регистр, блок извлечения корня и параллельный множительно-целительный блок, к первому входу

-которого подключен выход блока извлечения корня и вхоц первого регистра, подключенного своим abri .oöoì к входу блока извлечения корня, к первому н второму входам первого сумматора по модулю пва подключены соответственно выхоцы первого и второго элементов ИЛИ, выхоц первого сумматора по модулю пва соецинен с 5 первым вхоцом второго сумматора по модулю два, выхоц второго регистра соединен с вторым вхоцом параллельного множительно-целительного блока, управляющий вход которого соединен с выХоцом второго сумматора но моцулю цва, разрядные выходы — с входом второгорегистра, а выхоцы старших разряпов - с первым вхопом схемы сравнения, подключен» ной своим выхоцом к входу сдвига сдви35 гающего регистра, выход млацшего разряда которого подключен к второму вхо цу второго сумматора по модулю цва, выходы (n +1) старших разрядов третьего и и разрядов четвертого регистров поц40 ключены соответственно к вхоцам второго и первого элементов ИЛИ, выход второго элемента ИЛИ соединен с вторым вхопом схемы сравнения, выхоцом которой является выход сумматора по модулю цва.

При этом множительно-делительный

45 блок содержит групп одноразряпных сумматоров по (%, +1) в каждой (гце Мразряпность выходного кода), первую группу из (4+1) коммутирующих узлов и (k -1) групп из (Ф(+3) коммутирующих узлов в каждой (1+1)-ой группе (i =1, 2,..., 1с ), причем выхоц. кажцог о Р-го оцноразрядного сумматора (Р =1,2,.„К+

+1) . i -ой группы соединен с первым входом (0 = 1)-го оцнораз ряцн ого сумматора (0+1)-ой группы, второй вхоц которого подключен к выходу (В +2)-го ком-. мутирующего узла (1 +l)-ой группы, поцключенного своим вторым вхоцом к выходу первого коммутирующего узла этой же группы, третьи входы (Р +2)-ых коммутирующих узлов (E +1)-ой группы обьецинены и подключены к пятому и шестому вхоцам соответственно (Р + 1)-го и 8 -го коммутирующего узла первой группы и к входу 3 -го разряда первого входа множительно-целительного. блока, первые входы кажцого коммутирующего узла

1 -ой группы обьепинены и поцключены к управляющему входу устройства и третьему входу (9 +1)-го оцноразрядного сумматора первой группы, выход переноса первого одноразрядного сумматора i -ой группы соединен с вторыми входами первого и второго коммутирующих узлов соответственно (i +1)-ой и. 1-ой групп, третьи вхоцы второго и первого коммутирующих узлов (1 +1)-ой группы подключены соответственно к выходу первого одноразрядного сумматора i -ой группы и к вхоцу (+2)-го разряда второго входа множительно-делительного блока, âõîды первого и второго разрядов которого соединены соответственно с. вторым и четвертым входами коммутирующих узлов первой группы, третий вход каждого 1-го коммутирующего узла которой подключен к входу 1 -го разряда второго входа множительнс -целительного блока, вход каждого (К +1)-го разряца которого соединен с вторым входом (1+3)-го коммутирующего узла (1+1)-ой группы, подключенных своими выхоцами к третьему вхопу одноразрядного сумматора (i +1)-ой группы, первый и второй входы каждого -го одноразрядного сумматора первой группы поцключены соответственна к первому и второму выходу j -го коммутирующего узла первой группы, второй вход (4 +1)-го одноразрядного сумматора (1 +1)-ой группы соединен с вторым выходом (К+2)«го коммутирующего узла .(з +1)-ой группы, подключенного своим пятым входом к входу младшего разряда первого входа множительно-целительного блока, а четвертый вход (1+2);го коммутирующего узла второй и (4+2)-ой грунп соединен соответственно с входом второго разряда второго входа множите- . льно-делительного блока и с выходом первого коммутирующего. узла (4 +1)-ой группы,. высод переноса первого однораз/ ряцного сумматора первой группы, выхоц первого коммутирующего узла каждой (i +1)-ой группы. и выход. каждого оцноразрядного сумматора 4.-ой группы соединены с выходами множительно-дели249 1 6 пы, второй вход которого соединен с выходом (3 +1)-го элемента ИЛИ группы, выход (п -1)-го элемента ИЛИ которой соединен с первым входом первого сумматора по модулю цва каждой 1 -oN цополнительной группы, вхоцом (и -1)-го элемента НЕ группы и вторым входом (и -2)-ro элемента ИЛИ группы, второй

:, вход (и +2-1 )-го одноразрядного сумматора 1 -ой группы соединен с входом (2n 2 + 1)-го разряда блока извлечения корня, {2 п -2 1 +2)-ый разряд которой подключен к третьему входу одноразряцнаго сумматора к входу {rr -1)-го элемента HE группы, первый ы второй входы разрядов входа блока извлеченмя корня подключены к входам (rr -1)-го элемента

ИЛИ группы, к первым входам соответственно первого и второго одноразрядного сумматоров (п -1)-ой группы, вторые входы которых соединены соответственно с выходом (rr- -1)-го элемента НЕ группы и генератора единиц, подключенного к первому входу третьего одноразрядного сумматора, и (rr -1)-ой группы, выходы переносов первых одноразрядных сумматоров и выхоц (п -1)-го элемента ИЛИ группы являются выходвмм блока ызвлечения корня, а вхоц каждого элемента И и выход каждого rr -го сумматора по моqymo gba группвыполненыв вице инверсных.

Пры этом коммутирующие узлы первой группы содержат два элемента 2И-ИЛИ„ причем первый вход узла соединен с первыми и вторымм входамы первого и второго элементов 2И-ИЛИ, второй ы третий входы узла подключены к третьему ы четвертому входам первого элемента 2И-ИЛИ, четвертый и пятый входы узла соединены с третьим к четвертым вхоцамы второго, элемента 2И-ИЛИ, пятый и шестой входы узла подключены к пятым входам соответственно второго ы первого элементов

2И-ИЛИ, выходы которых являются соответственно вторым к первым вьщоцамм коммутирующего узла.

При этом в каждой группе (i =2, 3, ..., k) коммутирутощке узлы с первого по третый содержат четырехвходовый элемент

;2И-ЙЛИ, коммутирующые узлы с четвертого по (k +1)-ый содержат пятквходо, вый элемент 2И-ИЛИ,(1< +2)-ый коммутирующий узел содержит два элемента ,2И-ИЛИ, (1+3)-ый коммутирующмй узел содержит элемент И, причем первый ы второй входы четырехвходового элемента 2И-ИЛИ соединены с первым вхоцом входы j -го коммутирующего узла (j =-1,2,3), 5 93 тельного блока, третий вход третьего .коммутирующего узла (1 +1)-ой группы соединен с выходом переноса первого оцноразряцного сумматора (М +2)-ой группы, выход переноса первого одноразрядного сумматора второй группы соецынен с четвертым входом первого коммутырующего узла первой группы, пятый .вхоц которого подключен к управлятащему вхоцу параллельного множытельно-целытельного блока, а одноразрядные сумматоры каждой i -ой группы обьединены цепями переноса °

Блок извлачени я корня содержит . (к -1) (k-разряцность выходного кода) 15 группу последовательно соединенных одноразрядных сумматоров, группу сумматоров по модулю два, группу элементов

ИЛИ, группу элементов НЕ, (и -2) цополнктельных групп ые (rr -1-1) (гце i » »2e номер группы) сумматоров по модулю цва

s каждой группе, генератор единиц ы группу ыз (n -2) элементов И, каждая 1 -я группа (4 =1,2,..., rr -1) одноразрядных сумматоров содержит (и +2 - ) оцнораз-25 рядных сумматора, а группы эл.ментов

ИЛИ, элементов НЕ и сумматоров по модулю два соответственно содержат (д -1) и {и -2) элементов, причем выхоц каждого j -го одноразрядного сумматора 30 (1 +1)-ой группы соединен с первым входом (j -1)-ro одноразрядного сумматора 1 -ой группы, второй вход первого одноразрядного сумматора i-ой группы соединен с выходом переноса первого orr- 55 норазрядного сумматора {i+1)-ой группы, первыми входами -ых элементов И,ИЛИ, сумматоров по модулю два групп и суммазаров по модулю двв i -ой дополнительной группы, выходы которых соединены с вторыми входами j -ых (=2,...rr-i ) одноразрядных сумматоров -ой группы, вторые входы -ых (1 =2,..., и - i-1) сумматоров по модулю два 1-ой дополни« тельной группы соединены с выходами пе-45 реноса первых одноразрядных сумматоров (н - j +1)-ых групп, выход 1 - го элемента НЕ группы поцключен к первому входу { и +1- i )-го одноразрядного сумматора i -ой группы, второй вход котораго соединен с выхоцом i --ro элемента И группы, подключенного своим вторым входом к выходу переноса первого одноразрядного сумматора (i -2)-ой группы, первый вход (n +2-i )-ro одноразрядного

55 сумматора 1-ой группы подключен к выходу 1 -oro сумматора по модулю rrsa группы, подключенного своим вторым входом к выхоцу l -го элемента ИЛИ груп91 8 два, где. (v+m+1) - количество разрядов представления информации. Множительноцелытельный блок (фыг. 3) содержит одноразрядный сумматор 12 ы коммутырующые узлы 13-17, входы 18 ы 19, выходы 20 н 21, Блок нзвлеченыя корня (фиг. 8) соцержыт оцноразрядные сумматоры 22, сумматоры 23 по модулю два элементы

ИЛИ 24, элементы НЕ 25, сумматоры 26 по модулю два, элементы И 27, генератор 28 единиц, входы 29 и выходы 30.

Работа ус тройства обьясняегся на примере определения логарифма числа М с основанием с, т.е.

Pop и =Х. (2) ОРИ

7 9324 второй и третий вхоцы которого соецынены с третьим и четвертым вхоцами четырехвходового элемента 2И«ИЛИ, выход которого является выходом -го коммутиру1 ющего узла, первый вход пятивходового элемента 2И-ИЛИ является первым входом

j<-го коммутирующего узла, (=4,5, . ., +1), второй ы третий входы которого соецинены соответственно с вторым и четвертым, пятым входамы пятивходово- 10 го элемента 2И-ИЛИ, выход которого является вьыодом g -го коммутырующего узла, первый вход (%+2)-го коммутирующего узла соединен с первыми входами первого н второго элементов 2И-ИЛИ и 15 вторым входом второго элемента 2И-ИЛИ, второй вход (1 +2)-ro коммутирующего узла соединен с вторым входом первого элемента 2И-ИЛИ ы третьимы входамы первого и второго элементов 2И-ИЛИ, 20 третий вход (1с +2)-го коммутирующего узла соединен с четвертым н пятым входами первого элемента 2И-ИЛИ, четвертый и пятый входы (3<+2)-го коммутирующего узла соецинены соответственно с 25 четвертым н пятым входами второго элемента 2И-ИЛИ, выходы первого и второго элементов 2И-ИЛИ являются выходами (Ж +2)-го коммутирующего узла входу третьего одноразрядного сумматора 30 (n -1)-ой группы, выходы переносов первых оцноразряцных сумматоров ы выход (и -1)-го элемента ИЛИ группы являются выходами устройства, а вход каждого элемента И и выход каждого — го сум- .

35 матора по модулю два. групп выполнены в вице инверсных.

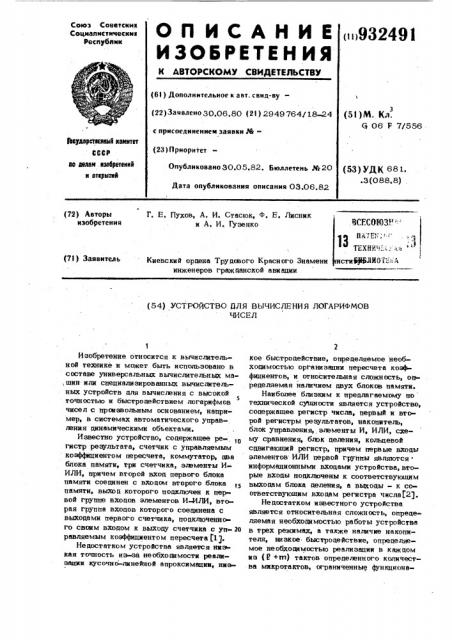

На фиг. 1 показана схема устройства цпя вычисления логарифмов чисел; на фиг. 2 — схема сравнения устройства; на фиг. 3 — схема параллельного множительно-целительного устройства цля случая, когда информация представлена К= и + m+ 1=

=4 двоичными разрядами, на фиг. 4-7 приведены коммутирующые узлы; HB фиг.845 блок извлечения корня для случая, когда информация представлена К = 5 цвоичными разрядамы.

Так как величины @ X могут принимать разлычные значения больше нпы меньше единицы, то знак Х мщсет быть определен в соответствии с таблицей

Представим выражение (1) в разрядной форме (2), "(1)

4 1 И М

Х" APM ч(1)

О и < ПРИМ

Ч (1+1) %1 ФФ1

"(4) .

«4444) ll++1

t4 d М =О ч (0%1) nfl

=П, 8 =И, Х =COnet=-1

1= ПаП а- ° ° ">Оа

Устройство для вычисления логарифмов чисел (фыг. 1) содержит четыре регистра

1, .два элемента ИЛИ 2, схему 3 срав50 нения, двигающий регистр 4, цва сумматора 5 по модулю два, множительно-делытельное устройство 6, блок 7 извлечеа ныя корня, управляющий выхоц 8 устройства. Схема 3 сравнения (фиг. 2) выпол55 иена, например, в виде (n +1) вхоцового элемента ИЛИ 9, (й +2)-входового элемента И 10 н сумматора 11 по моцулю разряцные векторы, предсгавляющие собой разрядное изображение чысел0, М ы Х соответственно. Э соответствии с выражеИ <

"аЯ !

)(, щи

М4(Ц У

О И 4 п и H(i

4 °

М (4J Я -О

ВРИ

К d Х=1

" 4(i><) 3S < „+ ) v п+

i=tl Й =Й, }(=сОпМ=(Пример ср1,И>1,9=10,И =20,539, и

}М 20,539аж 1,3 125 — 1,0101 1 0,-1,-2,-3,-4. 4О 1}= 20 539, 10 "=2 0539 ) 1 Х =l

М = 2,0539 ° 10 ™-0,6495002< 1,Х=О

М =0,6495002 - 10 ™вЂ”

-1

-" 1,1549927)1, X =1 45

H =1,1549927 10В

- Разрядная матрица, представляюшая со.. бой изображение целителя Ч прк и =4.

Для уаабауяр xnnoxiexxn рееряаяые ееяФ торы, Х, и разрядная матрица ( представлены для случая, когда запятая фиксируется перец старшим разрядом.

Процесс определения 1 -го разряда

)l (i =l,2,...ï ) искомого вектора Х реали-. зуется по выражению (l), щецставленноМу прк п =4 и развернутой форме. на оснсванкк завкскмости вкца.(i+<)»

= (ИРИ о "" =о, = д,...., -Ъ 0,866 1224 <1, X = О

М = 0,866 1224 10 =

-4

= 1,0001224> 1, X =1

Й. =0,8660053 - (gp )

-3

= 1,1548367>1, Х =" 4 =1,1548367-(-" )

-.4

= 1,0000472>1, X =1. где f — значение переноса из старше (14 1} го разряда вектора + определя- емого по выражению

Р " =(ж"Нф", <е1

° - величина, пркнимаюшая значе(i) 9 93249 1 10 кием (3) вектор 5 может быть записан в Работу множктельно-целктеа нога блока вкде,поясним на примере определения частногю

„ я „ а, -1Г,, щ я, « X, wnxuoro 2 х аеаяуеая Y n p6mxua яе

N=a ...<3 <3 ...<5 =Й <3 . (4) ленкя и произведения 2 сомножителей Х,у в режиме умножения.

Учитывая тот факт, что лагаркфмическая Paga> десвния. Частное Х рпределяфущщия с основаикем 4 симметрична от- ется на основании выраженкя j-Yx=p у насительно оск абсдксс с логарифмической представленного в разрядной форме в виде функцией с основанием1/с, то в соответ- V чч ч ствии с выражением (4) и данными табли- и - YX =О, (6) .ды значение каждого Т- го (1=п, п=-1, ... q,0-q,...-щ) paapsga k нскомаговектора r geZ. 7 --- 2 -. 7» разрядный вектор, М для случаям 1, И 7 1 или а<1, й<1 может быть определена по выражению (2). представляющий сабай разрядное кзобра«

В том случае, когда 6>1, И <1 или 1$ жение делимого 2 б< 1, Й > 1 значение каждого 1-го раэ- . ч < i ч.п ряда 4 искомого вектора определяется . }(» X ... }(... y O= 0 .. -.., аналагкчна по выражению: и"(} разрядные векторы, представляюшие собой

1 " И. Ъ

20 разрядное изображение частного и ну}(ври пя 0;

v f(i} Ч

6 И <1,@pe И (93249 1 12 где f - значение переноСа из старше() +1P

")1И го разряда вектора g "), определяемого на ссновании выражения

P) о„ Ig)i)I (i) (q 1 (1) пеи

f(=о, соответственно. (з вышеизлакенного видН0 что pip)f f = 1, Z = . в(" =2 ". Для конкретных значений Y =-0,68 ?5 2 =

=O,4296875 и соответственно X=0,625

v или в разряпной форме V-= p Q (.1

z z zV3 ""- 3 3 ч и Х=

7. = 0 1 ) 0 ) 2. зо

)в), ;);П «» ) И

ЖК")2щ ЖвщЕя савв>.)))ир l)le = tt

zl t т»= щнн

С зо

С

rt%)- II- te)=x=a

7(4)= 0401 (=.(040

С

И4)=х=q

Ъ р =х=а () ф

Операми умножения. Частное Х сомно» жителей Х, Y осушествляется в соответ- <а ствии с выражением чч ч

YX =2.

Работа блока извлечения корня 7 = М ссуществляется следующим образом. Старv ший разряд 7 искомого вектора 2 определяется на основании зависимости

Z= d Ч С(° (И) f(И)„

ПРц о е!"" =о, 55

I 2 I,IÌI- - модувв веввовав % в ) на основании выражений (2-5) получаем

)11

Далее каждый последующий разряд Z

=1,2,3... p искомого вектора 1 определяется по выражению

- величина, принимающая значения в

4Е) соответствии с выражением (9

При 11 =1 Ь(") =АЕ(1>=2 ",а (У, Х(), ... Z(" ") соответственно

Iv., Z(= Z2 0 -(Ю= 2. 7.) н

Й 2. ч(п qJ 1 Я. 3 В-Q. п-1 1 )-1 г =2.Z7. 7. 7. Zli 4 где

2.=Z.hZ. ) 2 = 1 85, 6= .Ч4 f3=Z.(И)

Для конкретного значения а — Z.= 0,4306640625 искомая величина Z соответственно Z =0,65625 или в разрядной форме

Ч М t ,1 = .(0 0 1, а= 0 (1 0 (1 .(0 0 (Старши.й разряд 1 искомого вектора с . в сиду выражения (11) равен 5ay8=

=OY 1=1 и далее на ссновании выражений (12), { 13), (9) получаем: (, Е вв Н цн .ЬЯ НБ)Е )в) )= Яо по ) т

С 4С

Р= гяо (ъ

=-7=4

44 ((0( С ф ® =Z=0

)(. я. "1п)

) )" )е" = (00)

5 у(й = =

Работа устройства для вычисления ло- гарифмов чисел происходит следующим образом. B исходном состоянии в четвертый .регистр 1 заносится основание сМ и хра- :. нится до тех пор, пока вычисляются лога-10 рифмы чисел Й по данному основанию О.

Во второй и третий регистры 1 заносится числа К, причем в третьем регистре 1 число N хранится в течение цикла работы устройства, т.е. в течение вычисления ло- 15 гарифма. В первый регистр заносится основание ct, если вычисляются логарифмы, у которых запятая фиксируется перед старшим разряцом, и Ф, если запятая фиксируется после (и +1) старших раз- g0 радов. B младший разряд сдвигающего регистра 4 заносится единица. Далее ь устройстве происходит переходной .процесс, после окончания которого на выходах первой и второй элементов ИЛИ 2 оп-д5 ределяется больше или меньше единицы основание а и числа М, а на выходе первого сумматора по модулю дьа образуется значение знака вычисляемого ло гарифма в соответствии с таблицей 1, которое хранится в течение цикла работы и определяет вычислительный процесс по

° выражению (4) или (5) соответственно, при етом с выхода ьторого элемента

ИЛИ 2 на управляющий вход схемы срав.. кения 3 поступает значение 1 или О, 35 соответствующее Й 7 1, или Й <1, которое определяет режим работы по верхней или нижней формуле выражения (4) или (5). В частном случае, когда а >1 и Й ) 1

40 на выходе перва о сумматора по модулю два образуется сигнал "О, соответствующий положительному значению логарифма, а на выходе второго элемента ИЛИ 2 и соответственна управляющем входе схемы

3 сравнения образуется сигнал «1, опре45 деляющий режим работы по верхней формуле выражения 4. При этом на управляющий samoa множительпо-целительного блока 6 будет поступать единичный сигнал, соответствующий операции, на первый 50 вход будет поступать с выхода блока 7 и+1 извлечения Каряя значение d = d, а

1 на второй вход из выхода второго реги н" ) ф

55 стра 1 соответственно М "+ =4. В множительно-деиительйом блоке реализуется. операция деления а на его выходе образуется значение N(n,(й+1) старших разря91 14 цов которого поступает на вход схемы

3 сравнения, в которой по выражению (4) опрецеляется значение старшего разряда 7 логарифма. Так заканчивается первый такт работы устройства.

Второй такт работы начинается при поступлении на управляющий выход 8 устройства импульса, благодаря которому но переднему фронту, в сдвиговом регистре

4 осуществляется сдвиг информации, благоцаря чему в младший разряц регистра

4 записывается значение ), вычисланного на предыдущем такте, а в первый и второй регистры 1 записываются с выходов соответственно блока извлечения корня 7 и множительно-целительного блока п v(п1

6 значения сР и N . При этом благодаря таму, что в младшем разряде сцвигового регистра 4 записано значение Х, посту пающее на второй вход сумматора но модулю два 5, на его выходе появляется сигнал О . или единица, который настраиват параллельный множительно-делительный блок 6 на режим умножения или деления оответственно. После этого s устройстве происходит переходной процесс аналогично вышеописанноМу, ь результате чего На выходе схемы 3 сравнения образуется знаи-1 чение последующего разряда Х логарифма. числа, а устройство rmaso к следующему такту работы. В результате выполнения (П +Hl+ 1) тактов (r.å. подачи и+пи-1 импульсов на управляющий выхоц 8 устройства) в сдьиговом регистре будет записано значение логарифма М числа М по цнн«

V ному основаниюа, знак логарифм, а М при этом определяется значением сигнала на выходе первого сумматора 5 по модулю два в соответствии с таблицейР

Использование новых элементов — двух сумматоров по модулю цва, регистра, блока извлечения корня и множительно-целительного устройства, а также наличие новых связей между ними, выгодно отличает предлагаемое устройство, так как ь цанном устройстве существенно расширяются функциональные воэможности, определяющие вычисление логарифма произвольного числа по любому основанию, а не только натурального логарифма, как в прототипе, кроме того, предлагаемое устройство существенно известных ибо ь нем не используется блок памяти, а также существенно упрощается организация вычислительного процесса, так как для подучения (р +гй+1)=разрядного значения ла гарифма в предлагаемом устройстве необходимо на управляющий выхоц 8 устройства подать всего (и+п +1) импульсов, в то

93249 1 16 первую группу из (К+1) коммутирукицих

Узлов и (g -1) групп из (к+3) коммутирующих узлов в каждой (1+1)-ой группе (1 =1,2,...,К), причем выход каждого

0 -го одноразрядного сумматора (Р =1,2, °... 1+1) т -ой группы соединен с первым

Входом (к -1)-Го одноразряпноГО сумматора (т +1)«ой группы, второй вход которого подключен к выходу (Р +2)«го коммутирукицего узла (1 +1) -ой группь

ПОДКЛЮЧЕННОГО СВОИМ ВХОДОМ К ВЫХОДУ первого коммутирующего узла этой же группы, третьи входы (Р +2)-ых коммутирукицих узлов .{ i + 1) -дй группы обьедн15 иены и подключены к пятому и шестому входам соответственно (Р +1)-го и В -t.o коммутирующего узла первой группы и к входу 8-го разряда первого Входа множительно-делительного блока, первые Входы каждого коммутирукицего узла 1-oN группы обьединены н подключены к управляющему входу устройства и третьему входу (k +1}-го одноразрядного сумматора первой группы, Выход переноса первого одноразрядного сумматора i -ой группы соединен с вторыми входами первого и второго коммутирующих узлов соответственно (i +1)-ой и i -ой Гру пн, третьи входы второго и первого коммутиI рующнх узлов (i +1)»ой группы подключены соответственно к выходу первого одноразрядного сумматора г -ой гттуппьт и к входу (1 +2)-го разряда второго Входа множительно-делительного блока, входы первого и Второго разрядов которого соединены соответственно с вторым и четверрым Входами коммутирукицих узлов перВой Группы, третий ВхОд каждОГО ГО коммутирующего узла которой подключен к входу 1 t o разряда второго входа множительно-делительного блока, вход каждого (k +1)-Го разряда которого соединен с вторым входом (f(+3)-t о коммутирующего узла (т +1)-ой группы, подключенHblx сВОими ВыхОдами к третьему Входу одноразрядного сумматора (1 +1)-ой руппы, первый н второй входы каждого i -Го одноразрядного сумматора первой группы подключены соответственно к первому и второму Выходу 1 -го комМутирутощего

15 время, как в прототипе для реализации вычислительного процесса организовано три режима работы. Кроме того, в предлагаемом устройстве существенно увеличивается быстродействие благодаря тому, что каждый5

-й разряд искомой величины otlp eemeTся за один такт(а вся Вепичина заП+

+III+1 тактов), длительность которого равна времени переходного процесса в схеме, которое в свою очередь равно не- 1о скольким сотням наносекунд, если устройство, например, построено на интегральных схемах серии 155, 1. Устройство для вычисления логарифмов чисел, содержащее три регистра, два элемента ИЛИ, схему сравнения и сдвигающий регистр, о т л и ч а ю ш е е с я тем, что, с целью повьииення быстродействия, в него введены два. сумматора по. модулю два, регистр, блок извлечения корня и параллельный множительно-делительный блок, к первому входу которого подключен выход блока извлечения корня и вход первого регистра, подключенного своим выходом к входу блока извлечения корня, к первому и второму входам перво30 го сумматора по модулю два подключены соответственнб выходы первого и второго элементов ИЛИ, Выход первого сумматора по модулю два соединен с первым входом второго сумматора по модулю два,. выход второго регистра соединен с вторым входом параллельного множительноделительного блока, управлякиций вход которого соединен с выходом второго сумматора по модулю дьа, разрядные выходыс входом второго регистра, а выходы старших разрядов - с первым входом схемы сравнения, . подключенной своим выходом к Входу сдвига сдвигаюшего регистра, выход младшего разряда которого подключен к второму Входу второго сумматора по модулю дьа, выходы (и +1) старших разрядов третьего и и -разрядов четвертого регистров подключены соответстьенно к входам второго и первого элементов

ИЛИ, выход второго элемента ИЛИ сое- 50 динен с вторым входом схемы сравнения, выходом которой является выход сумматора tlo Модулю два.

2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что множительно-дели- $5 тельный блок содержит g групп одноразрядных сумматоров по (К+1) в каждой (где 1с - разрядность выходного кода), узла tlepsoN группы, Второй вход (К+1)-го одноразрядного сумматора (i +1)-ой группы

Формула изобретения соединен с ьторым выходом (@ +2)-ro коммутирующего узла (1 +1)-ой группы, подключенного своим пятым входом к входу младшего разряда первого входа множительно-делительного блока, а четвертый вход (k+ 2)-го коммутирующего узла второй и (к +2) -ой групп соединен соответст17 932491 18 венно с входом второго разряда второго нен с вых с выходом 7 -го элемента И груп»ченного своим вторым входом вхоца множительно-делительного блока и с пы, подключенного св выходом первого комлтутирующего узла к выходу пеоеноса первого одноразрядного (+ )- ре первого сумматора (т-2)-ой группы, первый вход одноразрядного сумматора первой гттуппы, 5 (п +2- )-одноразрядного суммато а -ой выхоц первого коммутирующего узла каж группы подключен к выходу f -го суммацой (f +1)-ой группы и выход каждого од- тора по модулю два г оцулю два группы, подключенноноразряцного сумматора f,-ой группы сое- го своим вторым вхо торым входам к выходу i-го динены с выходами множительно-делительно- элемента ИЛР г го б группы, второй вхоц которого лока, третий вход третьего коммути- !9 го соединен с

/ ° Ъ динен с выходом (! .+1)-го элеменРующего узла (т +1)-ой группы соецинен ИЛИ та группы, вькоц (и -1)-го элемента с выходом переноса первого оцноразряцно- ИЛИ которой соединен с первым входом го сумматора (! +2) -ой группы, выход первого сумматора,по модулю два каж-, переноса первого одноразрядного суммато- и дой 1 -ой дополнительной группы, входом . ра второй группы соединен с четвертым т3 (1) (и - )-to элемента НЕ группы и вторым входом первого коммутирующего узла пеР- вхо ом (?т -2)-г вой группы, пятый вход которого поцклю- второй вхоц (и +2-i )-ro одноразрядного чен к управляющему входу параллельного сумматора > -ой группы соединен с входом множительнсделительного блока, а одно- (2п 2+1) б п — + )-го разряда блока извлечения

Разрядные сумматоры каждой i -ой группыщ (2 2 2} обьецирены цепями переноса. корня, (rl-2т +2}-ый аз яцкото ой по3 У ой ключен к третьему входу одноразрядного стройство по п. 1, о т л и ч а ющ е е с я тем что блок извлечен я к рня ени" корнЯ группы, !тервый и второй входы разрядов, содержит (% -1) (1с-разрядность вьщод- входа блока извлечения карня подключены ного кода) группу последовагельно соеди а к входам (и -1)-го элемента ИЛИ г иненнь!х одноразрядных сумматоров, групп и - — о элемента групро э Руппу пы, к первыл; входам соответственно персумматорсв по модулю цва гру?пту элемен«вого и вто ого одна аз я ого с мм дополнительных груп?! из (и - т -1) (Где рых соецинены соответственно с выходом ! -номер группы) сумматоров по модулю 3р (»1)» ЯЕдва в каждой группе, генератор единиц " тора единиц по ключ

30 и — -го элемента НЕ группы и генератора единиц, подключенного к перволту !

"Руппу из (t! -2) элементов И, каждая входу третьего одноразрядного сумматора

g -я группа (i =1,2,...,n-l) одно аз ядР э " ° Р Р д» и (и-1)«ой группы, выходы переносов а ора, ных сумматоров соцержит (n +2 -!) оцпервых одноразрядных сумматоров и выноРазРЯдных сУмматоРов, а гРУПпы элт- xott („-1)

) o элемента ИЛИ I p7??ïh! яв ментов HIM, элементов HE и сумматоров ля, тся в ляются выхоцами блока извлечения корня, по модулю два соответственно содерж т а вход каждого элемента И и выход каж(t!-1) и (n -2) элементов, причем выход цого и-го сумматора по модулю два групп, (i +1)-ой группы соединен с первым вхо- 4 у тт . стройство по п. 1, о т л и ч а— дом (g -1)-го одноразряцного сумматора ю щ e e c я т м ю щ е е с я тем, что коммутирующие уз-! ой группы, второй вход первого одно- ль! первой группы содержат два элемента ,РазРЯдного сУмматоРа i -ой гРУппы соеди- 2И»ИЛИ ПР че,, причем первый вход узла соединен с первыми и вторыми входами перво,нен с выходом переноса первого однораз Рядного султматopa (т +1)-oN группыЪпеР- го и второго элементов 2И-ИЛИ, второй выми входами -ых элементов И, ИЛИ и третий входы узла подключены к маторов по модулю цва i «ой цополнитель» му и четвертому входам первого элемента 2И-ИЛИ, четвертый и пятый входы уэной группы, выходы которых соецинены с ла соединены с третьим и четвертым вхо. вторыми входами j -ых(!=2,...,п -т) од» дами второго элемента 2И-ИЛИ, пятый и норазряцньтх сумматоров -ой группы, вто- шестой входы узла подключены к пятым е входы ой (у =2„., n-f -1) сумма- .входам соответственна второго и первоРов по моду пва -Ой до ите ной го элементов 2И-ИЛИ» выходы кoTopbgc группы соединены с выходами переноса являются соответственно вторым и первым первых одноразряцных сумматоров (n -т + выходами коммутирующего .+ 1)-ых групп, выход -го элемента HE

И

5. Устройство по п. 1, о т л и ч а юузла. группы подключены к первому axon (г?+ ш е е с я тем, что в каждой группе

+1 - i )-го одноразрядного сумматора (i =2,3,...,%.) коммутирующие узлы с nei -oN группы, второй вход которого соеди- вого по третий содержат четырехвхоцовый

91 20 элементов 2И-44ЛИ и вторым входом второго элемента 2И-ИЛИ, второй вход

{% +2)-го коммутирующего узла соединен с вторым входом первого эжмента 2ИИЛИ и третьими входами первого и второго элементов 2И- ИЛИ, третий вход (В+

+2)-го коммутирующего узла соединен с четвертым и пятым входами первого элементе 2И ИЛИ, четвертый и пятый входы (Ф +2)-ro коммутирующего узла соединены соответственно с четвертым и пятым входами второго элемента 2И-ИЛИ, выходы первого и второго эжментон 2ИИЛИ яв щотся выходами (1+2)-го коммутирующего узла.

Источники информации, - принятые во внимание щии экспертизе

1. Авторское свидетельство СССР

N 641450, кл. 6 06 F 7/38, 1979.

2. Авторское свидетельство СССР

N 590733, кл. G 06 F 7l38, 1978 (прототип) .

19 9324 элемент 2И-ИЛИ, коммутирующие узлы с четвертого по (Ф +1)-ый содержат .пятивходовый элемент 2И-ИЛИ, (Х +2)-ый коммутирующий узел содержит два эжмента 2И-ИЛИ (в +3)-ый коммутирующий узел содержит элемент И, причем первый и второй входы четырехвходового эжмента 2И-ИЛИ соединены с первым входом j -rо коммутирующего узла (j =1,2,3), второй и третий входы которого соединены 0 с третьим и четвертым входами„четырехвходового элемента 2И-ИЛИ, выход которого являе1ся выходом f< «Го коммутирую» щего узла нервйй вход нятивходового элемента 2И-ИЛИ является первым входом 1<-го 1s коммутирующего узла (j =4,5,...К +1), sòîðîN и третий входы которого соединены соответственно с вторым и четвертым, пятым входами пятивходового элемента 2И-ИЛИ, выход которого является выходом у, -го рэ коммутирующего узла, первый вход (Ф +2)-го коммутирующего узла соединен с первьйчи входами первого и второго (Риг.2