Запоминающее устройство

Иллюстрации

Показать всеРеферат

(72) Автор изобретения

В.В.Реутов

Таганрогский радиотехнический институт им.В.Д.Калмыкова (Vl ) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычисли" тельной технике и может быть использовано при обмене информацией в мно". гопроцессорных вычислительных системах.

Известно многоканальное запомина=

S ющее устройство, представляющее собой многофункциональное запоминающее устройство для многоканального пересчета единичных приращений с пространствен10 ным делением нескольких каналов записи, содержащее ячейки памяти с элементами памяти на ферритовых сердечниках, формирователи сигналов по адресным, разрядным и установочным

15 шинам, усилители считывания, триггеры переноса., которые хранят перед записью поступившие по каналам записи сигналы, схемы управления суммированием во всех ячейках памяти (EQ.

Недостатками этого устройства яв." ляется запоминание информации в виде единичных приращений, что находит сравнительно малое применение и невоз,можность одновременного считывания информации из ячеек запоминающего ус" тройства с различными адресами.

Наиболее близким по технической сущности к предлагаемому являетсязапоминающее устройство, содержащее регистр адреса записи, первые входы которого соединены с адресной шиной, регистр записи числа, первые входы которого соединены с числовой шиной, регистры адреса считывания, первые . входы которых соединены с адресныме шинами, а выходы .- с первыми входами дешифраторов считывания, выходы которых соединены с входами элементов памяти накопителя и первыми входами элементов И-ИЛИ, выходы которых соединены с первыми входами регистров считывания числа, выходы которых соеди-, нены с числовыми шинами, выходы эле-.. ментов памяти соединены с вторыми входами элементов И-ИЛИ, блок управ" ления, первый вход которого соединен с шиной записи, второй — с шиной

932567 считывания, а третий — с шиной синхронизации, первый выход блока управ пения соединен с вторыми входами регистров адреса считывания, второй с вторыми входами регистров считывания числа, третий - с вторыми входами дешифраторов считывания и одними из входов элементов памяти накопителя, четвертый - с другими входами элементов памяти и вторыми входами >р дешифратора записи, пятый - с вторыми входами регистра адреса записи, а шестой - с вторыми входами регистра записи числа (2$.

Однако запоминающее устройство не обеспечивает эффективный обмен между несколькими абонентами из-за поочереДной записи их информации через один вход, что ограничивает быстродействие запоминающего устройства при обмене информацией между несколькими абонентами.

Цель изобретения — повышение быстродействия запоминающего устройства за счет организации независимого обмена между абонентами.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее регистр адреса записи, первые входы которого соединены с адресной шиной, регистр записи числа, первые входы которого соединены с числовой шиной, регистры адреса считывания, первые входы которых соединены с адресными шинами, а выходы - с первыми входами дешифраторов считывания, вы" ходы которых соединены с входами элементов памяти накопителя и первыми входами элементов И-ИЛИ, выходы которых соединены с первыми входами регистров считывания числа, выходы кото 4в рых соединены с числовыми шинами, выходы элементов памяти соединены с вторыми входами элементов И-ИЛИ, блок управления, первый вход которого соединен с шиной записи, второй - 4 с шиной считывания, а третий - с шиной синхронизации, первый выход блока управления соединен с вторыми входами регистров адреса считывания, второй - с вторыми входами регситров считывания числа, третий - с вторыми входами дешифраторов считывания и одним из входов элементов памяти накопителя, четвертый — с другими входами элементов памяти и вторыми входами дешифратора записи, пятый - с вторыми входами регистра адреса записи, а шестой — с вторыми входами регистра записи числа, введены дополнительные регистры адреса записи, дополнительные регистры записи числа и дополнительные дешифраторы записи, причем одни из входов одних из элементов памяти накопителя подключены к выходам соответствующих дешифраторов записи, входы которых соединены с выходами соответсвующих регистров адреса записи, другие входы элементов памяти накопителя подключены к соответствующим выходам дополнительных регистров записи числа, а входы дополнительных регистров адреса записи и дополнительных регистров записи числа подключены к адресным и числоBbIM шинам.

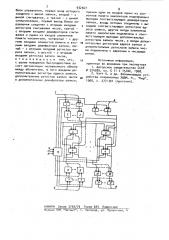

На чертеже представлена структурная схема запоминающего устройства.

Запоминающее устройство содержит регистры 1 адреса записи, первые входы которых соединены с адресными шинами 2, а выходы — с первыми входами дешифраторов 3 записи. Выходы каждо-го дешифратора 3 записи соединены с соответствующими входами элементов памяти накопителя 4, регистры 5 записк числа, первые входы которых соединены с числовой шиной 6. Выходы каждого регистра 5 записи чиспа соединены с входами всех элементов йамяти накопителя 4.Регистры 7 адреса считывания, первые входы которых соединены с адресными шинами 8, а выходы - с первыми входами дешифраторов 9 считывания. Выходы каждого дешифратора 9 считывания соединены с одними из входов всех элементов памяти накопителя 4, а также с первыми входами соответствующих элементов И"ИЛИ 10. Вто-. рые входы каждого элемента И-ИЛИ 10 соединены с выходами каждого элемента памяти 4. Выходы элементов И-ИЛИ

l0 соединены с первыми входами регистров 11 считывания числа, выходы которых соединены с числовыми шинами

12. Блок 13 управления, первый вход которого соединен с шиной 14 записи, второй - с шиной 15 считывания, а третий - с шиной 16 синхронизации.

Первый выход блока 13 управления соединен с вторыми входами регистров 7 адреса считывания, второй — с вторы" ми входами регистров 11 считывания числа, третий — с вторыми входами дешифраторов 9 считывания. и одним из входов элементов памяти накопителя 4, четвертый - с другими входами элемен67 6 налы с выхода дешифраторов 9 считывания поступают только на те входы элементов И-ИЛИ 10, которые соответствуют выбранным элементам памяти накопителя и числовой шине 12 запросившего абонента. По сигналу из блока l3 управления коды чисел .считываются из элементов памяти, проходят через соответствующие элементы И-ИЛИ 10, заносятся в регистры 11 считывания числа ивыдаются по числовым винам 12 запросившим их абонентам. Таким образом, за один цикл записи-считывания происходит обмен информацией всех абонентов. Для обмена информацией в другом соответствии между абонентами необходимо поменять в программе соответствие адресов по записи и по считыванию. Необходимо подчеркнуть, что такая структура запоминающего устройства осуществляет не только попарный обмен абонентов, но и одного абонента с многими абонентами. Для этого к элементу памяти с обменной информацией могут обратиться по считыванию нескольких абонентов одновременно.

При использовании известных запоминающих устройство для обмена информацией между несколькими абонентами возникают очереди на доступ к памяти — нерационально используется машинное время. Основным преимуществом предлагаемого устройства является возможность программно-управляемого обмена информацией между несколькими абонентами одновременно. Таким образом, экономическая эффективность состоит в экономии дорогостоящего машинного времени.

Запоминающее устройство, содержащее регистр адреса записи, первые шиной, регистр записи числа, первые входы которого соединены с числовой шиной, регистры адреса считывания, первые входы которых соединены с адресными шинами, а выходы - с первыми входами дешифраторов считывания, выходы которых соединены с входами элементов памяти накопителя и первыми входами элементов И-ИЛИ, выходы которых соединены с первыми входами регистров считывания числа, выходы ко" торых соединены с числовыми шинами, выходы элементов памяти соединены с вторыии входами элементов И-ИЛИ, 5 9325 тов памяти накопителя 4 и вторыми вхо-. дами дешифраторов 3 записи, пятыйс вторыми входами регистров 1 адреса записи, а шестой - с вторыми входами регистров 5 записи числа. Так как за- s поминающее устройство имеет высокую конструктивную сложность, то изготовление таких устройств стало возмож» ным только с развитием технологии больших интегральных схем. о

Запоминающее устройство работает в трех режимах: обмена, запоминания и смешанном.

Наибольший эффект получается при работе в режиме обмена. Допустим нес- 1 колько абонентов одновременно хотят обменяться информацией. Адресные коды по шине 2 поступают на входы регистров 1 адреса записи, а коды чисел по шине 6 поступают на входы регистров 520 записи числа. По сигналам по шинам 14 и 16 блок 13 управления вырабатывает управляющие сигналы, по которым ! работа происходит в следующей последовательности. Адресные коды зано- 25 сятся в регистры 1 адреса записи, а коды чисел - в регистры 5 записи чис-ла, с выхода которых коды чисел .поступают на соответствующие входы элементов памяти накопителя 4. С выхода щ каждого дешифратора 3 записи.выбирается по одному элементу памяти накопиталя 4, т.е. выходы регистров 5 записи числа подключаются к выходам элементов памяти накопителя 4 в нужном абонентам соответствии по управляющему сигналу коды чисел переписываются в соответствующие элементы памяти накопителя 4. 8 программах абонентов записано, с какими абонентами в данный момент обменивается каждый из формула изобретения них, т.е. в какие элементы памяти не- . обходимо обратиться, чтобы получить нужную информацию. С этой целью по адресным шинам 8 на входы регистров - входы которого соединены с адресной

7 адреса считывания поступают коды адресов. Затем по сигналам по шинам

15 и 16 блок 13 управления вырабатывает управляющие сигналы, по которым работа происходит в следующей последовательности. Адресные коды заносятся в регистры 7 адреса считывания, после чего дешифрируются в дешифраторах 9 считывания. С выхода каждого дешифратора 9 считывания выбирается элемент памяти накопителя 4, в котором находится обмениваемая информация. нужная в данный момент обратившимся абонентам. Кроме того, эти же сиг932567

/ф

ВНИИПИ Заказ 3793/73 Тираж 624 Подписное

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4 блок управления, первый вход которого соединен с шиной записи, второй - с шиной считывания, а третий - с шиной синхронизации, первый выход блока управления соединен с вторыми входами регистров считывания числа, третийс вторыми входами дешифраторов считывания и одним из входов элементов памяти накопителя, четвертый — с дру. гими входами элементов памяти и вто- tO рыми входами дешифратора записи, пя" тый - с вторыми входамй регистра адреса записи, а шестой - с вторыми входами регистра записи числа, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия за счет организации независимого обмена между абонентами, в него введены дополнительные регистры адреса записи, дополнительные регистры записи числа и дополнительные дешифраторы записи, причем одни из входов одних из элементов памяти накопителя подключены к выходам соответствующих дешифраторов записи, входы которых соединены с выходами соответствующих регистров адреса записи, другие входы элементов памяти накопителя подключены к соответствующим выходам дополнительных регистров записи числа, а входы дополнительных регистров адреса записи и дополнительных регистров записи числа подключены к адресным и числовым шинам.

Источники информации, принятые во .внимание при экспертизе

1. Авторское свидетельство CCCP .

N 224589, кл. G 11 С 15/02, 1968.

2. Катт А. и др. Запоминающие устройства современных ЭЦВИ. М,, >t p, 1968, с. 277-301 (прототип).