Цифровой линеаризатор сигналов

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социаиистичесник

Респубиии

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ау (22) Заявлено 21.04.80 (21) 2937863/18-21 с присоединением заявки №вЂ” (23) Приоритет (51)N. Кл.

Н 03 К 13/20

Государетвсииый кеиитет

СССР

Опубликовано 30. 05.82„Бтоллетень ¹ 20 (53) УДК 681 . 325 (088. 8) яо делам изебретеиий и открытий

Дата опубликования описания 30 .05 . 82 (72) Авторы изобретения

В.Г.Зебрев и В.У.Лаптев (7l) Заявитель (54) ЦИФРОВОЙ ЛИНЕАРИЗАТОР СИГНАЛОВ

Изобретение относится к измерительной технике и предназначено для измерения метрологических характеристик (поверки) аналого-цифровых преобразователей (АЦП).

Известен цифровой линеаризатор сиг- з налов, содержащий генератор тактовых импульсов, вентильное устройство,первый вход которого является разрешающим и подключен к выходу генератора тактовых импульсов, а на его второй вход поступает последовательность импульсов, делитель частоты по входусоединенного с выходом вентильного устройства, счетчик импульсов и дешифратор выходом подключенного к входу

15 устройства визуального изображения, предназначенного для считывания результата измерения (1).

Недостатком данного цифрового ли20 неаризатора сигналов является низкая надежность и малое быстродействие..

Цель изобретения - повышение надежности и быстродействия.

Поставленная цель достигается тем, что в цифровой линеаризатор сигналов, содержащий аналого-цифровой преобразователь, первый выход которого соединен с первыми входами десятичного счетчика импульсов, второй выходс первым входом блока синхронизации, выход которого соединен с вторым входом десятичного счетчика импульсов, выход которого соединен с входом блока индикации, дополнительно введены первая и вторая группы эле" ментов И-НЕ, группа элементов НЕ"ИЛИ, дешифратор старших разрядов, дешифратор нуля и двоичный вычитающий счетчик импульсов, первый вход кото" рого соединен с вторым выходом аналого-цифрового преобразователя и пер" выми входами первой и второй rpynn элементов И-НЕ, второй вход - с выходом блока синхронизации, а третий вход - с третьим выходом аналогоцифрового преобразователя, вторыми входами второй группы элементов И-НЕ;

3 93261 и входом дешифратора старших разря-, дов, выходы которого соединены с входами группы элементов НЕ-ИЛИ, выходы которых через первую группу элементов И-НЕ соединены с третьими з входами десятичного счетчика импуль" сов, четвертые входы которого соединены с выходами второй группы weментов И-НЕ, при этом выход двоичного вычитающего счетчика импульсов 10 соединен с входом дешифратора нуля,. выход которого соединен с вторым входом блока синхронизации.

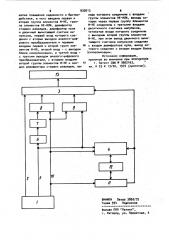

На чертеже представлена блок-схема цифрового линеариэатора сигналов. ls

Цифровой линеаризатор сигналов содержит поверяемый аналого-цифровой преобразователь (АЦП) 1, шину 2 общего сброса, десятичный счетчик 3 импульсов, двоичный вычитающий счетчик

4 импульсов, информационную шину 5, дешифратор 6 старших разрядов, группу элементов И-НЕ 9, шину 10 стробирования, блок 11 синхронизации, дешифратор 12 нуля, блок 13 индикации.

Устройство работает следующим образом.

Предварительно поверяемый АЦП калибруется так, что вес единицы младшего разряда становится кратным 10 при максимальном входном напряжении, После этого вес единицы младшего разряда представляется с помощью двух дополнительных разрядов Несколькими уровнями.

При первоначальном включении и подаче импульса "Сброс" поверяемый АЦП

1, десятичный счетчик 3 импульсов и двоичный вычитающий счетчик 4 импуль40 сов устанавливаются в исходное состояние.

Сигналы кода преобразуемого числа, поступающие по информационной шине

5 стробируются сигналом "Конец преобразования" (строб-импульс), посту45 пающим по шине 10 стробирования, при этом сигналы через элементы 8 первой группы И-НЕ поступают на установочные в единицу входы триггеров десятичного счетчика 3 импульсов, при этом в ® десятичный счетчик 3 импульсов записывается число, равное сумме весов . старших дешифрируемых,разрядов. Значение этого числа определяется дешифратором 6 старших разрядов, с выхода которого в зависимости от комбинации кода старших разрядов преобразуемого числа через соответствующие элементы

3 ф

НЕ"ИЛИ 7 сигналы поступают на первые входы первой группы элементов И-НЕ 8.

Одновременно код первых двух младших разрядов преобразуемого числа поступает на первые входы второй группы элементов И-НЕ 9, а остальные разряды поступают на второй вход двоичноro вычитающего счетчика 4 импульсов.

С занесением кода в двоичный вычитающий счетчик 4 импульсов и с поступлением заднего Фронта сигнала "Конец преобразования" на первый вход блока синхронизации 11 с его выхода тактовые импульсы поступают на первые входы десятичного 3 и двоичного вычитающего 4 счетчиков импульсов, при этом происходит синхронный запуск укаэанных счетчиков ho сигналу "Конец преобразования", причем десятичный счетчик 3 импульсов работает на суммирование, а двоичный вычитающий счетчик 4 импульсов - на вычитание тактовых импульсов.

При появлении нуля на выходе двоичного вычитающего счетчика 4 импульсов, с выхода дешифратора 12 поступит запрещающий сигнал до прихода следующего сигнала "Конец преобразования" по шине 10. На этом заканчивается процесс обработки результата измерения и в десятичном счетчике

3 импульсов запишется число, эквивалентное двоичному коду с выхода поверяемого АЦП 1, а на индикаторах блока 13 индикации отображается результат измерения в единицах измеряемого параметра, т.е. в вольтах.

Ввиду того, что старшие разряды преобразуются параллельно на дешифраторе 6 и не пересчитываются десятичным счетчиком 3 импульсов быстродействие поверки значительно повышается.

Формула изобретения

Цифровой линеаризатор сигналов, содержащий аналого-цифровой преобразоватвль, первый выход которого соединен с первыми входами десятичного счетчика импульсов, второй выход - с первым входом блока синхронизации,: выход которого соединен с вторым входом десятичного счетчика импульсов, выход которого соединен с входом блока индикации, о тл и ч а ю шийся тем, что, с

ЮЮЮ ЮЮЮЮЮФВ

S 9326 целью повышения надежности и быст1зодействия, в него введены первая и вторая rpynna элементов И-kE, группа элементов НЕ-ИЛИ, дешифратор старших разрядов, дешифратор нуля ф и двоичный вычитающий счетчик импульсов, первый вход которого соединен с втерым выходом аналого-циф" рового преобразователя и первыми входами первой и второй групп эле- 1а, ментов И-НЕ, второй вход — с выходом блока синхронизации, а третий входс третьим выходом аналого-цифрового

Преобразователя, с вторыми входами второй группы элементов И-НЕ и вхо- И дом дешифратора старших разрядов, вы13 6 ходы которого соединены с входами группы элементов НЕ-ИЛИ, выходы которых через первую группу элементов

И-HE соединены с третьими входами десятичного счетчика импульсов, четвертые входы которого соединены с выходами второй группы элементов

И-НЕ, при этом выход двоичного вычи", тающего счетчика импульсов соединен с входом дешифратора нуля, выход которого соединен с вторым входом блока (синхронизации.

Источники информации принятые во внимание при экспертизе

1. Патент США и 3662163, кл. Н 03 К 13/20, 1972 (прототип);

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4