Коммутирующее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Респубпии

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

<> i>932615 ($I j Дополнительное к авт. саид-ву (5l ) M Кл. (И) Заявлено 01.10.80 (21) 2989396/18-21 с присоединением заявки М

Н 0.3 К 17/00

1осударстееииый комитет (23) Приоритет по делам изобретений н OTI{phlTNN

<опубликовано 30. 05. 82. Ьтоллетень М 20

Дата опубликования описания 30 .05 . 82 (53) УДК 681.32 (088. 8) (72) Автор изобретения

В.А. Авдеев (71) Заявитель

Таганрогский радиотехнический институт им. В.Д. Калмыкова (54) КОММУТИРУНЗЦЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и коммутационной технике.

Известны коммутирующие устройства, содержащие матричный коммутатор, счетчик, дешифратор, блоки памяти, регистры. (1).

Недостаток известного устройстванизкая надежность функционирования.

Наиболее близким к предлагаемому по технической сущности является комто мутирующее устройство, содержащее матричный коммутатор, выходы которого соединены с выходными шинами, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора адресов выходных шин, входы которого соединены с информационными входами одноименного блока памяти и выходами одноименного регистра, первая и вторая группы .информационных входов которого подключены соответственно к первой группе адресных шин и выходам соответствующего . блока памяти, а управляющий вход соединен с одноименной основной управляющей шиной, при этом вторая группа адресных шин подключена к разрядным входам основного счетчика, счетный вход которого соединен с дополнительной управляющей шиной, а выходы через дешифратор адресов блоков fiaмяти — с адресными входами блоков памя ти (21, К недостатку известного устройства относится низкая надежность функционирования.

Цель изобретения — повышение надежности коммутирующего устройства.

Указанная цель достигается тем, что в коммутирующее устройство, содержащее матричный коммутатор, выходы которого соецинены с выходными шинами, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора адресов выходных шин, входы которого соединены с информационными входами одноименно"

rn блока памяти и выходами одноимен93261 ного регистра, первая и вторая группы информационных входов которого подключены соответственно к первой группе адресных шин и выходам соответствующего блока памяти, а управляющий вход соединен с одноименной основной управляющей шиной, при этом вторая группа адресных шин подключена к разрядным входам основного счетчика, счетный вход которого соединен 10 с дополнительной управляющей шиной, а.выходы через дешифратор адресов блоков памяти - с адресными входа>ми блоков памяти, введены дополнительные счетчики, дешифраторы адре- 1$ сов входных ший и линейные коммутаторы, информационные входы которых соединены с информационными входными шина» ми, выходы - с информационными входами ма тричного коммутатора, а упра вляющие входы каждого из них подключены к выходам соответствующегодешифратора адресов информационных входных шин, входы каждого из которых подключены к выходам одноименного дополнительного счетчика, счетный вход которого соединен с выходом дополнительного разряда одноименного регистра, разрядные входы - с третьей группой адресных шин, а управляющий вход подключен к соответствующей шине дополнительной группы °

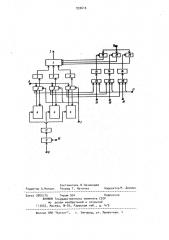

На чертеже приведена блок-схема коммутирующего устройства.

Устройство содержит матричный ком- 3$ мутатор 1., выходы которого соединены с выходными шинами 2, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора 3 адресов выходных шин 2, входы которо- го соединены с информационными входами одноименного блока 4 памяти и выходами одноименного регистра 5, первая и вторая группы информационных входов которого подключены соответственно к группе адресных шин 6 и выходам соответствующего блока 4 памяти, а управляющий вход соединен с одноименной управляющей шиной .7; группа адресных шин 8 подключена к $0 разрядным входам счетчика 9, счетный вход которого соединен с управляющей шиной 10, а выходы через дешифратор 11 адресов блоков 4 памяти с адресными входами блоков 4 памяти; $$ линейные коммутаторы 12, информациI онные входы которых соединены с информационными входными шинами 13,вы5 4 ходы - с информационными входами матричного коммутатора 1, а управляющие входы каждого из них подключены к выходам соответствующего дешифратора

14 адресов информационных входных шин 13, входы каждого из которых подключены к выходам одноименного .счетчика 15, счетный вход которого соединен с выходом дополнительного разряда одноименного регистра 5, разрядные входы — с группой адресных шин

16, а управляющий вход подключен к соответствующей управляющей шине 17 дополнительной группы.

Коммутирующее устройство функционирует следующим образом.

Перед началом работы в блоках 4 памяти через адресные шины 6 и регистры, 5 осуществляется ввод программы коммутации, состоящей из адресов выходных шин 2. Каждая ячейка блока 4

1памяти содержит в коде адреса выходных шин 2 дополнительный разряд. Адресация ячеек блоков 4 памяти производится с помощью дешифратора 11 и счетчика 9, в который или предварительно вводится адрес через адресные шины

8, или увеличивается значение счетчика 9 на единицу сигналом, подаваемым по управляющей шине 10. В счетчики 15 вводятся через адресные шины 16 начальные коды адресов информационных входных шин 13, а в счетчик 9 засылается начальный код адреса ячеек блоков 4 памяти.

Затем по сигналу управления производится одновременное считывание адресов выходных шин 2 из ячеек блоков 4 памяти, соответствующих адресу счетчика 9, и осуществляется подключение тех информационных входных шин 13 через линейные коммутаторы 12 к матричному коммутатору адреса которых хранятся в счетчиках 15. Считанные коды адресов выходных шин 2 поступают в регистры 5 и через дешифраторы 3 управляют подключением выходов линейных коммутаторов 12 с помощью матричного коммутатора 1 к требуемым выходным шинам

2. Если дополнительный разряд кода адреса выходных шин 2, хранящийся в регистре 5, равен нулю, то код адреса в счетчике 15 ; если дополнительный разряд равен единице, то к началу считывания адресов выходных шин 2 следующих ячеек блоков

9326

4 памяти код адреса в счетчике 15 увеличивается на единицу.

Таким образом, введение дополнительных счетчиков, дешифраторов и линейных коммутаторов позволяет повысить надежность предлагаемого коммутирующего устройства по сравнению с известным.

Формула изобретения

Коммутирующее устройство, содержащее матричный коммутатор, выходы которого соединены с выходными шинами, а каждая группа управляющих входов подключена к выходам соответствующего дешифратора адресов выходных шин,входы которого соединены с информационными входами одноименного блока памя- 2в ти и выходами одноименного регистра, первая и вторая группы информационных входов которого подключены соответственно к первой группе адресных шин и

;выходам соответствующего блока памя- 25 ,1ги, а управляющий вход соединен с одноименной основной управляющей шиной, при этом вторая группа адресных шин подключена к разрядным входам основного счетчика, счетный вход кото- зо рого соединен с дополнительной уп15 6

-равляющеи шиной, а выходы через дешифратор адресов блоков памяти - с адресными входами блоков памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, в него введены дополнительные счетчики, дешифраторы адресов входных шин и линейные коммутаторы, информационные входы которых соединены с информационными входными шинами, выходы " с информационными входами матричного коммутатора, а управляющие входы каждого из них подключены к выходам соответствующего дешифратора адресов информационных входных шин, входы каждого из которых подключены к выходам одноименного дополнительного счетчика, счетный вход которого соединен с вы" ходом дополнительного разряда одноименного регистра, разрядные входыс третьей группой адресных шин, а управляющий вход подключен к соответствующей управляющей шине дополнительной группы.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании У 1392176, кл. С 4 А, 1975.

2. Авторское свидетельство СССР по заявке и 2822786,кл.Н 03 К 17/04, 1980 (прототип).

Составитель В.Чачанидзе

Редактор А.Мотыль Техред T. Наточка Корректор М. Демчи к

------------- т----------Заказ 3800/75 Тираж 954 Подписное .ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4