Способ контроля канала связи и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<1ц932625 (61) Дополнительное к авт. свид-ву (22) Заявлено 06.08.79 (21) 2807093/18-09 с присоединением заявки М— (23) Приоритет— (51)М. Кл.

Н 04 В 3/46/l . Н 04 В 1/10 фЬвударатваккый камнтет

СССР ва делам каабретекяй н еткрмтнй

Опубликовано 30.05 82. Бюллетень М 20

Дата опубликования описания 30.05.82 (53) УД е(621.395. .664:621.391. .82 (088.8) (72) Авторы изобретения

Ю. С. Козленков, Л. И. Мартынов и В, Г. Чугьщ

I »

1

Г i ."1

4, ф

1 (7l) Заявитель (54) СПОСОБ КОНТРОЛЯ КАНАЛА СВЯЗИ И УСТРОЙСТВО

ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

Изобретение относится к измерительной технике и может использоваться при построении автоматических гидролокационных, радиолокационных, радиотехнических и другого рода, информационных и измерительных сиS стем, а также в вычислительной технике при разработке и построении специализированных корректирующих устройств.

Известен способ контроля канала связи, включающий формирование ожидаемого значения сигнала, формирование границ зоны допуска ожидаемого значения сигнала, формирование допустимых значений принимаемого сигнала, сравнение их со значением принятого сигнала и при совпадении или несовпадении значения принятого сигнала с формированными допустимыми значениями, запоминание значения принятого сигнала соответственно как достоверного или недостоверного (1) .

Однако известный способ не обеспечивает контроля канала связи при передаче безызбыточной информации с коррекцией ошибки.

Известно также устройство для осуществления способа, содержащее регистр и последовательно соединенные экстраполятор и блок сравнения (2).

Цель изобретения — обеспечение контроля канала связи при передаче безызбыточной информации с коррекцией ошибки.

Поставленная цель достигается тем, что согласно способу контроля канала связи, включающем формирование ожидаемого значения сигнала, формирование границ зоны допуска ожидаемого значения сигнала, формирование допустимых значений принимаемого сигнала, сравнение их со значением принятого сигнала . и при совпадении или несовпадении значения принятого сигнала со сформированными допустимыми значениями, запоминание значения принятого сигнала соответственно, как достоверного нли недостоверного, формирование границ зоны допуска ожидаемого значения сигнала осуществляют путем сравнения значения принятого сигнала со сформированным ожидаемым значением сигнала и уменьшения величины раэностного сигнала пропорционально величине предыдущего достоверного зиачщ@я сигнала, а в последовательности приня3 932625 тых сигналов вместо запомненных недостоверных значений сигнала формируют соответствующие им ожидаемые значения сигналов, причем каждое формируют путем изменения К последовательных предьщущих достоверных значений сигнала пропорционально,.соответствующим коэффициентам экстраполяции . и

I суммирования с учетом знаков коэффициентов экстраполяции, определяемых по формуле:

M(,K,1) = д ((К" 1)(К+Ъ)-1(4g+7)itiOi ) 15 где i =1,2,3, ...,К,причем К 3.

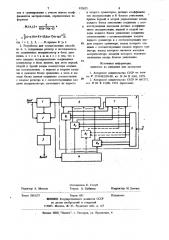

А в устройство для осуществления способа, содержащее регистр и последовательно соединенные экстраполятор и блок сравнения, вве- щ дены последовательно соединенные коммутатор и блок памяти, при этом первый, второй и третий входы коммутатора соединены соответственно с первым и вторым входами и выходом блока сравнения, а вход и выхо- 25 ды блока памяти соединены соответственно с входом регистра и с соответствующими входами экстраполятора, состоящего из первого и второго сумматоров, датчика коэффициентов экстраполяции и К блоков умножения, причем первый и второй управляющие входы каждого блока умножения соединены с соответствующими выходами датчика коэффициентов экстраполяции, первый и второй выходы каждого блока умножения соединены соответственно с соответствующим входом первого сумматора и с соответствующим входом второго сумматора, выход которого соединен с соответствующим входом первого сумматора, выход которого является выходом экстрапо10 лятора, входами которого являются сигнальные входы блоков умножения.

На чертеже представлена структурная электрическая схема устройства, реализующего предлагаемый способ.

Устройство содержит блок 1 сравнения, коммутатор 2, регистр 3, блок 4 памяти, экстраполятор 5, состоящий из первого и второго сумматоров 6 и 7 соответственно, К

50 блоков умножения 8,— 8к и датчик 9 коэффициентов экстраполяции.

Устройство работает следующим образом.

Входной сигнал Uu (ti) поступает одновременно на сигнальные входы блока 1 сравнения и коммутатора 2, на вторые сигнальные входы блока сравнения и коммутатора 2, с выхода экстраполятора 5 поступает экстраO

4 полированное (ожидаемое) значение входного сигнала Оэ(т;), вычисленное по формуле

1),H,„.)=N„g 08„)а--1 1=1 где К вЂ” количество точек, по которым осуществляется экстраполяция.

Ъ(К+2) (К+3 )

1 К(К-1) (К-2)

6 (4к+7)

К(К-1) (К-2.)

М = ) I

U(tI) — хранящиеся в блоке памяти К значения входного сигнала, принятые за достоверные.

На каждом такте работы устройства в блоке 1 сравнения осуществляется анализ сигналов Uu(ti) и U3(ti) и вычисляется относительная погрешность расхождения б (ti) по формуле и ) !Ом(Ь ) О 1 I

v (4j) () (+ ) I (2) где Uu(ti) — дискретное значение входного сигнала на i-от такте работы устройства, Ua(ti) — ожидаемое значение входного сигнала, вычисленное по формуле (1), О (t i ) — дискретное значение входного сигнала на предыдущем i 1-от такте работы устройства, которая сравнивается с заданной допустимой погрешностью и в зависимости от результата сравнения на выходе блока 1 сравнения вырабатывается.сигнал управления первого или второго рода и в соответствии с этим предусмотрены два режима работы устройства.

Первый режим работы устройства характеризуется соотношением

h(ti) (Ь, (3) которое показывает, что входной сигнал

Uu(ti) достоверен, т.е. не содержит искажений и сбоев, превышающих допустимый уровень. В этом случае на выходе блока 1 сравнения вырабатывается управляющий сигнал первого рода, который поступает на управляющий вход коммутатора 2, вызывая блокировку его второго входа и передачу входного сигнала Uu(t;) с входа устройства через первый вход коммутатора 2 на его выход.

При этом сигнал U(ti) на выходе коммутатора 2 принимают равным входному сигналу, = Uu(ti).

Таким образом, положительный эффект от использования предлагаемого изобретения состоит в том, что обработка входных сигналов осуществляется оперативно, в реальном масштабе времени, причем исправление аномальных сигналов осуществляется путем замены их наиболее вероятными достоверными значениями, полученными на основе анализа ранее поступивших достоверных значений сигналов; оперативная обработка текущих значений сигналов в реальном масштабе времени позволяет отказаться от накопления и хранения больших массивов информации, поступающей в процессе проведения измерений или наблюдений, и тем самым существенно сократить емкость оперативной памяти, упростить конструкцию блока памяти, и, как следствие этого, снизить его стоимость; автоматическое выявление и исправление аномальных значений входных сигналов, на основе использования информации. содержашейся в самих поступаюших значениях сигналов, позволяет отказаться от привлечения априорной ампирической информации о характере и физических параметрах поступающих сигналов и тем самым повысить. точность получаемых конеЧных результатов. юший формирование ожидаемого значения сигнала, формирование границ зоны допуска ожидаемого значения сигнала, формирование.допустимых значений принимаемого сигнала, сравнение их со значением принятого сигнала и при совпадении или несовпадении значения принятого сигнала со сформированными допустимыми значениями, запоминание значения принятого сигнала соответственно как достоверного или недостоверного, о т л и ч а юш и и с я тем, что, с целью обеспечения контроля канала связи при передаче безызбыточной информации с коррекцией ошибки, формирование границ зоны допуска ожидаемого .значения сигнала осуществляют путем сравнения значения принятого сигнала со сформированным ожидаемым значением сигнала и уменьшения величины разностного сигнала пропорционально величине предыдущего достоверного значения сигнала, а в последовательности принятых сигналов вместо запомненных недостоверных значений сигнала формируют соответствуюшие им ожидаемые значения сигналов, причем каждое формируют путем изменения К последовательных предыдуших достоверных значений сигнала пропорционально соответствующим коэффициентам экстраполя-.

5 932625

Второй режим работы устройства характеризуется соотношением

5(t)) ) Л, (4) которое показывает, что входной сигнал

Ug(t ),ложен, т.е. содержит аномальное отклонение или сбой, превышающий допустимый уровень. В этом случае на выходе блока 1 сравнения вырабатывается управляющий сигнал второго рода, который поступает на управляющий вход коммутатора 2, вызывая блокировку его первого входа и передачу сигнала

U>(t ) с выхода экстрополятора 5 через второй вход коммутатора 2 на его выход. При этом сигнал 0(т ) на выходе коммутатора 2 принимают равным сигналу на выходе экстраполятора 5.

Как в первом, так и во втором режимах работы устройства сигнал 0{1 ) с выхода коммутатора 2 поступает на входы блока 4 памяти и регистра 3. 20

На каждом такте работы устройства, т.е. с приходом каждого очередного значения сиг- нала 0(т ) с выхода коммутатора 2 на вход блока 4 памяти, в нем происходит сдвиг ранее поступившей информации на одно сло- 25 во и занесение в память на освободившееся место вновь поступившего сигнала U(t;).

Причем, сдвиг ранее поступившей информации в блоке 4 памяти осуществляется таким образом. что в памяти сохраняется только упоря- 30 доченная по времени поступления группа из

К соседних дискретных значений сигналов

U(t;), 0(t; <), U(t;z) 0(; K+ ) поступивших с выхода коммутатора 2, при этом самое раннее значение сигнала, поступившее на i-к-ом такте работы устройства, аннулируется.

Таким образом, на каждом такте .работы устройства в блоке 4 памяти хранится постоянно обновляющаяся группа из К достоверных значений входного сигнала, которые затем с выхода блока 4 памяти поступают на вход экстрапопятора 5, где на их основе вы. числяется по формуле (1) следующее ожидаемое значение входного сигнала 0 (t +g).

На следуюшем такте работы устройства ожидаемое значение входного сигнала Оэ(1 +4 ) с выхода экстраполятора 5 поступает на второй вход блока 1 сравнения, одновременно на его первый вход поступает очередное значение входного сигнала 0„(t;+q )., которое

50 сравнивается с сигналом 0э(т;+ ) и цикл работы устройства повторяется в соответствии с приведенным выше описанием.

Таким образом, на вход регистра 3 на каж55 дом такте работы устройства поступает откорректированная входная информация, которая преобразуется регистром 3 и в заданном виде передается на выход устройства.

Формула изобретения

1. Способ контроля канала связи, включаСоставитель E. Голуб

Техред А. Бабинец

Редактор А. Мотыль

Корректор М. Демчик

Заказ 3801/75 Тираж 685

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

ram и суммирования с учетом знаков коэффициентов экстраполяции, определяемых по формуле х ((K+1)(k+5)-2(4ksl)i+10i 1t где i 1, 2, 3, ..., К, причем К 3.

2. Устройство для осуществления способа по п. 1, содержащее регистр и последовательно соединенные экстраполятор и блок cpasпения, о т л и ч а ю щ е е с я тем, что в него введены последовательно соединенные коммутатор и блок памяти, при этом первый, второй и третий входы коммутатора соединены соответственно с первым и вторым входами и выходом блока сравнения, а вход и выходы блока памяти саед иены соответственно с входом регистра и с соответствующими входами экстраполятора, состоящего из первого

32625 8 и второго сумматоров, датчика коэффициентов экстраполяции и К блоков умножения, I причем первый и второй управляющие входы каждого блока умножения соединены с соответствующими выходами датчика коэффициентов экстраполяции, первый и второй выходы каждого блока умножения соединены соответственно с соответствующим входом первого сумматора и с соответствующим вхо-!

О дом второго сумматора, выход которого соединен с соответствующим входом первого сумматора, выход которого является выходом экстраполятора, входами которого являются сигнальные входы блоков умножения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 0 заявке Р 2733462/18-09, кл. Н 04 В 3/46, 1979.

2. Авторское свидетельство СССР No 495777, кл. Н 04 В 15/00, 1974 (прототип).