Устройство для приема частотно-манипулированных сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

asxo cxОaaV С ) д л С

Союз Советсмик

Социалистическик

Республик и>932646 (6l ) Дополнительное к авт. свмд-ву (22) Заявлено 18. 11. 80 (2l ) 3007124/18-09 с присоединением заявки,% (23) ПриоритетОпублмковано 30.05.82 Бюллетень № 20 (51)М. К.п.

Н 04 L 27/14 фмударстинныЯ комитет

СССР пе делам нзабретеннй и рткрытнЯ (53) УДК 621.376,. .52(08&. 8) Дата опубликования описания 30.05.82

А.Л.Сартаков, Г.И.Титов и (72) Авторы изобретения (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ЧАСТОТНОИАНИПУЛИРОВАННЫХ СИГНАЛОВ

Изобретение относится к технике

1передачи дискретных сообщений по проводам и радиоканалам преимущественно На низкой несущей или поднесущей частоте.

Известно устройство для приема частотно-манипулированных сигналов, содержащее блок формирования синхронных сигналов и демодулятор, в котором для исключения "обратной работы" использована начальная установка фазы синхронных сигналов 5 1).

Однако необходимость начальной установки фазы существенно ограничивает возможные области применения устройства.

Наиболее близким к предлагаемому по технической сущности является устройство для приема частотно-манипулированных сигналов, содержащее детектор, первый вход которого соединен с выходом первого интегратора, к первому входу которого подключен выход перемножителя, первый вход ко.торого соединен с выходом усилителя ограничителя и входом удвоителя час. тоты, выход которого через блок фазовой автоподстройки частоты подключен к входу делителя частоты, выход которого соединен с входом формирователя импульсов (2 3.

Однако это устройство имеет низкую помехоустойчивость.

Цель изобретения - повышение по10 мехоустойчивости.

Указанная цель достигается тем, что в устройство для приема частотно-манипулированных сигналов, содержа"

15 щее детектор, первый вход которого соединен с выходом первого интегратора, к первому входу которого подключен выход перемножителя, первый вход которого соединен с выходом усилителя-ограничителя и с вхадрм удвоителя частоты, выход которого через блок фазовой автоподстройки частоты подключен к входу делителя частоты, выход которого соединен с входом форми.

3 93264 рователя импульсов, введены счетчи-! ки, ключи, второй интегратор „блок памяти и коммутатор, первый вход которого. соединен с первым входом первого ключа, с первым входом первого счетчика и с первым выходом формирователя импульсов, второй выход которого соединен с первым входом второго счетчика, с первым входом второго ключа и с вторым входом ком- о мутатора, к третьему входу которого подключен выход блока памяти, входы которого соединены с выходами второго интегратора, к входам которого подключены выходы первого и второго ключей, вторые входы которых соединены соответственно с выходами первого и второго счетчиков, вторые входы которых соединены с выходом усилителя-ограничителя, причем выход коммутатора подключен к вторым входам перемножителя, первого интегратора и детектора.

Ъ

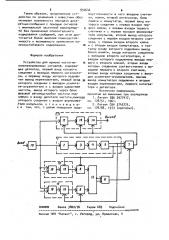

На чертеже представлена структурная схема предложенного устройства.

Устройство для приема частотно-манипулированных сигналов содержит блок 1 формирования синхронных сигналов, состоящий из удвоителя 2 частоты, блока 3 фазовой автоподстройки частоты, делителя 4 частоты и формирователя 5 импульсов, блок 6 памяти, коммутатор 7, два ключа 8 и 9, усилитель-ограничитель 10, демодуеятор ll, состоящий из перемножителя 12, первого интегратора 13 и дет ек- тора 14, второй интегратор 15, первый и второй счетчики 16 и 17, каждый из которых состоит из элемента И 18 и двоичного счетчика 19.

Уст роист во работает следующим

40 образом.

Принимаемый сигнал с минимальной частотной манипуляцией через усилитель-ограничитель 10 поступает на входы перемножителя 12, удвоителя 2 частоты и на первые входы элементов И 18 первого и второго счетчиков 16 и 17. Блок 3 фазовой автоподстройки частоты работает на удвоенной верхней характеристической частоте.

На выходе делителя 4 частоты на два сигнала верхней характеристической частоты, равной тактовой частоте сигнала, имеет неопределенность фазы

180 C. С выхода формирователя 5 два установочных импульсных сигнала с альтернативными значениями фазы поступают на установочные входы соот ветствующих двоичных счетчиков 19 и импульсные входы обоих ключей 8 и

Предположим, что установочный импульсный сигнал поступает на двоичный счетчик 19 первого счетчика 16 и ключ 8, а другой сигнал " на двоимный счетчик второго счетчика 17 и ключ 9. Очередной установочный импульс устанавливает двоичные. счетчики 19 в состояние, определяемое логической единицей на выходе предпоследнего разряда и логическими нулями на выходах остальных m-1 разрядов. На второй вход соответствующего элемента И поступают счетные импульсы, частота следования которых в 2 m раза выше тактовой частоты сигнала. Поскольку на первый вход элемента И поступают импульсы принимаемого сигнала, то при положительной его полярности счетные импульсы проходят на двоичные счетчики 19, а при отрицательной - не проходят.

Таким образом, к моменту прихода очередного установочного импульса сигнал на выходе последнего разряда двоичного счетчика 19 определяется разностью временных интервалов поло жительной и отрицательной полярности принимаемого сигнала от момента. поступления предыдущего установочного импульса. Если эта разность превышает половину тактового интервала, что выполняется для некоторых тактовых интервалов в двоичном счетчике 19 второго счетчика 17, то на выходе последнего разряда двоичного счетчика формируется сигнал, разрешающий прохождение через соответствующий ключ (в нашем случае ключ =9) очередного установочного импульса.

После статистического усреднения во втором интеграторе 15 происходит установка блока 6 памяти в состояние, определяющее коммутацию на выход коммутатора 7 синхронных сигналов с правильным значением фазы. В качестве перемножителя 12 может быть использован логический элемент "исключающее ИЛИ". Интегрирование результата перемножения производится на интервале от минус 0,5 Т до 0,3 Т, где Тдлительность тактового интервала.

В конце периода интегрирования производится опрос первого интегратоРа 13 детектором 14 знака с памятью ,и разряд первого интегратора 13.

Таким образом, предложенное устройство по сравнению с известным обес ,печивает возможность передачи диск:ретных сообщений с помощью сигналов с минимальной частотной манипуляцией беэ применения относительного кодировайия сообщений, при этом достигается более высокая помехоустойчивость и возможность применения помехоу стой чи во го кодир о ва ни я. формула изобретения

Устройство для приема частотно- 15 манипулированных сигналов, содержащее детектор, первый вход которого соединен с выходом первого интегратора, к первому входу которого подключен выход перемножителя, первый вход щ которого соединен с выходом усилителя-ограничителя и с входом удвоителя частоты, выход которого через блок фаэовой автоподстройки частоты подключен к входу делителя частоты,выход2з которого соединен с входом формирова,. теля импульсов, о т л и ч а ю щ е е ) с я тем, что, с целью повышения поме932646 б ! хоустойчивости в него введены счетчики, ключи, B торой интегратор, блок памяти и коммутатор, первый вход которого соединен с первым входом перз вого ключа, с первым входом первого счетчика и с первым выходом формирователя импульсов, второй выход которого соединен с первым входом второго счетчика, с первым входом второго ключа

30 и с вторым входом коммутатора, к третьему входу которого подключен выход блока памяти, входы которого соединены с выходами второго интегратора, к входам которого подключены выходы первого и второго ключей, вторые входы которых соедИнены соответственно с выходами первого и второго счетчика, вторые входы которых соединены с выхо дом усилителя-ограничителя, причем выход коммутатора подключен к вторым входам перемножителя, nepaoro интегратора и детектора.

Источники информации, принятые во внимание при экспертизе

1. Патент CQA 2977417, кл. 178/51, 1961 °

2. Патент США 3743775, кл . 178/88, 1973 (прототип) .

ВНИИПИ Заказ 3802/76 Тираж 685 Подписное еае е е ав а ав

Ф Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 г