Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических республик ()934468 (6l ) Дополнительное к авт. саид-ву (22) Заявлено 26.06.80 (2I ) 2947021/18-24 с присоединением заявки № (23 ) II рмори тет (5I)M. Кл.

С 06 F 7/02

1ввудлрствопвй кшммтвт

СОСО

llo 4NI35I мзобретеммм м отхритмй (53) УЛК 681.,325 (088.8) ОпУбликовано 07.06.82 Бюллетень ¹

Дата опубликования описания 07.06.82. (72) Автор . изобретения

А.И.Ферберов

) ф п,б ф

Харьковский фйлиал Всесоюзного научно-исслеловахел алвдиа института литейного машиностроения, литещудц, технологии и автоматизации литейного производства (7I ) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ

ЧИСЕЛ

Изобретение относится к автоматике и вычислительной технике и мажет быть использовано при реализации технических средств цифровой аппаратуры, в частности в испытательных машинах для определения предела прочности материалов.

Известно устройство для сравни« вания, содержащее два двоичных счетчика, элемент равнозначности, одноразрядный сумматор, два триггера, элемент НЕ и шесть элементов И (I), Недостатки данного устройствасложность согласования с внешними устройствами, вызванная запоминани« ем экстремального числа в заранее не определенном счетчике, что предопределяет наличке дополнительных логических элементов для считывания числа, и сложность схемы, вызванная большим каяичеством элементов, ши« рокая номенклатура которых накладывает ограничения на элементную базу при практическом конструировании устройства.

Наиболее близким к предлагаемому является устройство для сравнивания двоичных чисел, содержащее суммирующий двоичный счетчик, вычитающий двоичный счетчик, триггер, группу элементов И, элементы И, ИЛИ и НЕ, причем информационный вхсд устройства соединен с первыми входами первого и второго элементов И и входом установки в нулевое состояние триггера, выход первого элемента И под-ключен к информационному входу суммирукхцего двоичного счетчика, выходы разрядов которого соединены с первыми входами группы элементов И, вторые входы которых подключены к единичному выходу триггера, а выхо " ды - к установочным входам вычитаюшего двоичного счетчика, информаци" онный вход которого соединен с выхо" дом второго элемента И, а выход разрядов - со входами элемента ИЛИ, %

93446

3S выход которого. подключен ко второму входу второго элемента И и через элемент НŠ— ко второму входу первого элемента И, управляющий вход устройства подключен ко входу установки в единичное состояние триггера и ко входу установки в нулевое состояние вычитающего двоичного счетчика 2).

Недостатком известного устрой- 1п ства является трудность его практической реализации, поскольку вычитающие двоичные счетчики отсутствуют в номенклатуре серийно изготовляемых функциональных узлов. Изготовление вычитающего двоичного счетчика из отдельных триггеров или использование в качестве него реверсивного счетчика, работающего в вычитающем режиме, ведет к увеличению стоимости устройства, причем во втором случае.накладывается дополнительное ограничение по использованию элементной базы.

Целью изобретения является упрощени . устройства за счет применения унифицированных элементов

Поставленная цель достигается тем, что в устройство для сравнения двоичных чисел, содержащее суммирующий двоичный счетчик, триггер, элементы И, элемент НЕ, причем информационный вход устройства соединен со входом установки в нулевое состояние триггера и первыми входами первого и второго элементов И, второй вход первого элемента И соединен с выходом третьего элемента

И, второй вход второго элемента Ис выходом третьего элемента И через элемент НЕ, выход первого элемента

И соединен с информационным входом суммирующего двоичного счетчика, а управляющий вход устройства соединен со входом установки в единичное состояние триггера, введены второй суммирующий двоичный счетчик и группа элементов ИЛИ-НЕ, первые входы которых соединены с нулевым выходом триггера, вторые входы — c выходами разрядов первого суммирующего двоичного счетчика соответственно, а выходы — с установочылми входами второго суммирующего двоичного счетчика, выходы разрядов которого соединени со входами третьего элемента И, а вход установки в нулевое состояние соединен с управляющим входом устройства.

8 ф

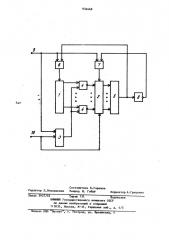

На чертеже представлена блок-схема устройства.

Устройство содержит сую ирующие двоичные счетчики 1 и 2, триггер 3, группу элементов ИЛИ-НЕ 4, элементы

И 5-7, элемент НЕ 8, информационный вход 9 и управляющий вход 10.

Предлагаемое устройство работает следующим образом, В исходном состоянии суммирующий двоичный счетчик 1 и счетный триггер

3 находятся в нулевом состоянии.

Тактирующий импульс, поступив на управляющий вход 10, своим передним фронтом устанавливает в нулевое состояние суммирующий двоичный счетчик 2. Задний фронт тактирующего импульса, воздействуя на вход установки триггера в единичное состояние, перебрасывает триггер 3 в единичное состояние. Нулевой сигнал нулевого выхода триггера 3, соединенного с первыми входами элемента ИЛИ-НЕ, разрешает перезапись числа из суммирук щего двоичного счетчика в суммирующий двоичный счетчик 2, Назначение суммирующего двоичного счетчика

2 состоит в вычитании из числа, поступающего D число-импульсном коде на вход 9, количества импульсов, равного числу, записываемому в суммирующем двоичном счетчике 1. Контроль переполнения суммирующего двоичного счетчика 2 по появлении во всех его разрядах "1" в сочетании с перезаписью вычитаемого числа из суммирующего двоичного счетчика в суммирующий двоичный счетчик 2 в обратном коде адекватен представлению вычитаемого, поступающего в сумматор, слагаемому в дополнительном коде.

Действительно, будучи записанным

0 в обратном коде, число "0" устанавливает во всех разрядах суммирующего двоичного счетчика 2 "1". Элемент И 5, контролирующий состояние суммирующего двоичного счетчика 2, своим единичным выходным сигналом разрешает прохождение импульсов первого числа через элемент И 6, а элемент НЕ 8 запрещает их прохождение через элемент И 7.

Первый импульс первого числа, по" ступающего на информационный вход

9, соединенный со входом установки в нулевое состояние триггера 3, своим передним фронтом устанавлива-, ет триггер 3 в нулевое состояние. формула изобретения

5 9344

Первое число полностью записывается в суммирующем двоичном счетчике 1

Тактирующий импульс, поступающий на управляющий вход 10 перед поступлением второго числа, устанавливает в нулевое состояние суммирующий двоичный счетчик 2, а затем— в единичное состояние триггер 3.

Первое число из суммирующего двоичного счетчика I переписывается 1О в обратном коде в суммирующий двоичный счетчик 2. Единичный сигнал с выхода элемента НЕ 8 разрешает прохождение импульсов второго числа через элемент И 7, а нулевой сигнал с выхода элемента И 5 закрывает элемент И 6.

Если второе число больше первого, после поступления на суммирующий двоичный счетчик 2 количества импульсов, равного первому числу, во всех. разрядах суммирующего двоичного счетчика 2 записываются "1".

Это фиксируется элементом И 5, который теперь разрешает прохождение входных импульсов на суммирующий двоичный счетчик 1 и через элемент

HE 8 запрещает их поступление на суммирующий двоичный счетчик 2.

Восприняв количество импульсов, равное разности между вторым и первым числами, суммирующий двоичный счетчик 1 запоминает второе число.

Если третье число меньше второго., суммирующий двоичный счетчик

3$

2, воспринимая поступающие на него импульсы, не сможет записать во всех разрядах "1" и следовательно, импульсы не смогут попасть на вход суммирующего двоичного счетчика 1.

Таким образом, из трех чисел, поступающих на входной информациoHHblfl вход 9, в устройстве оказывается записанным максимальное — второе число.

Использование в устройстве для сравнения двоичных чисел только унифицированных широкораспространенных функциональных узлов и элементов позволяет реализовать это устрой ство Практически на любой элементной базе.

68 6

Использование унифицированного суммирующего двоичного счетчика вместо собранного из отдельных счетных триггеров вычитающего двоичного счет. чика или работающего в режиме вычйтания реверсивного двоичного счетчика позволяет уменьшить стоимость данного узла не менее чем в 2 раза.

Устройство для сравнения двоичных чисел, содержащее суммирующий двоичный счетчик, триггер, элементы

И и элемент НЕ, причем информационный вход устройства соединен со входом установки в нулевое состояние триггера и первыми входами первого и второго элементов И, второй вход первого элемента И соединен с выходом третьего элемента И, второй вход второго элемента И вЂ” с выходом третьего элемента И через элемент

НЕ, выход первого элемента И соединен с информационными входом суммирующего двоичного счетчика, а управляющий вход устройства соединен со входом установки в единичное состояние триггера, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства за счет применения унифицированных элементов, в него введены второй суммирующий двоичный счетчик и группа элементов ИЛИ-НЕ, первые входы которых соединены с нулевым выходом триггера, вторые входис выходами разрядов первого суммирующего двоичного счетчика соответственно, а выходы — с установочными входами второго суммирующего двоичного счетчика, выходы разрядов которого соединены со входами третьего элемента И, а вход установки в . нулевое состояние соединен с управляыцим входом устройства, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 641442, кл. G 06 F 7/02, 1977.

2. Авторское свидетельство СССР.

h"-.645152, кл. 6 06 F 7/02, 1977 (прототип).

934468

Составитель В. Горохов

Техред И. Гайду Корректор А. Гриценко

Редактор Л. Пчелинская

Заказ. 3937

45 Тираж 73 1 Подписное

ВНИИНИ Государственного иоии гееа СССР но делаи изобретений и оиерыаий

113035, Иосква, Ж-35, Раупюиея наб., д. 4/5

Филиал ППП Патент ° г, Ужгород., ул. ИроЬжтиая, 4