Устройство для прерывания программ

Иллюстрации

Показать всеРеферат

Союз Советскик

Соцнапнстмческик

Республик

О П И С А Н И Е ()9344?4

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 27. 08. 80 (21) 2998554/18-24 с присоединением заявки Рв (23}приоритет

Опубликовано 07.06. 82. Бюллетень Фе 21 (ы)м. Кл.

G 06 F 9/46

9вуааретвопвй кемвтет

СССР ао делен иэе4ретеник и открытий (} УДК 681. . 323 (088. 8) Дата опубликования описания 10 .06. 82 (72) Авторы изобретения

И.Б. Баранов и А.И. Огнев 1 (:ЙСИ9щ,Ь о

1М

" %!7 )L%ХЕдтяб.

".а t3

ЛенингРадское специальное констРУктоРское юРо ЙРЬ4 ЩТР;е тяжелых и уникальных станков (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАИИ

Изобретение относится к вычислительной технике и может быть исполь" зовано в электронных вычислительных машинах (ЭВИ) в качестве узла прерывания программ по заданному адресу.

Известно устройство для прерыва" ния программ, содержащее генератор импульсов, два регистра задания временного интервала, инверсный счетчик и счетчик времени, которое прерывает программу по истечении заданного временного интервала 51).

Недостатками данного устройства . являются ограниченные функциональные возможности точного прерывания программы в заранее заданном месте программы.

В ЭВИ с синхронным принципом функционирования неточность прерывания определяется несинхронностью генератора импульсов известного устройст. ва и генератора ЭВИ, а также неточностного определения момента запуска программы.

Точность обработки временного ин тервала повышают путем увеличения частоты генератора импульсов данного устройства, однако это требует увеличения разрядности двух регистров задания временного интервала и счетчика времени, что делает устройство громоздким, а вычисление задаваемого интервала времени трудоемким. В ЭВИ с асинхронным принципом функционирования, когда компоненты системы с такого типа ЭВИ работают с наиболее возможной скоростью и время циклов команд зависит от скорости работы каждого компонента. Применение данного устройства становится невозможным из-за непредсказуемости величины задаваемого интервала времени, необходимого для выполнения программы.

Известно также устройство преры" вания программы по заданному адресу вычислительной машины типа СИ-1.

Устройство прерывания программы nr

93447 заданному адресу содержит регистр адреса, адресную шину оперативного запоминающего устройства (ОЗУ) элемент сравнения, триггер, формирователь кода прерывания и шину прерывания t2).

Однако известное устройство прерывает программу лишь при обращении процессора к заданной ячейке ОЗУ.

При отладке программ и для выпол- р нения заданного участка программы применение известного устройства создает ряд неудобств. Если, например, в заданной ячейке ОЗУ модифицируются адреса внешних устройств. (ВУ), то 1 невозможно остановить программу при обращении процессора к конкретному

ВУ. Кроме того, по заданному адресу

ОЗУ или ВУ процессор может выдавать (t о информацию в цикле "Вывод либо принимать ее .в цикле "Ввод".

Таким образом, для выполнения точного прерывания в заранее заданном месте программы необходимо прерывать программу не только при обращении про-уу цессора к ячейкам ОЗУ, но и при обращении его к ВУ, причем либо при вводе информации в процессор, либо при выводе информации из него.

Известное устройство не позволяет отрабатывать и отлаживать программы с указанными условиями.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения прерывания по адресу ввода (вывода).

Поставленная цель достигается тем, что в устройство для прерывания программ, содержащее регистр адреса, элемент сравнения, первый триггер, формирователь кода прерывания, выход которого соединен с выходом устройства, выход регистра адреса соединен с первым входом элемента сравнения, второй вход которого соединен с адресным входом устройства, а выход - с вхо45 дом первого триггера, введены два элемента И, второй и третий триггеры, причем выход первого триггера соединен с первыми входами элементов И, вход признака "Вывод" устройства сое- + динен со вторым входом первого элемента И, вход признака "Ввод" устройства соединен со вторым входом второго элемента И, выходы второго и третьего триггеров соединены с треть- ими входами первого и второго элементов И соответственно, выходы которых соединены со входами второго и треть4,ф его триггеров соответственно и с первым и вторым входами формирователя кода соответственно.

Кроме того, формирователь кода прерывания содержит два триггера, элемент ИЛИ, элемент И, формирователь импульса сброса и шифратор, выходы которого соединены с выходом формирователя, первый вход шифратора соединен с выходом элемента И, второй вход шифратора соединен с первым входом элемента ИЛИ и с выходом первого триггера, третий вход шифратора подключен ко второму входу элемента ИЛИ и к выходу второго триггера, первый вход элемента И соединен с первым входом формирователя импульса сброса выходом элемента ИЛИ и с выходом фор. мирователя, второй вход элемента И соединен со вторым входом формирователя сброса и первым входом формирователя,второй и третий входы формирователя соединены с информационными входами первого и второго триггеров, соответственно, выход формирователя импульса сброса соединен со входами сброса первого и второго триггеров.

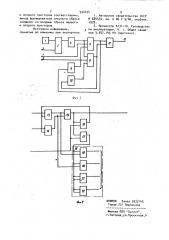

На фиг. 1 представлена структурная схема устройства; на фиг. 2структурная схема формирователя кода.

Устройство содержит регистр 1 ад-. реса, выход которого соединен с первым входом элемента 2 сравнения, второй вход которого соединен с адресной шиной 3 процессора. Выход элемента 2 сравнения соединен через первый триггер 4 с первыми входами первого и второго элементов И 5 и 6, второй вход первого элемента И 5 соединен с входом признака "Вывод" 7 устройства, второй вход второго элемента И 6 соединен с входом признака "Ввод" 8 уст.. ройства, третий вход первого элемента И 5 соединен с выходом второго триггера 9, а третий вход второго элемента И 6 соединен с выходом третьего триггера 10. Выход первого элемента И 5 соединен с первым входом формирователя 11 кода прерывания и со сбросовым входом второго триггера 9, выход второго элемента И 6 соединен со вторым входом формирователя

11 кода прерывания и со сбросовым вхо дом третьего триггера 10, а выход формирователя кода 11 прерывания соединен с шиной 12 прерывания. В состав формирователя кода прерывания входят два триггера 13 и 14, элемент

ИЛИ 15 формирователь 16 импульса

Формула изобретения

5 9344 сброса, элемент И 17, шифратор 18, содержащий группу элементов И 19-22.

Устройство работает следующим образом.

В регистр 1 адреса записывается код адреса ОЗУ или BY, по обращению процессора к которому необходимо прервать программу. Затем, если необходимо прервать программу при выводе информации по заданному адресу, fO устанавливают второй триггер 9; если необходимо прервать программу при вводе информации - устанавливают третий триггер 10. Если требуется прервать программу в любом случае (как 1s при выводе, так при вводе информации), устанавливают второй и третий триггеры 9 и 10.

Пусть, например, устройство подготовлено для прерывания программы щ при выводе информации по заданному адресу. Тогда при выполнении программы код адреса, поступающий с выхода регистра 1 адреса на элемент 2 сравнения, постоянно сравнивается у с кодами адресов ОЗУ или ВУ, генерируемых процессором в адресную шину 3. При появлении в адресной шине 3 кода адреса, совпадающего с заданным, элементом 2 сравнения ус- щ танавливает первый триггер 4. Если при этом информация выводится, то сиr. нал входа признака "Вывод" 7 поступает на первый элемент И 6, который срабатывает и сигнал с его выхода no- ступает на формирователь 11 кода прерывания и в то же время сбрасывает второй триггер. Формирователь 11 кода прерывания генерирует в шину 12 прерывания код прерывания, соответст- в вующий циклу "Вывод" по заданному адресу. Если же по заданному адресу следует ввод информации, то первый и второй элементы И 5 и 6 не срабатывают, а при генерации процессором следующего адреса, не совпадающего с заданным, элемент 2 сравнения сбрасывает первый триггер 4.

Таким образом, применение предлагаемого устройства позволяет обеспечить прерывание программы не только при обращении процессора к ячейке ОЗУ> но и при обращении его к любому BY, при этом учитывается:выводится информация по адресу ОЗУ или ВУ или вво55 дится, что расширяет функциональные возможности предлагаемого устройства и позволяет точно прервать программу в заранее заданном месте программы, 74 6

Это делает менее трудоемкими процессы отладки программ и повышает удобство при работе над программами.

1. Устройство для прерывания программ, содержащее регистр адреса, элемент сравнения, первый триггер, формирователь кода прерывания, выход ко". торого соединен с выходом устройства, выход регистра адреса соединен с первым входом элемента сравнения, второй вход которого соединен с адресным входом устройства, а выход - свходом первого триггера, о т л и ч,а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения прерывания по адресу ввода (вывода), в него введены два элемента И, второй и третий триггеры, причем выход первого триггера соединен с первыми входами элемента И, вход признака "Вывод" устройства соединен со вторым входом первого элемента И, вход признака "Ввод" устройства соединен со вторым входом второго элемента И, выходы второго и третьего триггеров соединены с третьими входа" ми первого и второго элементов И соответственно, выходы которых соединены соответственно с входами второго и третьего триггеров и с первым и вторым входами формирователя кода прерывания.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что формирователь кода прерывания содержит два триггера, элемент ИЛИ, формирователь импульса сброса, элемент И, шифратор, выходы которого соединены с выходом формирователя, первый вход шифратора соединен с выходом элемента И, второй вход шифратора соединен с первым входом элемента ИЛИ и с выходом первого триггера, третий вход шифратора подключен ко второму входу элемента ИЛИ и к выходу второго триг. гера, первый вход элемента И соединен с первым входом формирователя импульса сброса, выходом элемента

ИЛИ и с выходом формирователя, второй вход элемента И соединен со вторым входом формирователя сброса и первым входом формирователя, второй и третий входы формирователя соединены с информационными входами первого

934474

Фиг f и второго. триггеров соответственно, выход формирователя импульса сброса соединен со входами сброса первого и второго триггеров.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство CCCP

N 684555 кл. G 06 F 9/46, опублик. 1979

2. Процессор А131-10. Руководство по эксплуатации. Ч. !. Общие сведения 3.057.145 РЭ (прототип).

ВНИИПИ Заказ 3937/45

Тираж 731 Подписное

I филиал ППП "Патент", г.ужгород,ул.Проектная,4 .