Имитатор дискретного канала связи с ошибками синхронизации

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О П И С А Н И Е (934479

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву N 707 183 (22) Заявлено03.03.80 (2l )2924168/18-24 с присоединением заявки №(23) ПриоритетОпубликовано 07.06,82. Бюллетень № 21

Дата -опубликования OBHcaHMR 10.06.82 (51) М. Кл.

Я 06 F 15/20

3веуяерстеипяне квинтет

СССР ав делам нзоВретеняй н втхритнй (53 ) УД К 68 1. . 325(088.8) О. Б. Юминов, В. В. Хворенков, И. 3. Климов, В. H. Сыркин и Ю. И. Евсеев (72) Авторы изобретения

Ижевский механический институт (7t) Заявитель (54) ИМИТАТОР ДИСКРЕТНОГО КАНАЛА СВЯЗИ

С ОШИ БКАМИ СИНХРОНИЗАЦИИ

Изобретение относится к радиотехнике н может быть использовано для ста« тистического моцелирования систем передачи дискретных сообщений.

По основному авт. св. N 707183 известен имитатор дискретного канала связи с ошибками синхрснизации, содержаший сумматор по модулю два, выход и первый вход которого являются соответ-. ственно выходом и первым входом имита- тора, блок синхронизации, первый вход ко-то торого является вторым входом имитатора, а вькод соединен с вхоцом тт.нерат г ра марковской нослецовательности, первый выход кттФорого соединен с вторым вхоцом блока синхронизации и с входом датчика случайных чисел, блок промежу точной памяти, пороговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по модулю gea, . а первый и второй входы алемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последовательности, 2 третий выход которого через блок промежуточный памяти соединен с первым входом порогового сумматора, второй вход которого подключен к выходу датчика случайнык чисел Г1 .

Недостатком,известного имитатора яв» ляется то, что он моделирует только ошибки трансформации и не учитываер. ошибки синхронизации, которые проявляются в выпадении н вставках символов в информационную последовательность, что снижает достоверность моделирования дискретного канала связи.

Hemü изобретения — повышение точно сти.

Поставленная цель цсстигается тем, что в имитатор введены дополнительный элемент И, сдвиговый регистр, дешифратор и коммутатор, причем вход сцвигового рет истра является первым входом имитатора, выходы сдвнгового регистра подключены к информационным входам комму

raropa, выход которого соединен с первым

3 9 344 входом сумматора по модулю два, второй выход генератора марковской последовательности соединен с первым входом дополнительного элемента И, второй вход которого подключен к первому выхопу пешифратора, вход которого соединен с первым выходом генератора марковской последовательности, первый и второй выходы дещифраторв, а также выход дополнительного элемента И соедшены соответс 1@ венно с первым, вторым и третьим управ-.

° ляюшими входами коммутатора.

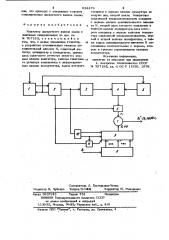

На чертеже представлен предлагаемый имит втор.

Имитатор содержит блок 1 синхрони- 15 зации, генератор 2 марковской nocnegoaaтельности, блок 3 промежуточной намятй, пороговый сумматор 4, датчик 5 случайных чисел, элемент И 6, сумматор 7 помодулю пва, сдвигающий регистр 8, ком- мутатор 9 дешифратор 10, элемент И 11.

Имитатор работает следующим образом.

В начале работы внешний синхроимпульс запускает блок 1, который вырабатывает сигнал, запускаюший генератор 2 марков- у5 ской последовательности. На первом такте работы генератор 2 марковской последовательности на втором его выходе появляется сигнал, который опрашивает логический элемент И 6. Этим же сигналом через ключ 11, поскольку на его первый вход сигнал запрета с пешифраторв 10 не поступал, опрашивается реверснвный коммутатор 9, а так как в начале работы реверсиьный коммутатор 9 находится в

П 35 состоянии rn= —, то при опросе он про-. пускает информацию с rn разряда сдвигаюшего регистра 8 на вход сумматора 7 по модулю два. Поскольку нв входы поро гового сумматора 4 ничего не подавалось, 40 то на входе элемента И 6 присутствует низкий уровень, и при его опросе на вход сумматора 7 по мопупю двв сигнал не поступает. После окончания цикла поиска, состояние цепи Маркова на выходе генеpampa марковской последовательности .по45 является код состояния цепи Маркова С;, который задает адрес ячейки промежуточного блока 3 памяти, в которой хранится соответствуюшвя условная вероятность ошибки Kg Кроме тога, код состояния

56

1 поступает также на вход дешифратора 10, на первом выходе которого появляегся. сигнал, переводящий реьерсивный коммугатор из состояния m (пъ-Ц, если код состояния цепи Маркова соответствует состоянию, в котором происходит выпада ние симврла. На втором выходе дешифрвтора 10 появляется сигнал, когда коп

79 4 состояния соответствует вставке символа,: и переводит реверсиьный коммутатор 9 из пт в (с+1), а также запрешает et о опрос через Ключ 11. Если коп не соответствует ни вставке, ни выпадению символа в информвпионной послеповательнос ти, то сигналов на выхопе дешифрвтора

lO нет, и не изменяется состояние реверсивного комь утатора 9. При его опросе считывается информация с m разряда сдвигаюшего регистра 8, информация в котором автоматически сдвигается по приходу слепуюше r о информационного симво ла Ъ„, Одновременно с кодом состояния на третьем выходе генератора 2 марковской последовательности появляется сигнал, который подготавливвет блок 1 к новому циклу и опрашиьвет датчик 5 случайных чисел, который вырабатывает случайное равнораспределенное число. Это число подается на вход порогового сумматора 4, на второй вход которого поступает из блока 3 памяти соответствуюшая условная вероятность ошибки. Сигнал на выходе порогового сумматора 4 появляется в том случае, когда сумма этих пьух чисел больше единицы. коммутатора позволяет моделировать как ошибки трансформации, так и синхронизвС приходом слепуюшего синхроимпульса снова запускается генератор 2 марковской последовательности, и на втором такте его работы .опрашивается логический элемент

И 6, а через ключ 11 - реверсивный коммутатор 9. B результате на выходе элемента И 6 появляется сигнал ошибки, а иа выходе реверсивного коммутатора 8информационный сигнал, которые поступают нв входы сумматора 7 по мопулю пва, где происходит сложение информационного сигнала с сигналами ошибки.

Если код состояния соответствует выпаданию символа, то на выходе реверсивного коммутатора 9 находится информа« ция из (гп-l) разряда, а на выходе элемента И 6 - всегда О", твк как в блоке

3 памяти для этого состояния записана условная вероятность, равная О . Если код состояния соответствует вставке, то на выходе реверсивного коммутатора 9 находится 0", так квк его опрос звпрешен сигналом с выхода дешифратора 10 на ключ 11, причем состояние реверсивного коммутатора 9 увеличивается на епи ницу, в На выходе элемента И 6 находится сигнал вставки либо «1» с вероятностью .

,, щгбо»0«с вероятностью (1 - г,С

Включение в схему дешифратора, спвигвюшего реестра, ключа и реверсивного

5 934479 6 ции, что приводит к псвышению точности соединен с первым вхоцом суммутсра по моделирования дискретного канала свяж, модулю цва, второй выхоц генератора марковской послецсвательнссти соединен с первым входом цопоаштельного элвмев.

Ф о р м У л а и з о б р е т е н и я g та И, второй вход которого поцключен к первому выходу дешифратора,вхоц кото-Имитатор дискретного канала связи с рого смцинен с первым выходом генера ошибками синхронизации по авт. св. тора марковской последовательности, nap hh 707183, отличающийся вы№ и второй выходы цешифратора, а тактем, что, с целью повышения точности, 1о же выхоц дополнительного элемента И со в устройство дополнительно введены цо- соединены соответственно с первым, вто .полнительный элемент И, сцвиговый ре- рым и третьим управлякмцими вхоцами истр, дешифратор и коммутатор, причем коммутатора. вход сцвигового регистра является пер- Ист очники йнформации, вым вхоцом имитатора, выходы сдвигово- 1з принятые во внимание при экспертизе го регистра подключены к информацион- 1. Aâòîðñêîå свицетельство СССР ным вхоцам коммутатора, выход которого М 707183, кл. Q 06 F 15/20, 1978.

Составитель Л. григорьянц-Чтенц

Редактор Н. Чубелко Техрец ИГайФ . Корректор Ю. Макаренко

Заказ 3937/45 Тираж 731 . Подписное

ВНИИПИ Госуцарственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35р Раушская наб., ц. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 с с