Умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соввтскик

Социапнстичвсиик

Рес убп

Опубликовано 07.06.82. Бюллетень йв 21

Дата опубликования описания 07.06.82 (51)M. Кл.

G 06 G 7/16

3Ьеударстеанный квинтет

СССР вв делам нзабретеннй н отнрытнй (53) УДК 681,335 (088.8) (72) Автор изобретения

М. Я. Хамитов (71) заявитель (54) УМНОМ(ИТЕЛЬ ЧАСТОТЫ

Изобретение относится к автоматйке и вычислительной технике и может быть использовано в устройствах, где необходимо умножить частоту последовательности прямоугольных импульсов на три.

Известен умножитель частоты, содержащий генератор тактовых импульсов, первый счетчик, основной делитель частоты, второй счетчик, регистр, 10 блок сравнения, дополнительный делитель частоты, логические элементы, триггер управления, известный уиножитель производит заполнение промежутка между двумя импульсами и импульсами 1 ).

Недостатком такого умножителя является то, что он для эффективной работы требует большую скважность отличающуюся от входной.

Наиболее близким техническим решением к предлагаемому является умножитель частоты, содержащий первый инвертор, интегратор, вход которого является входом умножителя, первый и второй блоки сравнения, первые входы которых объединены и через фильтр подключены ко входу умножителя, вторые входы блоков сравнения соответственно подключены к выходам второго и третьего инверторов, выходы блоков сравнения подключены соответственно к первым входам сумматоров по модулю два, второй вход первого суиматора по модулю два подклочен к выходу второго сумматора по модулю два, второй вход которого является входои умножителя (2(.

Однако в известном устройстве не" достаточная точность работы.

Цель изобретения - повышение точности °

Поставленная цель достигается тем, что в умножитель частоты, содержащий первый интегратор, вход которого является входом умножителя, первый и второй блоки сравнения, первые входы которых абъединены, первый, второй

934490

55 и третий инверторы, введены второй интегратор, источник опорного напряжения и четыре элемента И-НЕ, вход второго интегратора через первый инвертор подключен к входу умножителя, выходы интеграторов подключены соответственно ко вторым входам блоков сравнения, выход источника опорного напряжения подключен к первым входам блоков сравнения, выход первого блока сравнения подключен к первому входу первого элемента И-НЕ и ко входу второго инвертора, выход второго блока сравнения подключен к первому входу второго элемента И-НЕ и к входу третьего инвертора, вторые входы

4 ервого и второго элементов И-НЕ i объединены и подключены к входу множителя, выходы второго и третьего инверторов соответственно подключены к первому и второму входам третьего элемента И-НЕ, третий вход которого подключен к выходу первого инвертора, выходы первого второго и третьего элементов Й-НЕ подключены к соответствующим входам элемента И, выход которого является выходом умножителя.

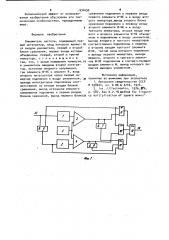

На фиг. 1 приведена функциональная схема умножителя частоты; на фиг.2 временные диаграммы, поясняющие его работу.

Умножитель частоты содержит интеграторы 1 и 2, блоки 3 и 4 сравнения, источник 5 опорного напряжения, инверторы 6-8, элементы И-НЕ 9- 11, weмент И 12, входную и выходную шины

13 и 14 соответственно. Причем входная.шина 13 соединена со входом интегратора 1, со вторыми входами элементов И-НЕ 9 и 10 и со входом инвертора 6, а выход последнего соединен со входом интегратора 2 и с первым входом элемента И-НЕ 11. Выходы интеграторов 1 и 2 .соединены со вторыми входами блоков 3 и 4 сравнения соответственно, первые входы которых объединены и подключены к выходу источника 5 опорного напряжения. Выход блока 3 сравнения соединен с первым входом элемента И-НЕ 9 и со входом инвертора 7, выход которого соединен со вторым входом элемента И-НЕ 11.

Выход блока 4 сравнения соединен с первым входом элемента И-НЕ 10 и со .входом инвертора 8, выход которого соединен с третьим входом элемента И:

НЕ 11, а выходы элементов И-НЕ 9-11 подключены ко входам элемента И 12, 4 выход которого подключен к выходнои шине 14.

Умножитель частоты работает следующим образом.

Прямоугольная последовательность импульсов с периодом Т (фиг.2 а) с входной шины 13 поступает на вход ин-. тегратора 1, вторые входы элементов

И-НЕ 9 и 10, и через инвертор 6 на

so вход интегратора 2 и первый вход элемента И-НЕ 11, С интеграторов 1 и

2 пилообразные напряжения, сдвинутые относительно друг друга на 0,5 Т, поступают на первые входы блоков срав15 нения напряжений 3 и 4, достаточно чувствительные т.е. Уело << пилы. з

На первые входы блоков сравнения (напряжений) 3 и 4 поступает постоянный потенциал — с источника опорного

20 .напряжения величиной -- — ч пилы. На

3 блоках сравнения (напряжений) 3 и 4 образуются новые последовательности прямоугольных импульсов (фиг.2 б,в25 соответственно) со скважностью три и сдвинутые относительно друг друга на

0,5 Т. Передний и задний фронты таки> импульсов находятся в точке, соответ я ствуЬщей равенству пилообразного на" пряжения и опорного напряжения. Точка пересечения,т.е. точка, соответствующая равенству напряжений находит1 ся в --- Т от переднего и заднего

6 фронтов входных импульсов и не завиЗ сит от входной умножаемой частоты.

C -помощью инверторов 7 и 8, элемен" тов И-НЕ 9,10 и 11 получаются три последовательности импульсов (фиг. 2,д, r,e соответственно), на выходе элемента И образуется сигнал с частотой, равной утроенной частоте входного сигнала, причем со скважностью равной скважности входной последовательности и равной 2 (фиг. 2ж), умножитель содержащий таких утроителей будет умножать частоту входного сигнала в, 3 раза.

Повышение точности в предложенном устройстве обуславливается заменой фильтра вторым интегратором (как известно интеграторы обладают лучшей помехозащищенностью и линейностью, чем фильтры), а также введением цифровых схем инверторов вместо аналоговых, введением элементов ИЛИ-НЕ, И источника стабильного опорного напряжения.

5 .934490

Экономическии эффект о фф т от использо= сравнения подключен к первому входу вания изобретения о условле б ален его тех- первого .элемента И-НЕ и к входу втоническими осо енностями, б приведенными рого инвертора,выход второго блока сравнения подключен к первому входу выше. второго элемента И-HE и к входу третьего инвертора, вторые входы перФ а изобретения

Формула вого и второго элементов И-НЕ об.ьединены и подключены к входу умножителя, Умножитель частоты, содержащии пер- вы д р хо ы вто ого и третьего инверторов вый интегратор, вход которог орого являет- 1О соответственно подключены к первому ся вхо ом умножителя, первыи и вт орой и второму входам третьего элемента д у

И-НЕ т етий вход которого подключен блоки сравнения, первые входы которых И-, тре обьединены, первыи, вт орой и третий к выходу первого инвертора, выходы ! чаю ийся -первого, второго и третьего элеменинверторы, о т л и ч а ю щ и и с тств ю им тем, что, с целью повышения точно я точности,ts тов И-IIE подключены к соотве у щ в умножитель введены вторьи инт егра- входам элемента И, выход которого явтор, источник опорного на р и яжения

Э ляется выходом умножителя. три элемента И-НЕ и элемент И, вход второго интегратора чере рез первый ин- Источники информации, вертор подключен к входу умн множителя 2о принятые во внимание при экспвртизе

1, Авторское свидетельство ССС

2. Int. 3.Electronics, 197о,ргo, напряжения подключен к первым входам р. 5 7, Као . . ае о о блоков сравнения, выход первог рвого блокагз су mul t1рl i cation of sguare waves".

Составитель Т. Сапунова

Редактор И. Ковальчук Техред м,Тепер Корректор И.Иуска

Заказ 3938/46 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5 филиал ПЛП "Патент", г. Ужгород, ул. Проектная, 4