Широтно-импульсное множительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик пи 934493 (61) Дополнительное к авт. сеид-ву (22) Заявлено 171Q80 (21) 2995830/18-24 с присоединением заявки № (23) Приоритет

Опубликована 070682. Бюллетень ¹ 21

G 06 G 7/161

Госухарсттвеииый комитет

СССР по делам изобретений и открытий (53) УДК 681. 335 (088. 8) Дата опубликования описания 07. 06. 82 (72) Авторы изобретения

A.C.Äàâûäoâ, В.У.Кизилов и И.И.Смилянский

Харьковский ордена Ленина политехнический институт им. В И.Ленина (71) Заявитель (54) ШИРОТНΠ†ИМПУЛЬСН МНОЖЙТЕЛЬНОЕ

УСТРОЙСТВО

tg tЛ

9 — —— где

xiy

Изобретение относится к аналоговой вычислительной технике.

Известно широтно-импульсное множительное устройство, содержащее широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и компаратора, дополнительный компаратор, выход которого является выходом устройства, ключи и источники первого и второго вход-.. ных сигналов, выходы которых соответственно подключены ко входу интегратора и к первому входу компара тора (1).

Недостаток этого устройства низкая точность перемножения и сложность °

Наиболее близким по технической сущности к предлагаемому является множительное устройство, содержащее источник первого входного сигнала, источник второго входного сигнала, широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй вход которого подключен к выходу источника первого входного сигнала через блок умножения на знак, второй компаратор, первый вход которого подключен к выходу интегратора, а второй вход — к шине нулевого потенциала (2).

Недостатком известного множительного устройства является наличие погрешности, обусловленной задержками переключения компараторов, При учете задержек переключения компараторов выражение для выходной величины множительного устройства принимает вид х

Е, х U U + x (Ux — U х)- 6 х +xx), 9 — относительная разность длительностей раэнополярных импульсов на выходе первого компараторат длительность отрицатель1 ного импульса. — длительность положительного импульса; входные сигналы-сомножители;

U — порог срабатывания первого с компаратора;

U — напряжение на выходе первого компаратора;

934493

Ъ Г, и у время задержек переключения первого и второго компараторов соответственно.

Составляющая входного сигнала-сомножителя х входят в знаменатель этого выражения и компенсировать их простыми средствами не представляется возможным.

Цель изобретения — повышение точности.

1!оставленная цель достигается 10

-.eM, что в широтно-импульсном множительном устройстве, содержащем источники первого входного сигнала, второго входного сигнала, широтно-импульсный модулятор, состоящий иэ 15 последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй компаратор, первый вход которого подключен к выходу интегратора, а второй вход к шине нулевого потенциала, и блок умножения на знак, источник второго входного сигнала подключен. к первому входу второго компаратора через блок умножения на, знак, выход второго компаратора является выходом устройства, выход первого компаратора подключен к знаковому входу блока умножения на знак, выход первого компаратора подключен к выходу источника первого входного сигнала, второй вход интегратора подключен к выходу источника первого входного сигнала.

Такое построение схемы позволяет полностью исключить погрешность, обусловленную задержками второго компаратора. Для полной компенсации погрешности, обусловленной задержками первого компаратора, источ- 40 ник первого сигнала-сомножите>>я через резистор подключен к инвертирующему входу операционного усилителя первого компаратора.

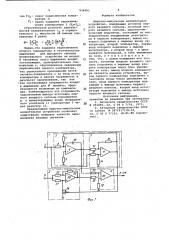

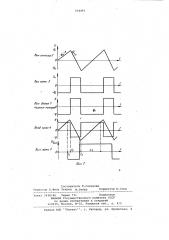

На фиг. 1 приведена принципиаль- 45 ная схема широтно-импульсного устройства; на фиг. 2 — временные диаграммы работы множительного устройства.

Широтно-импульсное множительное устройство содержит широтно-импульсный модулятор 1, состоящий иэ интегратора 2 и первого компаратора

3, второи компаратор 4 и блок 5 умножения на знак. Интегратор 2 содержит операционный усилитель 6, масштабные резисторы 7, 8 и 9 и интегрирующий конденсатор 10. Первый компаратор 3 содержит операционный усилитель 11, масштабные резисторы

12, 13 и 14 и резистор 15 обратной связи. Второи компаратор 4 содержит операционный усилитель 16, масштабные резисторы 17, 18 и 19.

Блок умножения на знак содержит операционнн1й усилитель 20, масштабЕсли на вход интегратора 2 подан входной сигнал-сомножитель х, а на вход блока 5 умножения на знак входной сигнал-сомножитель у, то происходят следующие изменения в работе схемы. Скорость изменения напряжения на выходе интегратора 2

1 равна — — (U + x) при положитель1

Т ном и Т (U — х) при отрицательном

Т, о напряжении на выходе компаратора 3.

Здесь+1> — напряжение на выходе компаратора 3; Т вЂ” постоянная вре- мени интегратора 2.

Изменяются также длительности отрицательного „ и положительного импульсов на выходе компаратора 4, которые с учетом задержек переключения компараторов равны:

2U С .(1)+х

Uc+ +

U + х

T Uc +Т

cU -х о

2 1. а

< U — х

T - - +T

+х о ные резисторы 21 и 22, резистор 23 обратнои связи и ключ 24 на полевом транзисторе.

Блок умножения на знак может быть выполнен в любом варианте1 в виде двух разнополярных ключей, подключающих ко входу второго компаратора прямой или инверсный выход второго источника У входного сигнала-сомно- . жителя или на операционном усилителе и ключе на полевом транзисторе. (фиг. 1). Источник первого входного сигнала х через масштабный резистор

12 подключен к инвертирующему входу операционного усилителя 11 компаратора 3.

Выход блока умножения на знак может быть подключен к любому из входов (инвертирующему или неинвертирующему) операционных усилителей 11 и 16 соответственно компараторов 3 и 4, при этом принцип функционирования устройства не нарушается, а изменяется лишь знак выходного сигнала и масштабный коэффициент при 8

Широтно-импульсное множительное устройство работает следующим образом.

Нри отсутствии входных сигналов интегратор 2 и компаратор .3 работает в автоколебательном режиме как релаксационный генератор. На выходе интегратора 2 формируется симметричное йилообразное напряжение, а на выходе компаратора 3 — напряжение прямоугольной формы. Компаратор 4 переключается при переходе через ноль напряжения на выходе интегратора

2, и на его выходе также формируется симметричное прямоугольное напряжение.

934493 где U — порог переключения компас ратора 3; время задержки переключечения компаратора 3 (T„a

Относительная разность длительностей положительного t и отрицательного 4 импульсов на выходе компаратора 4 равна И

Е t tä х + Цях %

"îc+" !

О

Ту

Видно,что задержка переключения второго компаратора в окончательное выражение для выходного сигнала . множительного устройства не входит.

В числитель этого выражения входит 15 составляющая, пропорциональная сом-! ножителю х, обусловленная задержками переключения первого компаратора, 1 что равносильно прохождению части сигнала-сомножителя х на вход этого компаратора и вносит погрешность в результат перемножения, так как

° эта составляющая погрешности входит в выражение для 6 линейно, представляется возможным ее компенсация. Компенсируется эта погрешность подключением выхода источника первого входного сигнала-сомножителя ф к инвертирующему входу операционного усилителя 11 компаратора 3 через резистор 12.

Предлагаемое широтно-импульсное множительное устройство позволяет существенно повысить точность перемножения входных сигналов.

Формула изобретения

Широтно-импульсное множительное устройство, содержащее источник первого входного сигнала, источник второго входного сигнала, широтно-импульсный модулятор, состоящий иэ последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй компаратор, первып вход которого подключен к выходу интегратора, а второй вход — к шине нулевого потенциала, и блок умножения на знак, о т л и ч а ю щ е е с я тем, что, с целью повышения его точности, источник второго входного сигнала подключен к первому входу второго компаратора через блок умножения на знак, выход второго компаратора является выходом устройства, выход первого компаратора подключен к знаковому входу блока умножения на знак, вход первого компаратора подключен к выходу источника первого входного сигнала, второй вход интегратора подключен к выходу источника первого входного сигнала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 492886, кл. G 06 G 7/16, 1973.

2. Авторское свидетельство СССР по заявке .9 2871917/18-.24, кл. 6 06 6 7/161, 18.01.80 (прототип) .

934493 дыА интегр Г

Юькг л.аж.,У

Юьм Ильи Х перекп. иолярн0

Фод лиы4 д

У

Ьах

Составитель Т.Сапунова

Редактор Л.Филь Техред М.Тепер Корректор Н.Стец

Заказ 3938/46 Тираж 731 Подписное

ВНИИПИ Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал IIIIII Патент, г. Ужгород, ул. Проектная, 4