Экстраполятор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсиик

Социалистическик

Республик пи 934504 (6l ) Дополнительное к авт. синд-ву (22)Заявлено 10.10.80 (2! ) 298/674/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 07.06.82„Бюллетень Мв21

Дата опубликования описания 07. 06 . 82 (5! )М. Кл.

6 06 С 7/30 (Ъаудератвеииый каиитет

СССР по делен изобретений и открытий (53) УДК 681. 3 (088. 8) (g4) ЭКСТРАПОЛЯТОР л

Г (пТ + t ) = (йТ) +

Изобретение относится к автома-, тике и вычислительной технике, предназначено для реализации экстраполяционной зависимости второго порядка и мбжет быть использовано в системах сбора и обработки информации, устройствах телеметрии, связи и управления, в устройствах оперативного прогнозирующего контроля, для получения огибающей импульсного сигнала с постоянным шагом квантования и т.д.

Известен экстраполятор, содержащий аналоговый регистр сдвига и три интегрирующих усилителя (1), Недостатками этого экстраполятора являются низкая точность экстраполяции и ограниченные фу нкцио-" нальные возможности, большая чувствительность к помехам во входном сигнале и погрешностям работы аналогового регистра сдвига.

Наиболее близким к предлагаемо" му является устройство, реализующее экстраполяционную зависимость второго порядка

3F(nT7-4F ((п-1 ) Tj+F ((n -2) Т3

ГСпТ 3-2Г (п-1) Т)+Р P(n-2) Т3

2Т2 ™ где Т - период квантования;

t - -время внутри интервала квантования (0e t <Т);

Г пТ3 - дискретные значения восстанавливаемого сигнала (n = л =О, 1, 2,...);

ГЬ" 3- экстраполированное значение восстанавливаемого аналогового сигнала.

Этот экстраполятор содержит трех- разрядный аналоговый регистр сдвига, два интегратора и один сумматор f2).

Недостаток известного экстраполятора - большая чувствительность к входным помехам, и погрешностям работы аналогового регистра сдвига.

Цель изобретения — повышение точности.

Поставленная цель достигается за счет того, что в экстраполяторе, содержащем аналоговый регистр сдвига, вход которого является входом экстраполятора, сумматор, выход которого является выходом экстраполятора, и два интегратора, выполненных соответственно на первом и втором операционных усилителях, интегрирующих конденсаторах, один. из которых включен между выходом и инвертирующим входом соответствую" щего операционного усилителя, а второй - между неинверитрующим входом соответствующего операционноro усилителя и шиной:нулевого потенциала, ключах, включенных параллельно интегрирующим конденсаторам, и масштабирующих резисторах, управляющие входы ключей и аналогового регистра сдвига соединены с шиной тактовых импульсов, первый выход аналогового регистра сдвига соединен с первым суммирующим входом сумматора и через соответствующие и сштабирующие резисторы — с неинвертирующими входами первого и второго операционных усилителей, выход первого операционного усилителя соединен через соответствующий масштабирующий резистор с неинвертирующим входом второго операционного усилителя, выход которого соединен через соответствующий масштабирующий резистор с вторым суммирующим входом сумматора, второй выход аналогового регистра сдвига соединен с.третьим суммирующим входом сумматора и через cooTBeTствующие масштабирующие резисторы — с инвертирующими входами первого и второго операцион° ных усилителей, третий выход аналогового регистра сдвига соединен с первым вычитающим входом сумматора и через соответствующие масштабирующие резисторы - с инвертирующими входами первого и второго операционных усилителей, четвертый выход — с вторым вычитающим входом сумматора и через соответствующие масштаб1рующие резисторы — с инвертир,ющими входами первого и второго операционных усилителей, а пятыи

4504 4 выход аналогового регистра сдвига соединен с четвертым суммирующим входом сумматора и через соответствующие масштабирующие резисторыс неинвертирующими входами первого и второго операционных усилителей.

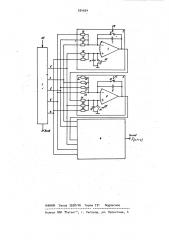

На чертеже представлена схема экстраполлтора.

Экстраполятор содержит аналоговый

10 регистр 1 сдвига, интеграторы 2 и 3, сумматор 4, операционные усилители

5 и б, интегрирующие конденсаторы 7 и 8, клячи 9 и 10, интегрирующие конденсаторы !1 и 12, ключи 13 и 14, масштабирующие резисторы 15 — 26.

Экстраполятор работает следующим образом.

Экстраполяционная зависимость второго порядка реализуется по пя2о ти последним дискретным значениям входного сигнала. Она имеет вид

Г(пТ+ t)= а + a„t+ à t, 31 1 ГпТ )+ 9F ((n-1) Т3 где а а

25 35

-31 ((n-2) Т3-5F Е(п-3) Т 3+ ЗГ p(n-4) Т 3

54FEnTJ-13F Кп-1)T3л 70Т

40Г E(n-2) Т)-27F((n-3) Т 3+26F ((n-4) Т 3

70Т

2F(nT3-F((п-l)Т)-2F((n-2)Т а —

-F ((n-3) T J+2F Г(п-4) Т1

Я

0--С <Т.

Экстраполяционная формула L2) получена с помощью метода наименьших квадратов.

Неизвестные коэффициенты а, а, а находятся из условия минимума суммы квадратов отклонений Г и-з)Т) от 1 g(n-i)T3 i = 0, 1, 2, 4

Дифференцируя сумму кв::дебатов по а,. а, а и приравнивая к нулю о производные, получаем систему уравнений, решение которой дает значения ао, а, а, приведенные в форо> муле (. 2).

На очередном И-ном такте работы . за время записи gg< T в регистр записывается очередное значение входного сигнала 1:(nT), которое фиксируется на выходе а. Предшествующие значения 1 ((п-l)Т3, 934504 фиксируются соответственно íà выходах б - д. В течение времени записи интеграторы обнуляются.

11осле окончании записи очередного дискрета в регистр 1 интеграторы 2 и 3 переходят в рабочее состояние, и на выходе сумматора 4 формируется зкстраполирующий сигнал.

Интеграторы могут быть выполнены, как и в прототипе, на дифференциальных операционных усилителях с интегрирующими конденсаторами, включенными между инвертирующим входом и выходом усилителя, а также между неинвертирующим входом и шиной нулевого потенциала, и с ключами, параллельными соответствующим конденсаторам. Между входами интеграторов и входами операционного 20 усилителя включаются масштабирующие резисторы. При равенстве конденсасаторов и при наличии дополнительных резисторов, включаемых между инвертирующим входом операционного усилителя и шиной нулевого потенциала и уравниваюших суммарные активные проводимости по обоим входам усилителя, коэффициенты по каждому входу интегратора определяются че- 30 рез величину соответствующего входФормула изобретения

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

11. 467368, кл. G 06 G 7/30, 1975.

2. Авторское свидетельство СССР по заявке 4" 2961521/18-24, кл. G 06 G 7/30, 1980 (прототип).

Fg(n-2)Т), Г((п-3)T) и Г((п-4)yg

1 ного резистора К . =

Технико-зкономический эффект от M использования изобретения определяется повышением точности экстраполяции.

Экстраполятор, содержащий аналоговый регистр сдвига, вход которого является входом экстраполятора, сумматор, выход которого является выходом экстраполятора, и два интегратора, выполненных соответственно на первом и втором операционных усилителях, интегрирующих конденсаторах, один из которых включен между выходом и инвертирующим входом соответствующего операционного усилителя, а второй - между неинвертирующим входом соответствующего операционного усилителя и шиной нулевого потенциала, ключах, включенных параллельно интегрирующим конденсаторам, и масштабирующих резисгорах, управляющие входы ключей и аналогового регистра сдвига соединены с шиной тактовых импульсов, первый выход аналогового регистра сдвига соединен с первым суммирующим входом сумматора и через соответствую-, щие масштабирующие резисторы - с неинвертирующими входами первого и второго операционных усилителей, выход первого операционного усилителя соединен через соответствующий масштабирующий резистор с неинвертирующим входом второго операционного усилителя, выход которого соединен через соответствующий иасштабирующий резистор с вторым суммирующим входом сумматора, о т л и ч а юшийся тем, что, с целью повышения точности, второй выход ана-. логового регистра сдвига соединен с третьим суммирующим входом сумма" тора и через соответствующие масштабирующие резисторы — с инвертирующими входами первого и второго операционных усилителей, третий выход аналогового регистра сдвига соединен с первым вычитающим входом сумматора и через соответствующие масштабирующие резисторы — с инвертирующими входами первого и второго операционных усилителей, четвертый выход — с вторым вычитающим входом сумматора и через соответствующие масштабирующие резисторы - с инвертируоцими входами первого и второго операционных усилителей, а пятый выход аналогового регистра сдвига соединен с четвертым суммирующим входом сумматора и через соответст вующие масштабирующие резисторыс неинвертирующими входами первого и второго операционных усилителей.