Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

934521 соответственно с вторым и третьим входами формирователя кода.

Блок делителей частоты содержит два делителя на четыре, два цифровых сумматора и делитель с промежуточными выходом, вход, которого является входом блока делителей частоты., а первый и второй выходы соединены с входами соответственно первого и второго цифровых сумматоров, выход каждого из которых соединен с входом соответствующего 10 делителя на четыре, первые выходы делителей на четыре являются соответственно первым и вторым выходами блока делителей частоты, третий н четвертый выходы которого соединены с вторыми выходами делителей на четыре, lS третий и четвертый выходы делителя с промежуточным выходом соединены с пятым и шестым выходами блока делителей частоты, вход и седьмой выход которого соединены между собой.

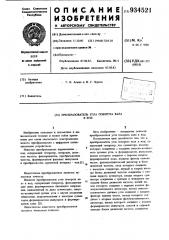

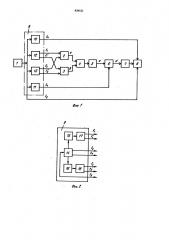

На фиг. 1 приведена блок-схема преобразователя угла поворота вала в код; на фиг. 2— .схема блока делителей частоты,вариант выполнения; па фиг. 3 — временные диаграммы, поясняющие работу преобразователя.

Преобразователь содержит генератор 1 частоты fb, сумматоры 2 и 3, синусно-косинусный датчик 4 угла, фильтр 5 нижних частот, фазочувствительный дете тор 6, формирователь 7 импульсов, формирователь 8 кода, блок 9 делителей частоты, в который входят делители

10 и 11 с выходами импульсов частот fa u

f0 и делители 12 и 13 частоты с расщепителями фазы выходных импульсов частот f и fz

В случаях, когда требуется преобразователь углаповорота вала в код, имеющий выход

35 в двоичном коде, блок 9 делителей частоты . содержит делитель 14 с промежуточным выходом, цифровые сумматоры 15 и 16 и де,лители 17 и 18 на четыре, Преобразователь работает следующим образом.

Ог генератора 1 на входы блока 9 (с входов делителей 10-13) поступают импульсы, частотой fb (фиг. 3, fb). На двух выходах делителя 12 частоты блока 9 формируются т р 45 импульсы Е1 и f1 (фиг. 3, Е,, Е,) частотои

Е,, сдвинутые относительно друг друга по фазе на 1/4 периода. На двух выходах делителя 13 частоты блока 9, имеющего коэффициент деления, отличный от коэффициента деления делителя 12, формируются импульсы >0

fz u fz (фиг, 3 fz fz) частотои fz сдвинутые по.фазе на 1/4 периода. Сигналы f< и поступают на входы сумматора 2, на выходе которого формируется сигнал а (фиг. За). При этом первая гармоНика сигнала Ф. имеет вид SS -Ь . 4<+1

1 „=Асов  — 1&1и2% — г -

Сигналы f< и fz поступают на входы сумматора 3, на выходе которого формируется сигнал (фиг. 3b). При этом первая гармоника сигнала имеет вид

? = А81И ЯЖ вЂ” ВЕИ 271 4 4.. .4 +5 в 2

Выходные сигналы Д.и ф сумматоров 2 и 3 поступают на входные обмотки датчика 4 угла. Напряжение с выходной обмотки датчика

4 поступает в фильтр 5 нижних частот; где происходит вьщеление сигнала с (фиг. З,c), представляющего собой сумму двух сигналов разностной (Ее — Ен) и суммарный (f0+Ен)

I частот. Сигнал с на выходе фильтра нижних частот имеет вид (1 = — Сов ЙВ K -3 -Ч ь

В с 6. О l4

cow (1>l(P gq) 1i1 )).= Ьсоь(1ГЦ1+W)oo11 1 1,t, 1 хЕ+ 2 У 41 Я. н=

\ где  — амплитуда сигнала с на выходе фильтра 5 нижних частот; р — пространственный угол взаимного положения входных и выходных обмоток датчика 4 угла.

Сигнал с с выхода фильтра 5 нижних частот поступает на один из входов фазочувствительного детектора 6, на второй вход которого с выхода блока 9 поступают импульсы опорной частоты Ее. В фазочувствительном детекторе 6 осуществляется синхронное детектирование и вьщелеиие с помощью фильтра нижних частот первой гармоники сигнала d (фиг. 3 д), частота которого равна Ен, а фаза соответствует взаимному положению входных и выходной обмоток датчика 4. При этом на фазочувствительном детекторе 6 практически полностью исключается из измерительного сигнала d . квадратурная составляющая.

Сигнал d с выхода фазочувствительного детектора 6 поступает на формирователь 7 импульсов. Прямоугольные импульсы с выхода формирователя 7 поступают на первый вход формирователя 8 кода, на второй вход которого с выхода блока 9 поступают импульсы частотой fa. В формирователь 8 кода по передним фронтам импульсов, поступающих на его первый и второй вХоды, формируются временные интервалы, которые заполняются импульсами частоты fb,, поступающими на третий вход формирователя 8 кода с выхода блока 9. Величина временного интервала в формирователе

8 кода соответствует взаимному положению входных и выходной обмоток датчика 4 угла.

Блок 9 делителей частоты работает следующим образом. Делитель 14 выполнен.в виде двоичного делителя частоты с 2п-двоичными разрядами (где n = log / ), а цифровые и сумматоры 15 и 16 выполнены в виде (n-.1)-: разрядных полных. двоичных сумматоров. Сигналы с п — 1 младших разрядов делителя 14 поступают на входы сумматоров 15 и 16 в качестве первого слагаемого. В качестве второго слагаемого на входы сумматора 15 поступают сигналы q последующих и-1 разрядов делителя 14. В качестве второго слагаемого на входы сумматора 16 поступают сигналы, инверсные сигналам второго слагаемого на. входах сумматора .15 (на входе переноса младшего разряда сумматора 15 должен быть установлен логический "0 *, a на входе переноса младшего разряда сумматора 16 — логическая

"1"). Выходные сигналы со старших разрядов сумматоров 15 и 16 поступают на входы делителей 17 и 18, которые могут бьггь выполнены в виде двухразрядных двоичных делителей.

В этом случае на выходе блока 9 формируются сигналы следующих частот: -Ха . Ап . Хв и аи o yn+1 < 1 4(ал„) Формула изобретения

f. Преобразователь угла поворота. вала в код, содержащий генератор, два сумматора, выходы которых соединены с входами синуснокосинусного датчика угла, и формирователь. импульсов, выход которого соештнен с первым . входом формирователя кода, о т л и ч а юшийся тем, что, с целью повышения точности преобразователя, в него введены фильтр

4521 6 нижних частЬт, фазочувствнтельный детектор н блок делителей частоты, вход которого соединен с выходом генератора, первый и второй выходы блока делителей частоты соединены с входами первого сумматора, входы. второго сумматора соединены с третьим и четвертым выходами блока делителей частоты, пятый выход которого соединен с первым входом фазочувствительного детектора, выход синус10 но-косинусного датчика угла соединен с входом фильтра нижних частот; выход которого соединен с вторым входом фаэочувствительного детектора, выход которого соединен с входом формирователя импульсов, шестой

1S и седьмой выходы блока делителей частоты соединены соответственно с вторым и третьим входами формирователя кода.

2. Преобразователь по ц. 1. о т л и ч аю шийся тем, что, блок делителей частоты з«п содержит два делителя на четыре, два цифровых сумматора и делитель с промежуточным выходом, вход которого является входом блока делителей частоты, а первый и второй выходы соединены с входами. соответственно перья вого и второго цифровых сумматоров, выход каждого иэ которых соединен с входом- соответствующего делителя на четыре, первые выходы делителей на четыре являются соответственно первым и вторым выходами блока делителей частоты, третий и четвертый выходы которого соединены с BtopblMH выходами делителей на четыре, третий и четвертый выходы делителя с промежуточным выходом соединены с пятым и шестым выходами блока делителей частоты, вход и седьмой выход которого соединены между собой.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР У409258, кл. G 08 С 9/00, 1971.

2. Авторское свидетельство СССР Н 525988, кл. G 08 С 9/04, 1974 (прототип). г

934521

Составитель Е Бударина

Техред А. Бабинец

Корректор В. Бутяга

Редактор В. Петраш

Заказ 3944/47

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Тираж 642 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5