Устройство для отображения графической информации

Иллюстрации

Показать всеРеферат

1(72) Автор изобретения

Ю. Л. Чверткнн (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ГРАФИЧЕСКОЙ

ИНФОРМАБИИ

Изобретение относится к вычислитель действие за счет отсутствия возможносной технике и может быть использовано ти уменьшения ступенчатого напряжения . при проектировании устройств отображе- на выходе сумматора кратно степени 2 ни я информации. по мере уменьшения длины вектора с одИзвестны устройства отображения новременным масштабированием кодов графической информации в виде векторов, проекций вектора, с регулированием дли

S содержащие преобразователь код-напря- - тельности выходного напряжещ|я при фик жение, умножители, генератор линейно- сированной амллитуде внутри каждой изменякнцегося напряжения, компаратор ступени. и т.д. (1). Цель изобретения - повышение быст

Наиболее близким по технической сущ- родействия устройства, 10 ности к предлагаемому является устрой- Поставленная пель достигается тем, ство для отображения графической инфор- что s устройство, содержащее первый и мании, содержащее первый и второй пре- -второй преобразователи код-напряжение, обраэоватепн код-напряжение, соединен- соединенные с одними иэ входов первого та ные с одними входами первого и второ и второго сумматоров, соединеннык с го сумматоров, соединенных с индикато- индикатором, умноаатели, подключенные . ром, умножнтелн, подкшоченные к дру- к другим входам первого и второго сумгим входам первого и второго суммато маторов, последовательно соединенные ров, последовательно соединенные гене генератор импульсов, первый счетчик и ратор импульсов, один счетчик и третий третий преобразователь «од-напряжение, преобразователь код-напряжение (21 введены первый и второй элементы сдвиОсновным недостатком известных га, делитель частоты, дешифратор, четустройств является ограниченное быстро- вертый и пятый преобразователи код-на3 9345 пряжение, второй счетчик, третий сумматор и блок элементов И-ИЛИ, выходы первого эпемента сдвига соединены с одними иэ вхсщов умножителей, другие входы эпементов сдвига соединены между собой и выходом дешифратора и одним иэ входов блока эпементов И-ИЛИ, выход второго элемента сдвига подключен к одному из входов делителя частоты и входу четвертого преобраэоватепя код-напряжение, выход которого соединен с другим входом третьего преобразователя код-напряжение, другой вход делителя частоты подключен к выходу генератора импульсов, выход - к входам счетчиков, выходы которых соединены с другими входами бпока эпементов И-ИЛИ, выход которого подкпючен к входу генератора импульсов, выходы третьего и пятого преобразователей код-напряжение соединены с входами третьего р сумматора, подключенного к другим входам умножителей.

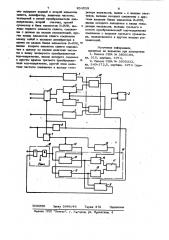

На чертеже представлена функционапьгая схема предложенного устройства.

Устройство содержит преобразователи 25

1 и 2 код-напряжение, умножитепи 3 и

4, индикатор 5 (эпектроннопучевую трубку), эпементы 6 и 7 сдвига, дешифратор

8, блок 9 элементов И-ИЛИ, счетчики

10 и 11, генератора 12 импупьсов, де- зр питель 13 частоты, преобраэоватепи 1416 код-напряжение, сумматоры 17-19.

Устройство работает спедуюшим образом.

Коды координат начапа вектора поступают на преобразователи 1 и 2, устанавпивая пуч в начальную точку экрана. На кодовые входы умножителей Э и 4 поступают коды приращений,8>> и К gy проекций вектора на оси координат. Выходные сигналы с преобразоватепей и умножитепей 1, 3 и 2, 4 суммируются с помощью сумматоров 18 и 19. С приходом на вход генератора 12 45 команды начапа формирования вектора на выходе преобразоватепей 14 и 15 вырабатывается ступенчато-возрастающее напряжение Ц (t), дпитепьность .которого регупируется как функция длины вектора.

В результате перемножения напряжения

Ц(4;). на масштабные коэффициенты Ngg,éäó иа выходе умножителей 3 и 4 вырабаты-, ваются отклоняющие напряжения U(QPQ<

Ц().Яду, которые скпадываются с выход- - 5 ными напряжениями преобразователей

1 и 2 и поступают на координатные уснпитепи индикатора 5, 39 4

Дпя того, чтобы при формировании векторов раэпнчной длины скорость записи была постоянной, необходимо регупировать период Т> напряжения ОЩ пропорционально длине модуля вектора

/ я

4 6 + 46

Регулирование периода Тр напряжения

Ц® в предлагаемом устройстве производится путем изменения числа ступенек ! выходного сигнала, образованного счетчиками 10 и 11, преобразоватецем 14, 15 и сумматором 17. Счетчик 10 обеспечивает пересчет по переменному модупю, определяемому коэффициентом пересчета К делителя 13 частоты, производящего сброс. Счетчик 11 работает по модулю 2. Оба счетчика образуют, по существу, единый счетчик, у которого код младших разрядов формируется счетчиком

10, а код старших разрядов - счетчиком 11.

Число ступенек выходного сигнала сумматора 17 равно

К=КлК где К вЂ” чиспо состояний счетчика 10; л число состояний счетчика 11.

При числе разрядов счетчиков 10 и

11, равном g,ю соответственно, чиспо состояний счетчиков K< и К лежат в спедуюших пределах:

28л К 1

Иф Ку 2

Е+ =И, где И вЂ” число разрядов кода.

Длительность периода Т равна т = ° К =t К К

В 1 ТОКТ ТОК-т 3К

Иэ поспеднего выражения следует,что можно варьировать, меняя как К,так и К <

При этом масштаб преобразования преобраэоватепей 1 и 2 должен быть неизменным, в силу чего размах U(+)aomcev быть фиксирован, либо при его изменении допжно производиться соответствующее масштабирование кодов проекций М у„N ау, Число состояний счетчика 10 можно устанавливать с шагом "1», поэтому дпя фиксирования размаха 0(О необходимо выпопнять следующие соотношения;

И® = ЬО„К„К =ЬО К =СОИ

t откуда

a0q

aU =—

Кл

Здесь Дал - единичное приращение выxoworo напряжения преобразователя 14, 9345

a0g — единичное приращение выходного напряжения преобразователя 15.

Из последнего выражения следует,что преобразователь 14 должен работать с ! переменным масштабом преобразования по закону 1/ К .

Вепичина вариации АО

< )< макс

=Д» 4МЫ»»

1О что обеспечивается изменением величины эталонного напряжения преобразователя

14 в пределах от U> до 0,5 О путем изменения кода на входе преобразователя 16. !

Число состояний счетчика 11 изменяется по двоичному закону, что можно реа-. лизовать либо отключением младших разрядов при неизменном размахе U8), либо отключением старших разрядов, что приводит к изменению размаха О (т) по двоичному закону. В предлагаемом устройстве производится отключение старших разрядов счетчика 11 с соответствующим масштабированием кодов проекций Йвх,Мв путем сдвига их в сторону старших разрядов. Управление величиной периода выходного сигнала сумматора 17 производится кодом модуля вектора с помощью дешифратора 8 (длины вектора) и эпемента 7 сдвига. Дешифратор 8 (дпины вектора) производит обнаружение номера после д него старшего значащего разряда и как бы грубую оценку длины вектора. При наличии на входе дешифратора 8 в старшем разряде погической "1" на его выходе

35 вырабатывается также погическая 1, При уменьшении кода N вдвое в старшем разряде на входе дешифратора 8 появляется логический О, а в предпоспеднем разряде - логическая 1 . Соответственю °

41 но на выходе дешифратора логическая 1 сдвигается. Нв всех остальных выходах вырабатывается логический 0 . При наличии в двух ст6рших разрядах погическо45 го "0" и логической "1" в разряде, смежном с ними, логическая "1 вырабатывается на другом выходе дешифратора.

Таким образом, по наличию логической "1 на том или ином выходе дешифpampa 8 можно производить грубую оцеи50 ку длины вектора. Выходы дешифраторв

8 соединены с входами блока 9 элементов И-ИЛИ дпя отключения разрядов счетчиков 10 и 11, причем на первые входы эпементов И поступают сигналы

55 переноса разрядов счетчиков 10 и 11, а на вторые - сигналы управления с выходов дешифратора 8 длины вектора. Вы39 6 ходы элементов И объединены через эпемент ИЛИ и соединены с входом генератора 12 управляющего тактовой частотой счетчиков 10 и 11.

Изменение кода длины вектора вызы« веет подключение входа генератора 12 к выходу переполнения различных разрядов счетчиков 10 и 11, вызывая тем самым изменение по двоичному закону длительности периода Т> и амппитуды 0(Исумматора 17; Необходимое при этом масштабирование кодов проекции вектора производится с помощью эпементв 6 сдвига. Бопее точная регулировка дпитепьиостн f производится изменением величины

К путем использования мпвдших разрядов кода модуля вектора, смежных с пер вым старшим эначаным разрядом, дпя:» управления коэффициентом пересчета делителя 13 частоты, н величиной этапонного напряжения преобразователя 14.

При изменении номера старшего энача щего разряда кода модупя соответственно сдвигаются и смежные с ним мпвдшие разряды, упрввпяюшие депитепем 13 частоты и преобрвзоватепем 16. Сдвиг. осуществляется с помощью эпемента 7 сдвига. Таким образом, с уменьшением длины вектора точность регупировки дпительности выходного напряжения сумматора 17 возрастает по двоичному закону.

Предлагаемое устройство обеспечивает более высокое быстродействие вспедствие большего постоянства скорости формирования векторов раэпичной длины.

Известное устройство позволяет испопьзовать регулирование скорости с порогами, расположенными вдоль параметра по двоичному закону» что цри pBBHosepoQ7» ном распределении длин векторов дает проигрыш в производительности 25% по сравнению с оптимвпьным регупирова.нием.

Форму-na.. изобретения

Устройство дгл отображения графичес кой информации, содержащее первый и второй преобразователи код-напряжение, соединенные с одними из входов aepsoro и второго сумматоров, соединенных с ин-. дикатором, умножитепи, подключенные к другим входам первого и второго сумматоров, последоватепьно соединенные генератор импульсов, первый счетчик и тречий преобразователь код-напряжение, отпичвющееся тем,что,с цеш ю повышения его быстродействия, 7 934539 8 оио содержит первый и второй элементы ратора импульсов, выход - к входам счетсдвига, дешифратор, делитель частоты, чиков, выходы которых соединены с дручетвертый и пятый преобразователи код- гимн входами блока элементов И-ИЛИ, напряжение, второй счетчик, третий,выход KoTopoFQ подключен к входу генесумматор и блок элементов И-ИЛИ, вы- 5 ратора импульсов, выходи третьего и ходы первого элемента сдвига, соедине- пятого преобразователей код-напряжение иы с одними из входов умножителей, Rpy- соединены с входами третьего сумматогие входы элементов сдвига соединены ра, подключенного к другим входам уммежду собой и выходом дешифратора и сожителей. одним из входов блока элементов И-ИЛИ выход второго элемента сдвига подклю- Источники информации, чен к одному из входов делителя часто- принятые во внимание при экспертизе ж и входу четвертого преобразователя 1. Патент США ¹ 3800183, коднапряжение, выход которого соединен кл. 315, опублик. 1974. с другим входом третьего преобразова- 15 2. Патент США ¹ 3500332, теля код-напряжение, другой вход дели- кл. 340-172,5, опублик. 1974 (протеЛя частоты папктачен к выходу гене- тотип), ВНИИПИ Заказ 3946/48 Тираж 472 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4